e-ISSN: 2319-8753 | p-ISSN: 2347-6710

EDIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 11, Special Issue 1, April 2022

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

### Impact Factor: 8.118

9940 572 462

6381 907 438

$\bigcirc$

International Journal of Innovative Research in Science, Engineering and TechnologyAn ISO 3297: 2007 Certified OrganizationVolume 11, Special Issue 1, April 20229th National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22)

28 <sup>th</sup> -29 <sup>th</sup> April 2022

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

### Design and Implementation of Optimizing the Energy through DVFS Techniques in 3D NoC

Mr. P. Manivannan<sup>1</sup>, P.Abinaya<sup>2</sup>, V.Kokila<sup>3</sup>, M.Monisha<sup>4</sup>

Assistant Professor, Dept. of Electronics and Communication Engineering, Adhiyamaan College of Engineering, Hosur, Tamil Nadu, India<sup>1</sup>

U.G Student, Dept. of Electronics and Communication Engineering, Adhiyamaan College of Engineering,

Hosur, Tamil Nadu, India<sup>2,3,4</sup>

**ABSTRACT**: As Networks-on-Chip (NoCs) continue to consume a large fraction of the total chip power budget, dynamic voltage and frequency scaling (DVFS) has evolved into an integral part of NoC designs.such as buffer occupation and channel utilization. The proposed methodology utilize highly predictable properties of cache-coherence communication to derive more specific and reliable NoC traffic predictions. 3D as well as network-on-chip (NoC), are two recent design approaches that promise to alleviate the consequences of interconnection degradation. This project introduces a new methodology for power efficient application mapping onto 3D NoC-based devices. Experimental results prove the efficiency of the proposed methodology since we achieve energy savings respectively. In our project we have implemented four routers in mesh connection in which all data flow is controlled by the HUB. Each Router is connected with some processing device which gives or requires the data to/from other devices.

KEYWORDS: Networks-on-Chip (NoC), Dynamic Voltage and Frequency scaling, Latency, 3D NoC, HUB.

#### I. INTRODUCTION

The steady increase in core counts coupled with power viscosity limitations and the breakdown of Dennard spanning demand NoC that give a scalable communication fabric for connecting a large number of coffers within a chip. With the increase in the number of cores, the underpinning communication fabric called the Network-on-Chip (NoC) has come critical for data communication between the cores and the memory scale. The immense number of transistors that are packed onto multicore chips as transistor point size continues to shrink into the sub-nanometer region has caused numerous new and unique power problems to emerge. Two critical power problems facing Network-on Chips are high static power and dynamic energy. Redundant dynamic energy is the result of storing and switching data within routers and links. NoC size increases proportionally with core count to accommodate the increased data communication demands. Dynamic Voltage and Frequence Scaling is the focus of important previous exploration and may be used to reduce dynamic energy. Therefore energy effectiveness of 3D NoC would ameliorate while labors are within the respectable friction. Also, the voltage swing reduction increases the needed time to transmit the packet. By exploiting the benefit of low quiescence of 3D NoC armature and employing this scaling system in the architecture would compensate the quiescence and also the performance declination of the network.

## International Journal of Innovative Research in Science, Engineering and Technology<br/>An ISO 3297: 2007 Certified OrganizationVolume 11, Special Issue 1, April 20229th National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22)

#### 28 <sup>th</sup> -29 <sup>th</sup> April 2022

#### Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

#### II. RELATED WORK

#### 1. Energy Optimization in 3D NoC through DVS Technique

As NoC's demand high power budget on the chip,DVS approaches can be applied in NoC to achieve efficient power and thermal management. DVS approaches can be applied in NoC resources to achieve energy efficiency and temperature reduction in 3D architecture. The proposed link and router architectures are respectively depicted. As some parts of the applications possess error resiliency nature, the supply voltage of the link and the routers can be reconfigured to the lower level when the approximable packet data would be mapped.

#### 2. Optimizing 3D NoC Design for Energy Efficiency A machine Learning Approach

GPU NoCs are usually implemented as two separate networks to avoid protocol deadlock. Request messages are sent from many shader cores to a few memory controllers in the request network. To evaluate the performance of different NoCs, we use a cycle-accurate NoC simulator that can simulate any regular or irregular 3D architecture. Our system consists of 64 cores and 64 network routers equally partitioned in four layers.

#### 3. Designing Scalable Hybrid Wireless NoC for GPGPUs

A robust design optimization methodology to improve the energy efficiency of 3D NoC architectures by combining the benefits of SW networks and machine learning techniques to intelligently explore the design space. The overlaid wireless network is implemented as 2x4 mesh. We choose mesh topology for wireless network because it has low design complexity and simple routing algorithms.

#### III. METHODOLOGY

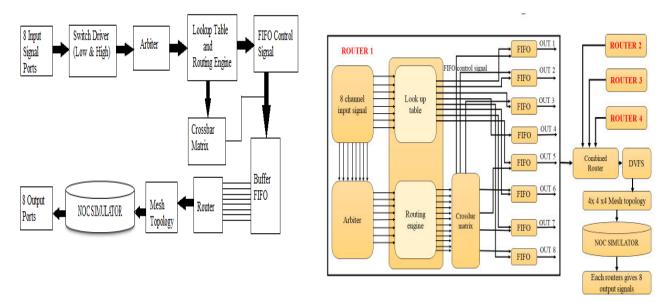

The input port models are built on a simple voltage regulator scheme that allows per router DVFS and the selection of four different voltage levels. For 8 Input 8 output architecture of Asynchronous NoC router is as shown.

The Router has four modules:

- 1. Input Arbiter

- 2. Routing Engine and Look up Table: Routing engine provides control signals to

- mux in crossbar matrix

- 3.4x4 crossbars Matrix

- 4. Circular FIFO Buffer

Each router is combined based on 3D mesh topology then each router gives 8 port output signals.

International Journal of Innovative Research in Science, Engineering and TechnologyAn ISO 3297: 2007 Certified OrganizationVolume 11, Special Issue 1, April 20229th National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22)

28 <sup>th</sup> -29 <sup>th</sup> April 2022 Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

#### Figure 1: Block Diagram

#### Figure 2: Architecture Design of 3D NoC

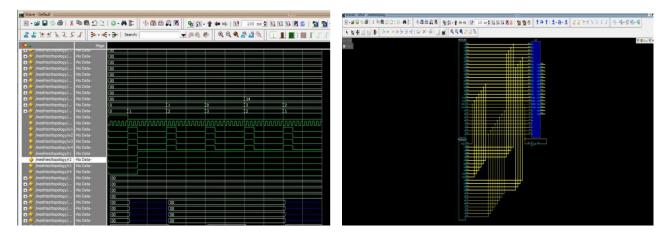

#### IV. EXPERIMENTAL RESULTS

Optimizng the energy through dynamic voltage and frequency scaling techniques in 3D NoC was successfully designed and implemented. The output screenshots is given below.

Figure 3: Simulation of Switch

Figure 4: Simulation View of Mesh Topology

International Journal of Innovative Research in Science, Engineering and TechnologyAn ISO 3297: 2007 Certified OrganizationVolume 11, Special Issue 1, April 20229th National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22)

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

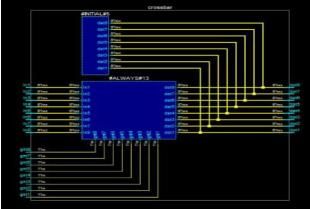

Figure 5: Inside View of Arbiter

Figure 6: Inside View of Crossbar

#### **V. CONCLUSION**

Three-dimensional 8 x 8 Asynchronous Mesh NOC Architecture Router. In our proposed router design, we implemented mesh topology with 4 routers. All the 4 Routers are connected to the Hub, which is responsible for creating connections between routers depending upon the source and destination address. The supply voltage of the links and the routers of NoC are scaled to reduce the power consumption and thermal dissipation in 3D NoC which account as a major challenges in 3D NoC architectures. Thus, the energy efficiency of 3D NoC is significantly improved due to employing DVFS technique by trading off accuracy within an acceptable variance. Also, applying the scaling method in 3D architecture would compensate the latency increase and the performance degradation of the network.

#### REFERENCES

- [1] Poovendran R, Sumathi S (2019) An area-efficient low-power SCM topology for high performance network-on Chip (NoC) architecture using an optimized routing design. Concurrency Comput Pract Experience 31(14)

- [2] Poovendran R, Sumathi S. An area-efficient FPGA implementation of network-on-chip (NoC) router architecture for optimized multicore-SoC communication [J]. Sensor Lett, 2018, 16(7): 552-560

- [3] Y. Chen, M. F. Reza, and A. Louri, "DEC-NOC: An Approximate Framework Based on Dynamic Error Control with Applications to Energy-Efficient NoCs, 2018.

- [4] M. Momeni , H.S. Shahhosein, "Energy Optimization in 3D Networks-on-Chip through Dynamic Voltage Scaling technique "

- [5] Poovendran R., Muniraj S., Nandakumar A. On Chip Implementation of Packet Switched Network. IOSR Journal of Electronics and Communication Engineering (IOSR-JECE), 2014, vol. 9, is. 2, pp. 38–42.

- [6] H. Zhao, et al., "Designing Scalable Hybrid Wireless NoC for GPGPUs," IEEE Computer Society Symposium on VLSI, pp. 703-708, 2018.

- [7] H. Jamali-Rad et al., "A new adaptive power optimization scheme for target tracking Wireless Sensor Networks".

- [8] U. Y. Ogras, R. Marculescu" It's a Small World After All": NoC Performance Optimization via Long-Range Link Insertion.

- [9] M. Momeni , H.S. Shahhosein" Energy Optimization in 3D Networks-on-Chip through Dynamic Voltage Scaling technique ".

- [10] Sourav Das, Janardhan Rao Doppa," Optimizing 3D NoC Design for Energy Efficiency A machine Learning Approach".

International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 9<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22) 28<sup>th</sup> -29<sup>th</sup> April 2022

#### 8 - - 29 - April 202

#### **Organized by**

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

#### BIOGRAPHY

Mr. P. Manivannan, Assistant Professor, Electronics and Communication Engineering Department, Adhiyamaan College of Engineering, Anna University.

Abinaya P, Electronics and Communication Engineering Department, Adhiyamaan College of Engineering, Anna University.

Kokila V, Electronics and Communication Engineering Department, Adhiyamaan College of Engineering, Anna University.

Monisha M, Electronics and Communication Engineering Department, Adhiyamaan College of Engineering, Anna University.

Impact Factor: 8.118

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com