e-ISSN: 2319-8753 | p-ISSN: 2347-6710

EDIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 13, Issue 4, April 2024

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

### Impact Factor: 8.423

9940 572 462 🔊

6381 907 438

International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET)

| e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

|| Volume 13, Issue 4, April 2024 ||

| DOI:10.15680/IJIRSET.2024.1304432 |

## Low Power High Accuracy Approximate Multiplier Using High Order Compressors

Smt.V.Rohini<sup>1</sup>, K.Snigdha<sup>2</sup>, V.Harsha Vardhan<sup>3</sup>, M.Akhil Kumar Reddy<sup>4</sup>, T.Sukumar<sup>5</sup>

Assistant Professor, Department of E.C.E, N.B.K.R. Institute of Science and Technology, Tirupati,

Andhra Pradesh, India<sup>1</sup>

UG Student, Department of E.C.E, N.B.K.R. Institute of Science and Technology, Tirupati, Andhra Pradesh, India<sup>2345</sup>

**ABSTRACT:** To reduce the power consumption, the design of approximate multiplier appears as a promising solution formally error-resilient applications. In this paper, we propose alow-power high accuracy approximate 8 x 8 multiplier design. The proposed design has two main features. First, according to the significance, different weights utilize different compressors (in different levels of accuracy) to accumulate their product terms. As a result, the power consumption can be saved with as small error. Second, for the middle significance weights, we use high order approximate compressors (e.g., 8:2 compressor) to reduce the logic of carry chains. To our knowledge, the proposed design is the first work that successfully uses high-order approximate compressors in the approximate multiplier design. Compared with an exact multiplier (Dadda tree multiplier), experimental results show that the proposed approximate multiplier can achieve bothlow power and high accuracy.

**KEYWORDS:** -approximate computing; arithmetic circuits; logic design ;low-power design ;partial product reduction.

#### I. INTRODUCTION

Nowadays, the demand for low power, high performance portable devices has been greatly increased. The growingmarket of portable electronic systems demands microelectronics circuits design with low power dissipation. Multipliers play an important role in today's digital signal processing and various other applications.

With advances in technology, many researchers have tried and are trying to design multiplierswhich offer high speed, low power consumption and hence less area or even combination of them in one multiplier thus making them suitable for various high speed, low power VLSI implementationnetwork overloading byintelligent circuit modifications [8]. EPTL flip flops are contention free and are expected to operate at wide range of operating voltages. You et.al, recently proposed a contentionfree low power EPTL flip flop that is completely void of anyredundant pre- charge and discharge operations which cansave 80 % power consumption when compared to conventional TGFF under 10 % data activity [11]. The present manuscript analyzes the power consumption features of the EPTL D flipflop using 18nm technological node. The analysis at 18nm technological node attests to the small circuit layout of the flipflop that is compatible with present lithographical tools yielding reliable devices for nominaloperation.

#### **II. LITERATURE SURVEY**

Approximate Compressor for Error-Resilient Multiplier Design", Approximate circuit design is an innovative paradigm for error-resilient image and signal processing applications. Multiplication is often a fundamental function for many of these applications. In this paper, three approximate compressors are proposed with an accuracy constraint for the partial product reduction (PPR) in a multiplier. Both approximation and truncation are considered in the approximate multiplier design. An image sharpening algorithm is then investigated as an application of the proposed multiplier designs. Extensive simulation results show that the proposed designs achieve significant reductions in area and power while achieving a high signal-to-noise ratio (SNR > 35 dB), compared to their exact counterparts as well as other approximate multipliers.

International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET)

| e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

|| Volume 13, Issue 4, April 2024 ||

| DOI:10.15680/IJIRSET.2024.1304432 |

#### **III. PROPOSED SYSTEM**

Multipliers are important components that dictate the overall arithmetic circuits' performance. The most critical components of multipliers are compressors.

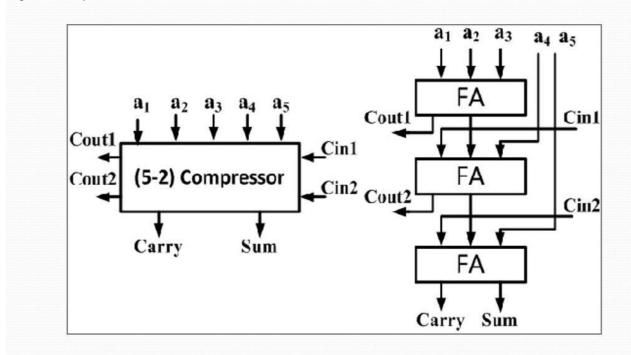

A new 5:2 compressor architecture based on changing some internal equations is proposed. In addition, using an efficient full-adder (FA) block is considered to have a high-speed compressor.

The proposed architecture is compared with the best existing designs presented in the state-of the-art literature in terms of power, delay and area.

#### IV. ADVANTAGES OF PROPOSED SYSTEM

- Re-silent errors are reduced.

- Power consumption reduced.

- Delay is reduced

#### V. DEVELOPMENT PROCESS

- Frontend Development Tools: While the project is focused on backend development, itrequires programming...

- XILINX ISE 14.5v.

- Verilog code is used.

#### VI. RESULT AND DISCUSSION

- Approximate computing can decrease the design complexity with an increase inperformance and power efficiency for error resilient applications.

- Data compression has a major role in multimedia and image processing applications to encode the information in a compact size. In those applications, reducing area, power anddelay are the most important requirements.

- In this paper two new 5:2 exact compressor are designed to analyse the booth multiplier based on area, power consumption, delay with error distance.

#### IJIRSET©2024

International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET)

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

|| Volume 13, Issue 4, April 2024 ||

| DOI:10.15680/IJIRSET.2024.1304432 |

#### VII. CONCLUSION

Utilizing a 5:2 Multiplier instead of a 4:2 Multiplier minimizes both the power consumption and the overall delay and also the accuracy will be increased.

#### REFERENCES

- 1. V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approximate adders," IEEE Trans. Compute.- Aided Design Integer. Circuits Syst., vol. 32,no. 1, pp. 124–137, Jan. 2013.

- 2. E. J. King and E. E. Swartzlander, Jr., "Data-dependent truncation scheme for parallel multipliers," in Proc. 31st Asilomar Conf. Signals, Circuits Syst., Nov. 1998, pp. 1178–1182.

- 3. K.-J. Cho, K.-C. Lee, J.-G. Chung, and K. K. Parhi, "Design low-error fixed-width modified booth multiplier," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 12, no. 5, pp. 522–531, May2004.

- H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 850–862, Apr. 2010.

- 5. Z. Yang, J. Han, and F. Lombardi, "Approximate Compressor for Error Resilient MultiplierDesign", Proc. of IEEE International Symposiumon Defect and Fault Tolerance in VLSI and Nano technology Systems, 2015.

- 6. A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Design and Analysis of Approximate Compressors for Multiplication", IEEE Trans.on Computers, vol.64, no.4, pp.984-994, 2015.

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com