e-ISSN: 2319-8753 | p-ISSN: 2320-6710

EDIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

808

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 10, Issue 1, January 2021

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

### Impact Factor: 7.512

9940 572 462

6381 907 438

$\bigcirc$

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

|| Volume 10, Issue 1, January 2021 ||

DOI:10.15680/IJIRSET.2021.1001013

## **Implementation of Low Power Vedic Multiplier Using Reversible Logic Gates**

K. Madhuri<sup>1</sup>, B. Siva Prasad<sup>2</sup>, K. Pradeep<sup>3</sup>

.M. Tech Scholar, Dept. of ECE, BITS, VIZAG, Visakhapatnam, Andhra Pradesh, India<sup>1</sup>

Associate Professor, Dept. of ECE, BITS, VIZAG, Visakhapatnam, Andhra Pradesh, India<sup>2</sup>

. Research Scholar, CUTM, Andhra Pradesh, India<sup>3</sup>

**ABSTRACT:** Reversible logic is one of innovative technology in present days due to power consumption is drastically reduced. In the digital circuits amount of energy is dissipated as the bits of information are lost during logical operations and loss of information can be reduced by using reversible logic gates. Multiplication plays important role in the dsp processors Reversible computation is an emerging area of research, having applications in numerous fields. In this paper a reversible Vedic multiplier is designed and compared with booth multiplier. The design is based on Vedic method of multiplication. In booth multiplier 41.7 nsec delay and power 2,23mw is obtained, Vedic multiplier the delay has reduced to 24.7nsecand power 1.3 mw . from the obtained results, it is clear that the UT reversible Vedic multiplier can perform better than the existed booth multiplier. And it is implemented by using Xilinx software using Verilog.

KEYWORDS: Reversible logic. Vedic multiplier, Urdhva Tiryakbhyam

#### I. INTRODUCTION

Energy dissipation is of fundamental in the design and implementation of VLSI circuits [1]. As the number of circuits integrated on a chip increases and the chip size decreases, energy dissipation thus becomes the greater area of important for designers. Conventional digital circuits dissipate an important amount of energy owing to loss of information. According to Landauer's research, the amount of energy dissipated for every irreversible bit operation is at least KTln2 joules, where K is the Boltzmann's constant and T is the temperature at which operation is performed [1]. Vedic mathematics is the ancient Indian system of mathematics which mainly deals with Vedic mathematical formulae and their application to various branches of Mathematics. Vedic mathematics was reconstructed from the ancient Indian scriptures (Vedas) by Sri Bharati Krishna Tirtha after his research on Vedas. He constructed 16 sutras and 16 upa sutras after extensive research in Atharva Veda. The most famous among these 16 are Nikhilam Sutram, Urdhva Tiryakbhyam, and Anurupye. It has been found that Urdhva Tiryakbhyam is the most efficient among these. The beauty of Vedic mathematics lies in the fact that it reduces otherwise cumbersome looking calculations in conventional mathematics to very simple ones. This is so because the Vedic formulae are claimed to be based on the natural principles on which the human mind works.

Digital signal processing (DSP) is the technology that is Omni present in almost every engineering discipline[3]. Faster additions and multiplications are the order of the day. Multiplication is the most basic and frequently used operations in a CPU. Multiplication operations also form the basis for other complex operations such as convolution, Discrete Fourier Transform, Fast Fourier Trans forms, etc. Hence Vedic mathematics can be apply employed here to perform multiplication. Reversible logic is one of the promising fields for future low power design technologies. Since one of the requirements of all DSP processors and other hand-held devices is to minimize power dissipation multipliers with high speed and lower dissipations are critical. This paper proposes an implementation of Reversible Urdhva Tiryakbhyam Multiplier which consists of two cardinal features. One is the fast multiplication feature derived from Vedic algorithm Urdhva Tiryakbhyam and another is the reduced heat dissipation by the virtue of implementing the circuit using reversible logic gates.[4]

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

|| Volume 10, Issue 1, January 2021 ||

DOI:10.15680/IJIRSET.2021.1001013

#### **II. REVERSIBLE LOGIC GATES**

Reversible Gates are circuits in which number of outputs is equal to the number of inputs and there is a one to one correspondence between the vector of inputs and outputs [8-10]. It not only helps us to determine the outputs from the inputs but also helps us to uniquely recover the inputs from the outputs. There are many numbers of reversible logic gates that exist at present. The quantum cost of each reversible logic gate is an important optimization parameter. The quantum cost of a 1x1 reversible gate is assumed to be zero while the quantum cost of a 2x2 reversible logic gate is taken as unity.

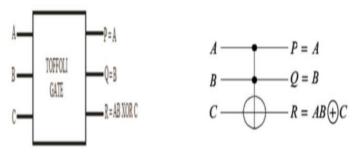

#### **2.1TOFFOLI GATE:**

TOFFOLI gate which is a 3\*3 gate with inputs (A, B, C) and outputs P=A, Q=B, R=AB XOR C. It has Quantum cost is five.

FIG1toffoli Gate and Its Symbolic Representation

#### 2.2 Feynman Gate:

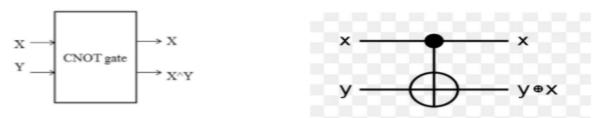

It is a 2\*2 Feynman gate. Quantum cost of a Feynman gate is 1 and is called as Controlled NOT gate or CNOT gate. It is identical to single control input Toffoli gate.

Fig 2: Feynman Gate and Its Symbolic Representation

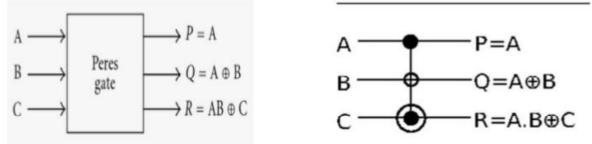

#### 2.3 Peres Gate:

It is a 3\*3 Peres gate. The vector input is I(A, B, C) and the vector output is O(P,Q,R). The outputs are defined by P=A, Q=A XOR B, R=AB XOR C. Quantum cost of a Peres gate is 4. It needs two Toffoli gates for its construction

FIG 3:Peres Gate and Its Symbolic Representation

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

|| Volume 10, Issue 1, January 2021 ||

DOI:10.15680/IJIRSET.2021.1001013

#### 2.4 CNOT Gate:

CNOT gate is also known as controlled-not gate. It is a 2\*2 reversible gate. The CNOT gate can be described as the input vector is I(X, Y) and the output vector is O(P,Q). The outputs are defined by P=X, Q=X XOR Y. Quantum cost of CNOT gate is 1.

Fig:4 Cnot Gate and Its Symbolic Representation

#### **III. VEDIC MULTIPLIER**

Vedic Mathematics is much simple and easy to understand. It also improves the speed of calculation. The word 'Vedic' is obtained from word "Veda" and its meaning is "store house of all knowledge". The Vedic multiplier has applications in microprocessors, filtering, Fourier transform, communication and Digital Signal Processing. Ancient Vedic mathematics consists of 16 Sutras that are related to different branches of mathematics like algebra, arithmetic and geometry. Vedic Multiplier mainly used "Urdhva Tiryagbhyam" (Vertically and Crosswise) which is used for both binary and decimal multiplication. This technique consists of generation of partial products and then performs addition simultaneously. This method can be used for 2x2, 4x4.....NxN bit multiplication.

#### **IV. REVERSIBLE VEDIC MULTIPLIER**

Vedic multiplication is divided into sixteen sutras. Urdhva Triyakbhyam is one such multiplication algorithm which is well known for its efficiency in reducing the calculations involved. The algorithm uses vertically and crosswise multiplication. As the partial products and their sum are calculated parallelly algorithm is independent of clock frequency of the processor. Hence, it is well adapted to parallel processing. This in turn reduces delay, which is the primary aim behind this work. The main advantage of Urdhva Triyakbhyam algorithm is to design a low power multiplier.

#### V. URDHVA TIRYAKBHYAM

UrdhvaTiryakbhyam is the general formula applicable for all cases of multiplication and also in the division of a large number by another large number [6]. It means vertically and crosswise where we multiply the numbers by places that is unit place multiply by unit place gives the unit place while tens place multiply by unit's place give the ten place and so on.

| Step 1                                 | Step 2                                 | Step 3                                 |

|----------------------------------------|----------------------------------------|----------------------------------------|

|                                        | ::::X                                  | · · · · · · · · · · · ·                |

| · · · · · · · •                        | · · · · · · · · ·                      | · · · · · · ·                          |

| Step 4                                 | Situage S                              | Step 6                                 |

| ···· ×                                 |                                        | ·····                                  |

| · · · · · · · ·                        |                                        |                                        |

|                                        | Numps II                               | 51ep 5                                 |

| · ···································· | · ···································· | · ···································· |

|                                        |                                        |                                        |

| Step 10                                | 51mp 11                                | Step 12                                |

|                                        |                                        | · · · · · · · · · · · · · · · · · · ·  |

| *                                      | ×                                      | A                                      |

| Step 13                                | Stage 1.4                              | Step 15                                |

|                                        |                                        | + · · · · · · ·                        |

| Ж:::::                                 | X                                      | +                                      |

Fig 5 Urdhva Triyakbhyam Algorithm

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

|| Volume 10, Issue 1, January 2021 ||

#### DOI:10.15680/IJIRSET.2021.1001013

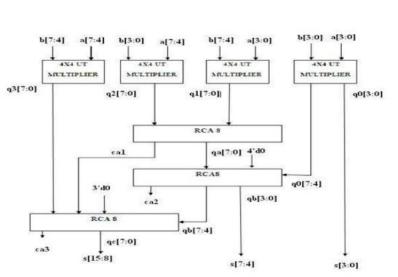

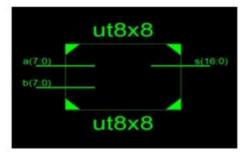

Fig 6 Reversible 8\*8 Vedic Multiplier

#### VI. SIMULATION RESULTS

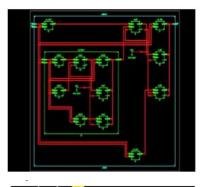

**RTL Schematic:**

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

|| Volume 10, Issue 1, January 2021 ||

#### DOI:10.15680/IJIRSET.2021.1001013

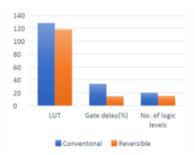

Table :1 comparison with different parameters

| PARAMETERS            | CONVENTIONAL<br>MULTIPLIER (BOOTH<br>MULTIPLIER) | VEDIC MULTIPLIER |

|-----------------------|--------------------------------------------------|------------------|

| Gate Delay(Logic      | 2.361ns (33.6%)                                  | 1.262ns (14.5%)  |

| Look Up Tables        | 128                                              | 118              |

| Number Of Logic Level | 20                                               | 15               |

| Power                 | 2.2mW                                            | 1.3mW            |

#### VII. CONCLUSION

Multiplication plays important role in the processors. Reversible computation is an emerging area of research, having applications in numerous fields. In this paper a reversible Vedic multiplier is proposed using Urdhva Tiryakbhyam sutra. In this paper, an 8\*8 UT Reversible Vedic multiplier is designed and compared with 8\*8 Conventional Vedic multiplier by using Xilinx software. The design is based on Vedic method of multiplication. In Conventional Vedic multiplier 2.361nsec gate delay is obtained, whereas in UT Reversible Vedic multiplier the gate delay has reduced to 1.262nsec. So, from the obtained results, it is clear that the UT Reversible Vedic multiplier can perform better than the existing Conventional Vedic multiplier.

#### REFERENCES

[1]VijayaLakshmi "Performance Analysis For Vedic Multiplier Using Modified Full Adders" International Conference on Innovations in Power and Advanced Computing Technologies (iPACT) IEEE (2017).

[2]G. Challa Ram, D. Sudha Rani, Y. RamaLakshmanna, K.Bala Sindhuri "Area Efficient Modified Vedic Multiplier" 2016 International Conference On Circuit, Power And Computing Technologies, IEEE (March 2016).

[3]Paras Gulati,Harsh Yadav, Manoj Kumar Taleja "Implementation of an efficient Multiplier Using the Vedic Multiplication Algorithm" 2016 International Conference on Computing, Communication and Automation (ICCCA) IEEE (2016).

[4]M. Akila, C. Gowribala, S. Maflin Shaby "Implementation of High Speed Vedic Multiplier using Modified Adder' 2016 International Conference on Communication and Signal Processing, IEEE(April 2016).

[5]Josmin Thomas, R. Pushpangadan, Jinesh S "Comparative Study of Performance Vedic Multiplier on the Basis of Adders Used" 2015 International WIF Conference on Electrical and Computer Engineering (WIECON-ECE) IEEE (December 2015).

[6]Saji. M. Antony, S.Sri Ranjani Prashanthi, Dr. S. Indu, Dr. Rajeswari Pandey "Design of High Speed Vedic Multiplier Using Multiplexer Based Adder", 2015 International Conference on Control, Communication & Computing India(ICCC) IEEE(November 2015).

[7]Kokila Bharathi Jaiswal, Nithish Kumar, Pavithra Seshadri, Lakshminarayana G. "Low Power Wallace Tree Multiplier Using Modified Full Adder", 2015 3rd Interntional Conference on Signal Processing, Communication and Networking(ICSCN) IEEE(2015).

[8]Bhavani Prasad. Y, Ganesh Chokkakula, Srikanth Reddy.P, Samhitha.N.R "Design of Low Power and High Speed Modified Carry Select Adder for 16 bit Vedic Multiplier" 2014 (ICICES) IEEE (2014).

[9]Manoranjan Pradhan, Rutuparna Panda, Sushant Kumar Sahu "Speed Comparsion of 16\*16 Vedic multiplier", International Journal of Computer Applications, Vol.21, No.6, IEEE(May 2011).

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

|| Volume 10, Issue 1, January 2021 ||

DOI:10.15680/IJIRSET.2021.1001013

[10]Sreehari Veeramachaneni, Kirthi M Krishna, Lingamneni Avinash, Sreekanth Reddy Puppala, M.B. Srinivas "Novel Architectures For High Speed and Low Power 3-2,4-2, and 5-2 Compressors" 20th International Conference on VLSI Design IEEE (Jan 2007).

[12].Swami Bharati Krsna Tirtha, Vedic Mathematics. Delhi: Motilal Banarsidass publishers 1965 2. Vedic Mathematics: http://www.hinduism.co.za/vedic.html.

[13] R. Landauer," Irreversibility and Heat Generation in the Computational Process", IBM Journal

[14.]Research and Development, 5, pp.183-191, 1961.

[15.].C.H. Bennett, "Logical reversibility of Computation", IBM J. Research and Development, pp.525 532, November 1973.

[16]. R. Feynman, "Quantum Mechanical Computers," Optics News, Vol.11, pp. 11–20, 1985. Peres, Reversible logic and quantum computers, Phys. Rev. A 32 (1985) 3266–3276.

[17]. E. Fredkin and T. Toffoli,"Conservative Logic", Int" J. Theoretical Physics Vol 21, pp.219-253, 1982.

[18] G Ganesh Kumarand V Charishma, Design of high speed vedic multiplier using vedic mathematics techniques, Itn''l J. of Scientific and Research Publications, Vol. 2 Issue 3 March 2012

The J. of Scientific and Research Fublications, vol. 2 issue 5 Watch 2012

Impact Factor: 7.512

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com