e-ISSN: 2319-8753 | p-ISSN: 2347-6710

DIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 13, Issue 5, May 2024

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

# Impact Factor: 8.423

9940 572 462

6381 907 438

🖂 ijirset@gmail.com

入 う え IJIRSET

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 || | DOI:10.15680/IJIRSET.2024.1305245 |

# **Review on Reversible Radix-2 DIT and DIF Fast Fourier Transforms**

<sup>1</sup>Abhay Kumar Ranjan, <sup>2</sup>Ompal Singh, <sup>3</sup>Sandip Nemade

M. Tech. Scholar, Department of ECE, TIT, Bhopal, India<sup>1</sup> Professor, Department of ECE, TIT, Bhopal, India<sup>2</sup> Professor & HOD, Department of ECE, TIT, Bhopal, India<sup>3</sup>

**ABSTRACT**: Fast Fourier transform (FFT) is utilized to minimize the complexity of discrete Fourier transform by converting signals from time domain to frequency domain and conversely. Digital signal processing systems like image processing, general filtering, sonar, spread spectrum communications, and convolutions use this FFT operations. Radix-2(R-2) decimation in frequency method is designed to execute an efficient FFT architecture. This work mainly focuses on the optimization of FFT architectures for VLSI Implementation. The optimization of FFT designs in this work mainly categorized into two major parts. One is optimization of pipelined FFT designs at the architecture level and the other one is subcomponent minimization. In this paper the study of decimation in time and decimation of frequency fast fourier transform and reversible gate.

KEYWORDS: FFT, Decimation in Time, Decimation in Frequency, Reversible Gate

# I. INTRODUCTION

In recent years, many advanced communication systems including digital audio broadcasting [1], digital video broadcasting [2], wireless networks [3], highspeed subscriber line systems [4] etc. require a core VLSI hardware for efficient and real-time signal processing algorithms. A number of important VLSI architectures have been designed to meet the challenge of high throughput and low latency with optimized area utilization and low power consumption. Therefore, over the past three decades design of efficient VLSI hardware architecture for signal processing algorithms has been considered as the major research focus, as reported in published literature.

In this paper, Fast Fourier Transform algorithm [5], a powerful tool in the field of signal processing, has been implemented through VLSI architectural transformation technique. Along with FFT, an intensive study and implementation of Discrete Hilbert Transform [6] and Fast Hartley Transform [7] has been performed on the reconfigurable platform. The FFT has wide applications in the field of modern digital communication system and television terrestrial broadcasting system [8], such as the XDLS (de)modulator, phase correlation system [9], mobile receiver [10] etc. For these applications, a vast number of dedicated FFT processors have been developed with several architectural transformation techniques. The pipeline based architecture of FFT processor [11] has been used in many applications with high throughput advantage. However, in case of real-time embedded system applications, a long pipeline based FFT processor consumes too large a silicon area to implement. Thus, shared memory based FFT processors are more suitable for embedded applications [12]. However, power hungry circuit of shared memory based FFT processor leads to the design of SA architecture based FFT processor.

# II. LITERATURE REVIEW

**Syeda Farhat Sultana et al. [1],** FFT models are planned utilizing the collapsing change and the register minimization strategies. Parallel pipelined structures are determined intricate and genuine esteemed quick Fourier change. The working recurrence of the proposed CFFT design is diminished which diminished the force. Notwithstanding that, the new equal pipelined models RFFT are introduced. The force utilization is decreased up to 37% and half in 2-equal structures separately. Further, the yield tests are gotten in a mixed request.

**Navin Nadar et al.** [2], have thought about the association of a unique reason processor for on-line. Gold and determined the FFT by progressive information clusters. Notwithstanding portrayal of blended calculations are inferred utilizing the above strategy. The portrayed a basic method to control the FFT equipment. The strategy created the lists both for contributions of each butterfly activity and for the appropriate fidget factor. Notwithstanding that, this

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| <u>www.ijirset.com</u> | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

# | DOI:10.15680/IJIRSET.2024.1305245 |

technique permits equal association of the memory with the end goal information sources and yields have a place with various memory units, henceforth can generally got to in equal.

**Shashidhara. K. S et al. [3],** the requirement for fast remote correspondence frameworks has gotten an most extreme need. High information rates lead to extra specialized issues since the broadband radio channel is time variation and show recurrence specific blurring due to multipath proliferation. Along these lines, the channel balance cycle of single transporter frameworks turns out to be excessively confounded. The inspiration to utilize OFDM is to decrease the computational multifaceted nature of high information rate transmission over radio channels. OFDM is a sort of multicarrier transmission, and wherein the radio channel is separated into numerous narrowband subcarriers or sub-channels. The sub-channels are in this manner recurrence non-specific to disentangle the adjustment cycle at the beneficiary. In OFDM framework a solitary information stream is sent over many low rate subcarriers to accomplish equal information transmission. This idea of equal information transmission and FDM was created during the 1960s. In the conventional equal information transmission framework, the absolute recurrence band is partitioned into N non covering sub-channels. Each sub-channel is regulated with a different image, and afterward the N sub-channels are recurrence multiplexed.

**Fahad Qureshi et al. [4],** have introduced MSR-CORDIC calculation and it's engineering. In MSR-CORDIC calculation miniature turn and scaling tasks are consolidated. The first calculation disposes of target turn point stockpiling. The subsequent calculation. It inferred the advanced arrangement of miniature pivots for the execution of fixed point vector pivot. Further, equipment pre-moving plan is proposed to decrease the barrel shifter unpredictability. These calculations altered the rudimentary pivot conditions. The scale factor is considered as a vital intensity of two. Some cycle was rehashed to expand the ROC. He proposed a scale factor improvement strategy for both exaggerated and roundabout facilitate framework. In this strategy indispensable intensity of two. The scaling activity in the tweet Z change is executed by standardization calculation. The ideal frequencies of CZT are indicated before calculation. Because of this, the aggregate numbers of CORDIC cycles are diminished.

**Guilherme Ferreira et al. [5],** proposed offbeat exhibit engineering HT. The sans scaling adjusted CORDIC unit is utilized as a fundamental PE. The engineering was reached out to perform round and elliptic HT. In expansion to that these models dispense with the prerequisites of pre-calculations. The point parallelization technique diminished the calculation by 25%. He built up programming characterized. Works in both coordinated and offbeat mode. Clock recurrence chosen the dormancy of the coordinated plan. The CORDIC calculation follows the repetitive parallel number framework and the scale factor is consistent. The calculation proposed in requires both sans scaling CORDIC cycles and ordinary CORDIC cycles and furthermore it builds the circuit unpredictability on account of radix-4 corner encoding. He proposed the CORDIC calculation that totally eliminates the scaling factor.

**S.** Aseeri et al. [6], depicted bound together exhibit design utilizing changed CORDIC as the fundamental butterfly PE. These four changes are processed by basic re-plan of information tests. Falling the little change engineering can be stretched out to longer length change. Hence these models are appropriate for WSI. In this calculation, the ROC is improved by area collapsing technique and reparation of some cycle steps. This calculation requires consistent scale factor increase and extra territory for sign/area discovery hardware. Scale factor rectification technique is proposed with one extra clock cycle to play out the estimation contrasted and the ordinary CORDIC calculation. In this calculation, the ROC is expanded utilizing the third-request of Taylor arrangement guess. Calculation in turn mode for exaggerated facilitate. The quantity of microrotation tasks is decreased utilizing the main 1 digit location procedure.

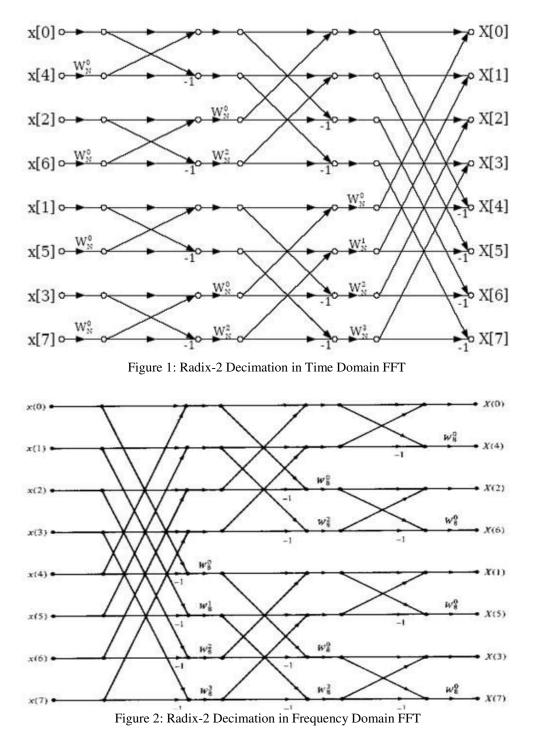

# III. FFT ALGORITHM

A FFT is a calculation to process the discrete Fourier change (DFT) and its reverse. Fourier investigation changes over time (or space) to recurrence and the other way around; a FFT quickly registers such changes by factorizing the DFT framework into a result of scanty (for the most part zero) factors. Subsequently, quick Fourier changes are broadly utilized for some applications in building, science, and arithmetic. Demonstrate the butterfly tasks for radix-2 DIF FFT in figure 1 and figure 2. The radix-2 calculations are the most straightforward FFT butterfly calculation.

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

| DOI:10.15680/IJIRSET.2024.1305245 |

#### Radix-2

Troublesome to recognize from one another, for this situation the zone based methodology will be calm valuable. Standardized cross connection [13] is a broadly utilized methodology in the territory based technique. Consolidating the stage relationship strategy with methodology was pro acted like an advancement territory based technique interpretation, scale and revolution. Utilized a likelihood thickness inclination based interest direct indicator toward remove the steady point highlights.

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

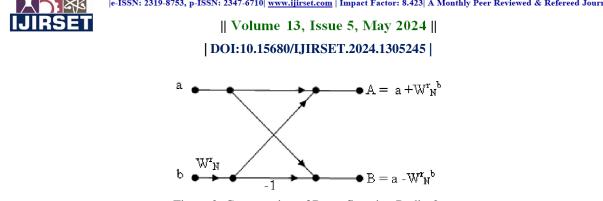

Figure 3: Computation of Butterfly using Radix-2

They proposed worldwide parallax histogram based channel to dispose of the anomaly actuated by old style connection strategy. They strategy that utilizations bootstrap resampling to gauge the vulnerability of territory put together picture enlistment calculation with respect to a specific pair of pictures. He proposed a strategy for programmed enlistment. In this, they first applied Harris administrator to remove the corner highlights after that canny administrator is executed to identify the picture edges. The relationship be tween's the picture sets yields the corner focuses. The relative change between the picture pair is set up, which figures the boundaries, as per that the pictures are enlisted.

## **IV. METHODOLOGY**

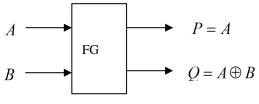

Several reversible gates have come out in the recent years. The most basic reversible gate is the Feynman gate and is the only 2x2 reversible gate available. It is most commonly used for fan out purposes. The 3x3 reversible gates include Toffoli gate, Fredkin gate, new gate and Peres gate, all of which can be used to realize the various Boolean functions in various logical architectures.

#### **BASIC REVERSIBLE GATES** 0

Several reversible logic gates are used in previous design. In figure 4, show the block diagram of two input (A, B) and two output (P, Q) Feynman gate.

Figure 4: Feynman gate

In figure 5, the block diagram of the three inputs (A, B, C) and three output (P, Q, R) Fredkin gate.

Figure 5: Fredkin gate

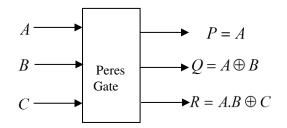

Figure 6 shows the Peres gate. A portion of the 4x4 doors are intended for executing some imperative combinational capacities notwithstanding the fundamental capacities. The vast majority of the aforementioned entryways can be utilized as a part of the outline of reversible adders.

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| <u>www.ijirset.com</u> | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

| DOI:10.15680/IJIRSET.2024.1305245 |

Figure 6: Peres gate

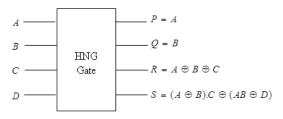

The HNG gate, presented in fig, produces the following logical output calculations:

$$P = A$$

(1)

$$Q = B$$

(2)

$$R = A \oplus B \oplus C$$

(3)

$$S = (A \oplus B) \cdot C \oplus (AB \oplus D)$$

(4)

The quantum cost and delay of the HNG is 6. At the point when D = 0, the consistent estimations created on the R and S yields are the required total and complete operations for a full snake. The quantum representation of the HNG is exhibited in Fig. 7.

Figure 7: Block Diagram of the HNG Gate

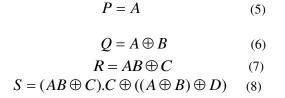

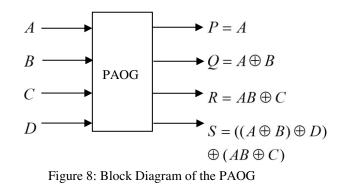

A new programmable 4x4 reversible logic structure - Peres And-Or (PAOG) gate - is presented which produces outputs

Fig. 8 shows the block diagram of the PAOG gate. This gate is an extension of the Peres gate for ALU realization.

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

# || Volume 13, Issue 5, May 2024 ||

# DOI:10.15680/IJIRSET.2024.1305245

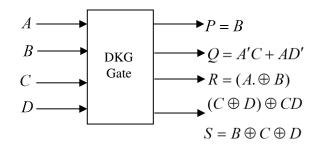

Several 4x4 gates have been described in the literature targeting low cost and delay which may be implemented in a programmable manner to produce a high number of logical calculations. The DKG gate produces the following logical output calculations:

Figure 9: DKG Gate

$$P = B (9)$$

$$Q = A'C + AD' (10)$$

$$R = (A. \oplus B)(C \oplus D) \oplus CD (11)$$

$$S = B \oplus C \oplus D (12)$$

## **V. CONCLUSION**

The prime objective is to construct a FFT in order to have low power consumption and lesser area. The parameters (i) power consumption (ii) Area occupancy were given due consideration for comparing the proposed circuit with other FFTs. The circuits were simulated using Model-Sim 6.3c and synthesized with Xilinx ISE 14.2i.

### REFERENCES

- [1] Syeda Farhat Sultana and Basavarja Patil, "Area efficient VLSI architecture for reversible radix\_2 FFT algorithm", International Conference on Emerging Smart Computing and Informatics (ESCI), IEEE 2021.

- [2] Navin Nadar, Moksha Mehta, Kaushal Bhat, Joshua Mendes and Dr. Ravindra Chaudhari, "Hardware Implementation of Pipelined FFT using Polyphase Decomposition", International Conference on Recent Trends on Electronics, Information, Communication & Technology (RTEICT), IEEE 2021.

- [3] Shashidhara. K. S and H.C. Srinivasaiah, "Low Power and Area efficient FFT architecture through decomposition technique", International Conference on Computer Communication and Informatics (ICCCI -2017), Jan. 05 – 07, 2019, Coimbatore, INDIA.

- [4] Fahad Qureshi, Jarmo Takala, Anastasia Volkova, Thibault Hilaire, "Multiplier-less Unified Architecture for Mixed Radix-2/3/4 FFTs", 2017 25th European Signal Processing Conference (EUSIPCO), IEEE 2019.

- [5] Guilherme Ferreira; Leandro M. G. Rocha; Eduardo Costa and Sergio Bampi, "Combining m=2 Multipliers and Adder Compressors for Power Efficient Radix-4 Butterfly", 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), IEEE 2019.

- [6] S. Aseeri "State-of-the-Art FFT: Algorithms Implementations and Applications" Reflections on the 2018 SIAM Conference on Parallel Processing for Scientific Computing pp. 1-3 Jun 2018.

- [7] E. Konguvel and M. Kannan "A Survey on FFT/IFFT Processors for Next Generation Telecommunication Systems" Journal of Circuits Systems and Computers vol. 27 no. 03 pp. 1830001 2018.

- [8] W. Choi Kang and J. Park "Embedded DRAM- Based Memory Customization for Low-Cost FFT Processor Design" IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2017.

- [9] Fahad Qureshi, Muazam Ali, and Jarmo Takala, "Multiplierless Reconfigurable Processing Element for Mixed Radix-2/3/4/5 FFTs", 978-1-5386-0446-5/17/\$31.00 ©2017 IEEE.

- [10] R. H. Neuenfeld M. B. Fonseca E. A. C. da Costa and J. P. Oses "Exploiting addition schemes for the improvement of optimized radix-2 and radix-4 fft butterflies" 2017 IEEE 8th Latin American Symposium on Circuits Systems (LASCAS) pp. 1-4 2017.

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

| DOI:10.15680/IJIRSET.2024.1305245 |

- [11] B. Silveira G. Paim B. Abreu M. Grellert C. M. Diniz E. A. C. da Costa et al. "Power-Efficient Sum of Absolute Differences Hardware Architecture Using Adder Compressors for Integer Motion Estimation Design" IEEE Transactions on Circuits and Systems I: Regular Papers vol. PP no. 99 pp. 1-12 2017.

- [12] M. Najem T. Bollengier J. C. Le Lann and L. Lagadec "A Cost Effective Approach for Efficient Time-Sharing of Reconfigurable Architectures" 2017 International Conference on FPGA Reconfiguration for General-Purpose Computing (FPGA4GPC) May 2017.

- [13] M. Z. A. Khan and S. Qadeer "A new variant of Radix-4 FFT" 2016 Thirteenth International Conference on Wireless and Optical Communications Networks (WOCN) pp. 1-4 2016.

- [14] C. A. Arun and P. Prakasam "A mathematical approach on various radix- 2i FFT algorithms" 2016 International Conference on Electrical Electronics and Optimization Techniques (ICEEOT) pp. 1040-1045 2016.

- [15] A. Rauf M. A. Pasha and S. Masud "A Novel split radix fast fourier transform design for an adaptive and scalable implementation" 2016 3rd International Symposium on Wireless Systems within the Conferences on Intelligent Data Acquisition and Advanced Computing Systems (IDAACS-SWS) pp. 116-121 2016.

INTERNATIONAL Standard Serial Number India

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com