An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

# Improving Voltage and Frequency of DC –DC Converter using ZCS and ZVS for Low Power and High Power Applications

Ramkumar.G<sup>1</sup>, Balaji.T<sup>2</sup>

PG Scholar, Paavai College of Engineering, Namakkal-637018, TN, India<sup>1</sup> Asst professor, Dept. of EEE, Paavai College of Engineering, Namakkal-637018, TN, India<sup>2</sup>

Abstract: In the phase shifted full bridge (PSFB) pulse width modulation (PWM) converter, external snubber capacitors are connected in parallel to insulated gate bipolar transistors (IGBTs) in order to decrease turnoff losses. The zero voltage transition (ZVT) condition is not provided at light loads, thus the parallel capacitors discharge through IGBTs at turn on which causes switching losses and failure risk of the IGBTs. Capacitor discharge through IGBT restricts the use of high-value snubber capacitors, and turnoff loss of the IGBT increases at high currents. This problematic condition occurs especially at the lagging leg. In this study, a new technique enabling the use of high-value snubber capacitors with the lagging leg of the PSFB PWM converter is proposed. As advantages of the proposed technique, high-capacitive discharge current through IGBT is prevented at light loads, the turn-off switching losses of the IGBTs are decreased, and the performance of the converter is improved at high currents. The proposed PSFB PWM converter includes an auxiliary circuit, and it has a simple structure, low cost, and ease of control as well. The operation principle and detailed design procedure of the converter are presented. The theoretical analysis is verified exactly by a prototype of 75 kHz and 10kW converter. The implementation results are presented.

#### I. INTRODUCTION

NEW techniques are proposed in order to decrease switching losses and to increase power density in dc–dc converters at high power and frequencies [1]–[4]. The applications of soft-switching methods are expanding. The most remarkable method in high-power isolated applications is Phase Shifted (PS) Zero Voltage Switching (ZVS) method, which provides all of the switches to operate with ZVS without any additional auxiliary switches. The parasitic capacitance energy is discharged by the leakage inductance, and the MOSFET turns on with zero voltage transition (ZVT). Insulated gate bipolar transistor (IGBT) is preferred over MOSFET at high voltage and high-power levels in industrial applications. Low RDSONMOSFETs are quite expensive compared to the IGBTs with equivalent current and voltage ratings. The choice of IGBT over MOSFET is mandatory due to nonavailability of high voltage and high-current MOSFET devices in some applications. An external snubber capacitor is connected in parallel to each IGBT in order to decrease turn-off losses, in case the IGBT is used in the phase shifted full bridge (PSFB) pulse width modulation (PWM) converter [5]-[26]. When the ZVT condition is not provided at no load and at light loads, the parallel capacitors discharge through IGBT at turn on and this causes increase in switching losses and failure risk of the IGBTs. This condition causes problems at specially the lagging leg [5]-[26]. Capacitor discharge through IGBT restricts the use of high-value capacitor in parallel to IGBT. Therefore, the election of the parallel capacitor value is very important. The parallel snubber capacitor value should be selected according to the speed and the maximum current of the IGBT [5]. The performance of the converter decreases rapidly at high-current levels because of the turn-off switching losses. At the leading leg, the required energy for discharging the parallel capacitor is supplied from the load current, so the use of high-value capacitor in the leading leg has no drawback.

In PSFB PWM dc–dc converters, some problems arises such as variation of duty cycle with load current, hard switching because of insufficient energy in leakage inductance at light loads, and high-voltage peaks and oscillations at the output diodes, and increment in the conduction losses because of the primary current flowing in the freewheeling interval. It is possible to encounter many studies in the literature about these converters and solution for the problems [5]–[26].

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

## On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

In [6], the required large resonant inductor is replaced with linear variable inductor (LVI) which is controlled by output current. The required energy for ZVS operation at low-current levels is obtained by means of the high value of the LVI. The value of LVI decreases approximately linearly with increasing current. The softswitching operation range is extended and dependency of ZVS operation on the load current is decreased.

In [7], an auxiliary circuit which includes two MOSFETs and a serial inductance is proposed. The inductance current is increased before the IGBT devices on the lagging leg are turned off. The ZVS conditions of the FB converter are improved, but the losses in the auxiliary circuit reduce the efficiency. The auxiliary circuit does not operate with soft switching. Main IGBTs are subjected to the current stress before turn off and this increases the switching losses in the turn-off process. The proposed method is not preferred due to low efficiency, high cost, and control difficulty.

In [8], the ZVS operation is achieved over the entire conversion range in the PSFB PWM converter for an ohmic load. The proposed converter is suitable for the applications, where load current proportionally increases with output voltage. When

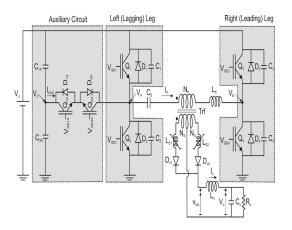

Fig. 1. Proposed PSFB PWM converter.

duty ratio is low and output current is high, soft switching is not provided.

In this study, a novel auxiliary circuit for the PSFB PWM converter using IGBTs is proposed. The proposed circuit enables the use of high-value capacitors with the lagging leg of the PSFB PWM converter without any problems. At no load, detrimental effects of the surge current to the IGBT due to the snubber capacitors are

prevented, and turn-off switching losses of the IGBTs are decreased. This novel converter requires resonant inductance much less than conventional PSFB PWM converter. The proposed method decreases the turn-off switching losses at high currents and improves the performance of the converter .Besides, parasitic oscillations and conduction losses of output diodes are decreased. The theoretical analysis of the proposed converter is given and verified exactly by a prototype of 75 kHz and 10kW converter.

#### **II. OPERATION PRINCIPLES AND ANALYSIS**

#### A. Definition and Assumptions

The proposed converter is shown in Fig. 1. It consists of a conventional PSFB PWM converter and an auxiliary circuit connected to the lagging leg. The auxiliary circuit contains two IGBTs with reverse recovery diodes and two capacitors C1A,C2A. At low-output currents, converter operates as the conventional PSFB PWM converter. Low-valued snubber capacitors are connected at the lagging leg. These capacitors provide ZVS operation at light loads and improve the turn-off behavior of the IGBT until a current level.

In the proposed converter, auxiliary circuit is operated only at high-output currents. By means of the auxiliary circuit, high value capacitors are connected to the lagging leg and the turnoff performance of the lagging leg switches is improved. The IGBTs used in the auxiliary circuit operate under soft-switching conditions. The conduction loss of the auxiliary switches is very low because they conduct current for a very short time. The operation of the auxiliary circuit starts when primary current IP is larger than boundary current level Ia.

The following assumptions are made to simplify the steady state analysis of the circuit during one switching cycle:

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

## On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

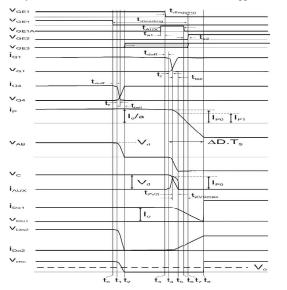

Fig. 2. Key waveforms concerning the operation stages in the proposed PSFB PWM converter.

1) input voltage Vd is constant;

2) equivalent series inductances of the parallel snubber capacitors are neglected;

3) the blocking capacitor CS is large enough to be neglected at high-frequency operation;

4) the effect of the saturable inductors used to prevent parasitic oscillations at the secondary are neglected.

B. Operation Stages

The basic operation of the proposed soft-switching converter has six operating stages within each half cycle. The operation waveforms are shown in Fig. 2. The equivalent circuits for each operating stage are shown in Fig. 3(a)-(f).

Stage 1 ([t0 < t < t1: Fig. 3(a)]): At the beginning of this stage, Q1 and Q4 are conducting, input voltage Vd is applied to the transformer's primary and power is transferred to the output. Output current flows through the diode Do1. The initial voltage of VC is equal to Vd. At t = t0, drive signal VGE4 is removed and Q4 starts to turn off. At the beginning of the turn-off process there exists a delay defined as tdoff. In this interval IQ1 = IQ4 =

IP, Q4 is still in the on-state and current flows through the transistor.

Stage 2 ([t1 < t < t2 : Fig. 3(b)]): In the turn-off process of Q4 two intervals occur which are defined as current fall time tf, and tail current time ttail. The current of Q4 begins to decrease after t1 and it falls to Itail value at the end of tf. In this interval, there is little increase on the voltage of Q4 because of the parallel capacitors. The

turn-off loss of the IGBT is very low in comparison to the hard switching case. In this stage, the parallel capacitor CP is the sum of C3 and C4 . The leakage capacitor of the transformer is neglected in respect of parallel capacitor.

If ttail is neglected, the parallel capacitor is assumed to charge linearly. The voltage of Q4 is given by

$$\sqrt{Q4} = \frac{-Ip \, tf}{Cp} \tag{1}$$

When the voltage of Q4 reaches to Vd, D3 starts to conduct. The turn-off loss of Q4 is approximated as

$$\mathsf{Eoff} = \frac{\mathsf{t}\mathsf{f}^2\mathsf{I}\mathsf{p}^2}{24\mathsf{C}\mathsf{p}} \tag{2}$$

Stage 3 ([t2 < t < t4: Fig. 3(c)]): This interval starts at t =t2, when D3 diode turns on. Q1 and D3 are conducting in this freewheeling interval. After the diode D3 turns on, the drive signal of Q3 can be applied. The signal should be applied before the primary current IP becomes zero. At t = t3, drive signal VGE1 is removed and this interval begins. At the beginning of the turn-off process there exists a delay defined as tdoff. The transistor is still in the on-state and current flows through the transistor.

Stage 4 ([t4 < t < t5: Fig. 3(d)]): At t = t4, lagging leg transition begins. The initial value of primary current is IP 0. In this stage two different operation modes occur depending on the primary current level. If the primary current is smaller than Ia, auxiliary circuit is not activated (Mode-1). This mode of the converter would have conventional operation. Proposed converter waveforms are the same as the conventional one's except VGE1A, VC, and IAUX. In this case, the parallel capacitor, CP is the sum of C1 and C2. The inductance energy is enough to charge the low-valued snubber capacitors, and soft switching is obtained. If primary current is larger than Ia, auxiliary circuit is operated (Mode-2) as shown in Fig. 3(d). In this case, the parallel capacitor, CP is the sum of C1, C2, C1A, and C2A. Due to additional high-valued capacitors, soft switching is obtained at high-current levels. The waveforms given in Fig. 2 are drawn for Mode-2. This interval is completed with discharge of the capacitor (C2 //C2A) through the resonance between LS and CP, and primary current falls to IP 1 level.

Stage 5 ([t5 < t < t7: Fig. 3(e)]): When D2 diode turns on at t = t5, negative voltage is applied to LS, and current falls to zero linearly. After the diode D2 turns on, the drive signal of Q2 can be applied. The auxiliary switch drive signal is removed at t = t6. This interval is completed when the primary current falls to zero.

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

### On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

I

Stage 6 ([t7 < t < t8 : Fig. 3(f)]): In this interval, primary current decreases from 0 to -Io /a. At t = t8, the current of Do1 falls to zero and output current is commutated to Do2. After t8 ,normal PWM operation takes place and power is transferred to the output. The operation in the second half cycle is symmetrical to the first one, and a new TS period starts after the second half cycle.

#### III. MAIN FEATURES AND DESIGN PROCEDURE

In this section, the design procedure of the proposed converter is given. The component values for implementing the converter are determined according to the design procedure.

#### A.Selection of the Boundary Current Ia

The boundary current level Ia that auxiliary circuit starts to operate is

$$Ia = Vd\sqrt{Cp/Ls}$$

(3)

The ZVS operation range of the lagging leg switches is increased with decreasing Ia. Low Ia value is obtained by selecting low CP value and high LS value. In the case of low CP value, the turn-off losses increases. High value of LS is not appropriate because it increases conduction and duty cycle losses. Besides, the selection of Ia also depends on the characteristics of the IGBTs, and nominal current of the converter.

#### **B.Control Signals and Dead-Time Requirements**

The required dead time between Q3 and Q4 Switches of the leading leg, tdleading , should provide

$$tdleading > tdoff + tf + ttail$$

(4)

where, tdoff is turn-off delay time, tf is fall time of the current to the tail current level, and ttail is the tail current time. The required dead time between Q1 and Q2 switches of the lagging leg, tdlagging , should provide following condition:

$$tdlagging > tdoff + tf + ttail.$$

(5)

The required dead time between lagging leg switches varies depending on the primary current. In order to turn off lagging leg switches with ZVS, the stored inductance

energy should be sufficient to charge/discharge parallel capacitors

$$1/2Lslp^2 \ge 1/2CpVd^2 \tag{6}$$

From this equation, the minimum current level IP min required to provide ZVS is given by

$$pmin = Vd\sqrt{Cp/Ls}$$

(7)

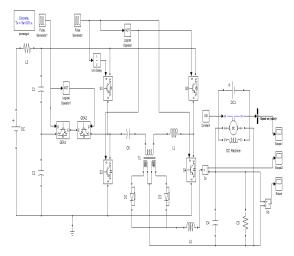

Fig.3. Simulation Circuit Diagram

Copyright to IJIRSET

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

## On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

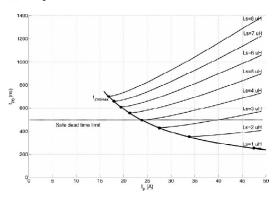

(b).Switching Speed

(c).Output Load Current

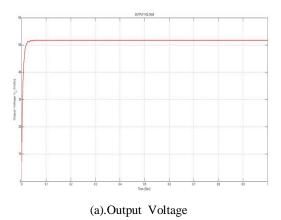

Fig. 4. Characteristics of the proposed converter for CP = 25 nF.

As seen from Fig. 6, for LS values smaller than 5  $\mu H$ , minimum dead-time requirement (500 ns) is not satisfied. As a result, LS inductance can be chosen between 5  $\mu H$  and 8  $\mu H$ . The calculated Ia , tZVSmax, tP 0 , and  $\Delta D$  variables for the values of LS.

In the proposed converter, shown in Fig 3. The output voltage, output load current and witching speed are shown. The selected values of CP and LS provide ZVT operation from 8.9 to 40A primary current for the IGBTs in the lagging leg. The use of the same component values in the conventional SFBPWM converter results in ZVT operation from 21.21 A to 40A primary current. In order to start ZVT operation at the same primary current in conventional PSFB PWM converter, 25  $\mu$ H inductance value is required which results an increase in duty cycle loss as much as five times.

The proposed converter, turn-off loss of the lagging leg switches is four times lower than that of the conventional converter, at full load. If the operation frequency is higher this advantage becomes more evident.

#### **IV. CONCLUSION**

In this study, a new method enabling the use of highvalued snubber capacitors with the lagging leg of the PSFB PWM converter is developed. Thanks to the new method, the turnoff switching losses are decreased, and the performance of the converter is improved at high currents. In the proposed PSFB PWM converter, IGBTs are used instead of MOSFETs due to their low cost and low-conduction losses. Auxiliary circuit is operated only during charging/discharging of capacitor at the lagging leg thus conduction loss is low. The control and design principles are similar to the conventional PSFB PWM converter.

The proposed topology has the following advantages compared to the other PSFB PWM converters presented in the literature:

1) Turn-off losses of the lagging leg IGBTs are decreased by the use of high-valued snubber capacitors.

2) It is possible to select resonant inductance smaller and to decrease duty cycle loss. Auxiliary circuit is started at high currents, so the required energy for discharging highvalued snubber capacitors is available.

3) Transformer conversion ratio can be selected higher, thus resulting in lower conduction losses.4) At no load, detrimental effects of the surge current to the IGBT and snubber capacitors are prevented, and turn-off switching losses of the IGBTs are decreased.

5) All semiconductor devices in the circuit are switched under soft switching at wide load range. The main switches are perfectly turned on and turn off with ZVT

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

## On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

and ZVS, respectively. The auxiliary switches are turned on and turn off with ZVS.

6) At very low-current levels soft switching is lost but in this case, the switching losses are negligible.

#### REFERENCES

[1] H. Bodur and A. F. Bakan, "A new ZVT–ZCT–PWM DC–DC converter,"IEEE Trans. Power Electron., vol. 19, no. 3, pp. 676–684, May 2004.

[2] A. F. Bakan, H. Bodur, and I. Aksoy, "A novel ZVT-ZCT PWM DC-DC converter," presented at the 11th Eur. Conf. Power Electron. Appl. (EPE), Dresden, Germany, Sep. 2005.

Appl. (EPE),Dresden, Germany, Sep. 2005.

[3] H. Bodur and A. F. Bakan, "An improved ZCT-PWM DC-DC converter for high-power and frequency applications," IEEE Trans. Ind. Electron., vol. 51, no. 1, pp. 89–95, Feb. 2004.

[4] I. Aksoy, H. Bodur, and A. F. Bakan, "A new ZVT–ZCT–PWM DC– DC converter," IEEE Trans. Power Electron., vol. 25, no. 8, pp. 2093– 2105,Aug. 2010.

[5] A. F. Bakan, T. Aksoy, N. Altıntas, and H. Bodur, "An experimental investigation of switching losses of the IGBT in PSFB PWM DC-DC converters depending on the parallel snubber capacitor," presented at the Electron., Telecommun. Artificial Intell. (ETAI) Conf.: [E4-2, CD ROM], Ohrid, Macedonia, Sep. 26–29, 2009.

[6] A. F. Bakan, "A new LVI assisted PSFB PWM DC-DC converter," in Proc. 6th Int. Conf. Electr. Electron. Eng. (ELECO), Bursa, Turkey, Nov.5–8, 2009, pp. 230–233.

[7] J. G. Cho, "IGBT based zero voltage transition full bridgePWMconverter for high power applications," IEE Trans. Electr. Power Appl., vol. 143,no. 6, pp. 475–480, Nov. 1996.

[8] M. Borage, S. Tiwari, S. Bhardwaj, and S.Kotaiah, "A full-bridge DC–DC converter with zero-voltage-switching over the entire conversion range,"IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1743–1750, Jul. 2008.

[9] S. Hamada and M. Nakaoka, "Analysis and design of a saturable reactor assisted soft-switching full-bridge dc-dc converter," IEEE Trans. Power Electron., vol. 9, no. 3, pp. 309–317, May 1994.

[10] S. Jeon and G. H. Cho, "A zero-voltage and zero-current switching full bridge DC–DC converter with transformer isolation," IEEE Trans. Power Electron., vol. 16, no. 5, pp. 573–580, Sep. 2001.

[11] E. Kim and Y. Kim, "A ZVZCS PWM FB DC/DC converter using a modified energy-recovery snubber," IEEE Trans. Ind. Electron., vol. 49,no. 5, pp. 1120–1127, Oct. 2002.

[12] Y. Jang, M. M. Jovanovic, and Y. Chang, "A new ZVS-PWM fullbridge converter," IEEE Trans. Power Electron., vol. 18, no. 5, pp. 1122–1129, Sep. 2003.

[13] Y. Jang and M. M. Jovanovic, "A new family of full-bridge ZVS converters,"IEEE Trans. Power Electron., vol. 19, no. 3, pp. 701–708, May 2004.

[14] G. Koo, G. Moon, and M. Y. Youn, "New zero-voltage-switching phaseshift full-bridge converter with low conduction losses," IEEE Trans. Ind.Electron., vol. 52, no. 1, pp. 228–235, Feb. 2005.

[15] B. Lin, H. Chiang, and C. Chen, "Analysis and implementation of a ZVS-PWM converter with series-connected transformers," IEEE Trans.Circuits Syst.—II: Express Briefs, vol. 54, no. 10, pp. 917–921, Oct. 2007.

[16] W. Chen, X. Ruan, and R. Zhang, "A novel zero-voltage-switching PWM full bridge converter," IEEE Trans. Power Electron., vol. 23, no. 2,pp. 793–801, Mar. 2008.

[17] J. A. Sabat'e, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "Design considerations for high-voltage high-power full-bridge zero voltage switching PWM converter," in Proc. IEEE APEC Conf. Rec., 1990,pp. 275–284.

[18] R. Redl, N. O. Sokal, and L. Balogh, "A novel soft-switching fullbridge dc/dc converter: Analysis, design considerations, and experimental results at 1.5 kW, 100 kHz," IEEE Trans. Power Electron., vol. 6, no. 3, pp. 408–418, Jul. 1991.

[19] J. G. Cho, J. A. Sabat'e, and F. C. Lee, "Novel full bridge zero voltage transition PWM dc/dc converter for high power applications," in Proc.IEEE-APEC Conf. Rec., 1994, pp. 143–149.

[20] R. Redl, L. Balogh, and D.W. Edwards, "Optimum ZVS full-bridge dc/dc converter with PWM phase-shift control: Analysis, design considerations, and experimentation," in Proc. IEEE APEC Conf. Rec., 1994, pp. 159–165.

[21] X. Ruan and Y. Yan, "A novel zero-voltage and zero-current switching PWM full-bridge converter using two diodes in series with the lagging leg," IEEE Trans. Ind. Electron., vol. 48, no. 4, pp. 777–785, Aug. 2001.

[22] G. Hua, F. C. Lee, and M. M. Jovanovic, "An improved full-bridge zerovoltage-switchedPWMconverter using a saturable inductor," IEEE Trans.Power Electron., vol. 8, no. 4, pp. 530–534, Oct. 1993.

[23] A. F. Bakan, H. Bodur, 'I. Aksoy, and N. Altıntas,, "A review of the full bridge PSFB PWM DC-DC converters," in Proc. Electr.electron.Comput. Eng. Conf. (ELECO), Bursa, Malaysia, Nov. 2008, pp. 366–370.

[24] J. Dudrik, P. Sp'anik, and N. Trip, "Zero-voltage and zero-current switching full-bridge DC–DC converter with auxiliary transformer," IEEE Trans.Power Electron., vol. 21, no. 5, pp. 1328–1335, Sep. 2006.

[25] C. Bo-Yuan and L. Yen-Shin, "Switching control technique of phase-shift controlled full-bridge converter to improve efficiency under light-load

and standby conditions without additional auxiliary components," IEEE Trans. Power Electron., vol. 25, no. 4, pp. 1001–1012, Apr. 2010.

[26] Z. Xin, H. S. Chung, R Xinbo, and A Ioinovici, "A ZCS full-bridge converter without voltage overstress on the switches," IEEE Trans. Power Electron., vol. 25, no. 3, pp. 686–698, Mar. 2010.