International Journal of Innovative Research in Science, Engineering and Technology

Volume 3, Special Issue 3, March 2014

2014 International Conference on Innovations in Engineering and Technology (ICIET'14) On 21<sup>st</sup> & 22<sup>nd</sup> March Organized by

K.L.N. College of Engineering, Madurai, Tamil Nadu, India

# Performance Evaluation of Digital CMOS Circuits Using Complementary Pass Transistor Network

C.Kalyana sundaram , A.Palanivel 1Asst Professor , (SR)/ ECE, Mepco Schlenk Engineering College, india.

2PG Student, Mepco Schlenk Engineering College, india.

Abstract— An important issue in the design of VLSI Circuits is the choice of the basic circuit approach and topology for implementing various logic and arithmetic functions such as adders and multipliers. Complementary Pass-transistor Logic (CPL) is the approach to reduce the physical capacitances in a digital circuit and in this way lower the power consumption. Charge-recovery circuitry has the potential to reduce dynamic power consumption in digital systems with significant switching activity. The overall energy-efficiency of charge-recovery circuitry therefore depends on the rate at which transitions occur, yielding an inverse relationship between energy consumption and clock period. This paper mainly focuses on Boost Logic, a charge recovery circuit family that can operate efficiently at clock frequencies in excess of 1 GHz. Complementary Passtransistor Boost Logic(CPBL) is a low-power charge recovery logic structure powered by 2-phase non-overlap alternating power clocks PC and ~PC and requires no DC power supply. To achieve high energy efficiency, Boost Logic relies on a combination of aggressive voltage scaling, and charge-recovery techniques. In order to achieve low power in adders (Full Adder, Ripple Carry Adder), Multiplexer and Multiplier has been designed using CPBL. The power efficiency obtained using CPBL is 16% lower than CPAL (Complementary Passtransistor Adiabatic Logic). Low power circuits are designed using CPBL is simulated using Tanner EDA 15.1.

**Keywords**— Low-power, Charge recovery logic, CPL ,CPBL, CPAL, Adders, Tanner EDA, power clock.

## I. INTRODUCTION

Main objectives of most of the system level or circuit design are high performance and power optimization. For high performance system design, propagation delay minimization plays an important role. Basically size, cost, performance and power consumption are the crucial issues in low power portable battery operated system design. Excessive power dissipation which overheats thereby degrading the performance and lifetime is not at all affordable. Energy consumption being an important constraint for battery life estimation, VLSI based low power design of dedicated multimode signal conditioning integrated circuit is desirable. Modern systems consist of digital realization of analog processes and this helps to design system with high precision, high signal to noise ratio, repeatability and flexibility. DSP systems can be realized with custom designed hardware circuits or ultralow power high performance programmable processors fabricated using VLSI circuit technology.

## II.N-TYPE Vs P-TYPE TRANSISTORS

Motivation to reduce energy consumption of logic circuits comes from increasing difficulties in removing heat from high speed VLSI circuits. The importance of reducing power dissipation in digital systems is increasing as the range and complexity of applications in portable and embedded computing continues to increase. Systemlevel issues such as battery life, weight, and size are directly affected by power dissipation. A trend into reducing power dissipation of the digital systems only serves to improve the performance and capabilities of these systems.

The power dissipation is a critical concern in the design of VLSI circuits with increasing package density and working speed. Also the energy consumption of batterydriven systems is above all problem to be considered. Many low power design methods have been developed to reduce CMOS digital circuit's power consumption. However the adiabatic circuit is an attractive way to obtain extreme low power level which conventional CMOS digital circuit can't reach. At present time, lots of digital systems are targeted at portable, battery-operated systems, so power dissipation is one of the primary design constraints.

To reduce the power dissipation, the circuit designer can minimize the switching events, decrease the node capacitance, reduce the voltage swing, or apply a combination of these methods. In all these cases, the energy drawn from the power supply is used only once before being dissipated. To increase the energy efficiency of the logic circuit, other measures can be introduced for recycling the energy drawn from the power supply. A novel class of logic circuits called Adiabatic Logic offers the possibility of further reducing the energy dissipated during switching events, and the possibility of recycling or reusing, some of the energy drawn from the power supply.

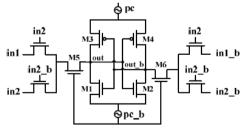

Fig 1.PMOS Full Adder

Recently, a novel approach to reduce power dissipation in digital circuits was proposed, which is to be used and verified in many digital applications. The approach, called adiabatic logic design, utilizes clocked ac power to slowly charge the node capacitances and then partially recover the energy associated with that charge. The term adiabatic is typically used to describe thermodynamic process that has no energy exchange with the environment, and therefore no energy loss in the form of heat.

Adiabatic digital circuits have the ability to recover energy once committed in computation and make it available for recycling. Due to the trend of increasing clock frequencies and transistor count, power demands new System-on-Chip designs will continue to grow. Adiabatic logic style has emerged as a promising approach to achieve ultra-low power without sacrificing noise immunity and driving ability. Adiabatic circuits are low power circuits which use "reversible logic" to conserve energy.

Adiabatic logic is a low-power circuit design approach where the signal energy stored on a capacitor may be recycled instead of dissipated as heat. Power dissipation can be avoided if the capacitor is slowly charged with a voltage ramp. It is possible to recover this charge back into the power source by discharging the capacitor to a down-ramping supply. Adiabatic principles, together with charge reuse by redistribution, can be utilized for power saving in interconnects.

Adiabatic logic is an attractive low power approach by utilizing AC voltage supplies (power clocks) to recycle the energy of circuits instead of being dissipated as heat. Adiabatic circuits are work on the principal of adiabatic charging and discharging by which energy is recycled from output nodes instead of discharging it to ground. Conventional CMOS circuits achieve a logic='1' or logic='0' by charging the load capacitor to supply voltage  $V_{dd}$  and discharging it to ground respectively. Thus every time a Charge-discharge cycle occurs an amount of energy equal to CV2 is dissipated. Unlike the conventional CMOS circuits, in adiabatic circuits energy is recycled. Instead of discharging the capacitor to ground, the charge is discharged to the power supply.

Fig 2.NMOS Full Adder

Since the charge has to be discharged to supply, the supply in adiabatic circuits is a time varying one called the power clock. It has been observed that among the different waveforms for charging or discharging the load capacitor, a ramp is more efficient and as such trapezoidal power clocks have been used in many adiabatic circuit styles. Many adiabatic logic circuits which dissipate less power than static CMOS logic circuits have been introduced as a promising approach in low power circuit design.

Field Programmable Gate Arrays have traditionally been configured by hardware designers using specific so called Hardware Design Languages (HDLs). There are already few such languages available offering different levels of abstraction but the most important ones are Verilog HDL(VHDL) and Very High Speed Integrated Circuits (VHSIC).

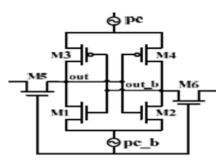

#### III.CHARGE RECOVERY

Charge-recovery circuitry has the potential to reduce dynamic power consumption in digital systems with significant switching activity. To keep energy consumption to a minimum, Charge-recovery circuitry is typically designed so that it maintains low voltage drops across device channels, while recovering the charge supplied to it every clock cycle. The overall energyefficiency of charge-recovery circuitry therefore depends on the rate at which transitions occur, yielding an inverse relationship between energy consumption and clock period. Relying on this energy/latency tradeoff, Chargerecovery circuitry can operate with energy consumption below, the fundamental limit of static CMOS.

Fig 3. Charge Recovery Logic.

Early research on Charge-Recovery Logic design focused on micro pipelined dynamic circuits with multiple (four or more) clock phases for recovering charge. These clock phases were generated by resonating the parasitic capacitance of the circuitry through the introduction of inductors. To maximize the efficiency of recovery, the inductors were chosen so that the resulting tank system resonates at the target clock frequency. In these early multiphase designs, the resulting complexity of the recovery mechanisms was considerable, especially in the case of the so-called reversible designs, which theoretically offer the greatest energy saving potential. Moreover, the synchronization of multiple clock phases was impeding high-speed operation.

## IV. COMPLEMENTARY PASS TRANSISTOR LOGIC

Low power techniques are of great importance in VLSI design applied for digital electronics, especially the portable devices. Several techniques have been developed to achieve the goal of low power dissipation. Voltage scaling is one of the most effective methods to reduce dynamic power consumption in digital system, as the energy consumed when charging and discharging a capacitive load C across a voltage difference V grows quadratic ally with V.

Charge Recovery Logic (CRL) is one of the most promising methods to achieve low power dissipation in digital systems with significant switching activities. The CRL structure is powered by power clocks, the sinusoidal signals produced by RLC resonant circuit, with which charges are recycled to power supply instead of flowing to the ground and being consumed.

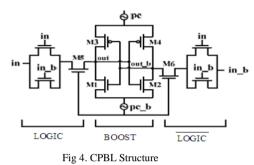

A new Charge Recovery Logic structure called Complementary Pass-transistor Boost Logic (CPBL) is proposed, fully powered by 2-phase non-overlap alternating power clocks pc and ~pc, energy dissipates only on the parasitic resistance of the transistors working in linear region which is different from the proposed Boost Logic that DC power supply is still necessary. Each CPBL gate consists of two parts working in mutually exclusive intervals: the logical evaluation stage (Logic) and charge-recovering amplification stage (Boost). Logic stage is implemented by complementary pass-transistor network, while the Boost stage consists of a pair of cross-coupled inverters connected to the pc and ~pc.

The operation of CPBL gate is explained in Section 4.1 in detail. Also another charge recovery structure CPAL involved with pass-transistor network has been proposed. However, it suffers from some problems, such as low operation frequency and the need of transform circuit to produce particular power clock waveforms. The CPBL has relieved these problems and retains the merit of energy saving in the meanwhile.

## A. CPBL STRUCTURE

Fig4. shows the basic structure of Complementary Pass-transistor Boost Logic (CPBL). Each CPBL gate consists of two parts: the complementary pass-transistor network which acts as the logical evaluation part, the "Logic" and a pair of cross-coupled inverters connected to complementary power clocks pc and ~pc which acts as the charge recovery amplification part, the "Boost". They work in two mutually exclusive intervals which will be referred to as Logic and Boost stages.

#### **B.CPBL OPERATION**

Each CPBL gate operates in two stages, Logic and Boost. When Logic evaluates, Boost does not drive the outputs and vice versa. The voltage swing of power clock is from 0 to  $V_{DD}$ .

During the Logic stage, power clock pc and ~pc are in low half cycle and high half cycle respectively. As such, Boost stage is in cut-off and the clocked transistors M5 and M6 turn on, evaluated logic values can be transferred to output nodes. The complementary pass-transistor network charges the out2 to approximately  $V_{DD}$ - $V_{TH}$  and discharges the out2 to the GND and there is a little voltage difference achieved across the output nodes by the end of the Logic stage. The Schematic design for the CPBL AND gate as shown in the following figure.

## Fig 5. CPBL AND gate

This work presents a new Charge Recovery Logic structure, the Complementary Pass-transistor Boost Logic (CPBL) which is capable of achieving considerable low power dissipation while operating at multi-MHz CPBL consists of two parts: the complementary passtransistor network and 4-Transistor Boost stage, fulfilling the logical evaluation and signal amplification respectively. It is fully powered by 2-phase alternating sinusoidal power clocks pc and ~pc produced by RLC resonant circuit.

## V.RESULTS AND DISCUSSION

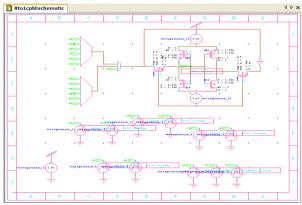

#### A. SCHEMATIC SIMULATION

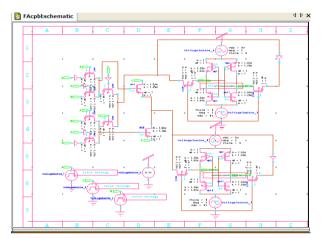

In this work, the Schematic design of Digital CMOS circuits using Complementary Pass Transistor Logic (CPL) is designed and simulated in the S-Edit. The power consumption is estimated by using the T-spice and their corresponding simulated waveform results are obtained in W-Edit.

Transistor count of CPAL circuits are considerably less than the another techniques of Adiabatic Logic Design. CPAL circuits have more efficient energy transfer and recovery, because the non-adiabatic energy loss of output Loads has been completely eliminated by using complementary pass-transistor logic for evaluation and transmission gates for energy recovery. Complementary pass transistor logic concept reduces the complexity of circuit.

Fig 6. Schematic view of FULL ADDER

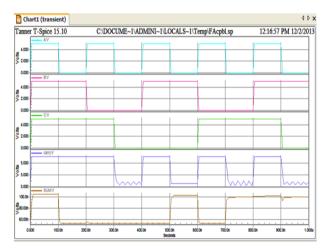

Fig.7Simulation Results of FULL ADDER DEVICE AND NODE COUNTS

| DEVICE            | NODE<br>COUNT |

|-------------------|---------------|

| MOSFETs           | 34            |

| MOSFET geometries | 2             |

| Voltage sources   | 8             |

| Sub circuits      | 7             |

| Model Definitions | 5             |

| Computed Models   | 2             |

| Independent nodes | 15            |

| Boundary nodes    | 9             |

| Total nodes       | 24            |

| TABLE.1 |  |

|---------|--|

|         |  |

POWER RESULTS OF FULL ADDER

| Voltage<br>Source            | Minimum<br>Power                                | Maximum<br>Power                                                 | Average<br>Power<br>in watts  |

|------------------------------|-------------------------------------------------|------------------------------------------------------------------|-------------------------------|

| Vvoltag<br>e<br>Source_<br>1 | 0.000000<br>e <sup>+000</sup><br>at time 0      | 1.120364e <sup>-003</sup><br>at time<br>4.01875e <sup>-007</sup> | 1.78464<br>7e <sup>-006</sup> |

| VVoltag<br>eSource<br>_2     | 0.000000<br>e <sup>+000</sup><br>at time 0      | 3.260543e <sup>-003</sup><br>at time<br>5.03568e <sup>-007</sup> | 1.02106<br>8e-005             |

| VVoltag<br>eSource<br>_3     | 0.000000<br>$e^{+000}$<br>at time 0             | 1.622141 e <sup>-004</sup><br>at time<br>6.0351e <sup>-007</sup> | 2.36367<br>5e <sup>-007</sup> |

| VVoltag<br>eSource<br>_4     | 1.89918e-<br>009<br>at time<br>4.38529<br>e-007 | 2.153464e-002<br>at time<br>2.03544e-009                         | 6.95793<br>0e-004             |

#### **B. RIPPLE CARRY ADDER**

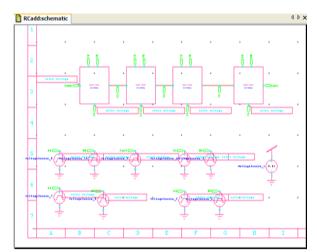

It is possible to create a logical circuit using multiple full adders to add N-bit numbers. Each full adder inputs a Cin, which is the Cout of the previous adder. This kind of adder is a ripple carry adder, since each carry bit "ripples" to the next full adder. The first full adder may be replaced by a half adder. Here 4-bit ripple carry adder is implemented with the help of four full adder blocks.

## Performance Evaluation of Digital CMOS Circuits Using Complementary Pass...

Fig.8 Schematic view of RIPPLE CARRY ADDER

| Chart1 (tra |          |         |          |          |            |              |           |         | (               |

|-------------|----------|---------|----------|----------|------------|--------------|-----------|---------|-----------------|

| anner T-Spi | ce 15.10 |         | C:\DOCUM | ~1\ADMIN | I~1\LOCALS | S~1\Temp\PTI | .RC.sp    | 5:      | 00:00 PM 12/2/2 |

| 5.000       | CoutV    |         | _        |          | _          |              | _         |         |                 |

| 0.000       | Sum0:V   |         |          |          |            |              |           |         |                 |

| 5.000       | Sumv.v   |         |          |          |            |              |           |         |                 |

| 0.000       | Sum1:V   |         |          |          |            |              |           |         |                 |

| 5.000       |          |         |          |          |            |              |           |         |                 |

| 5.000       | Sum2:V   |         |          |          |            |              |           |         |                 |

|             |          |         |          |          |            |              |           |         |                 |

|             | Sum3:V   |         |          |          |            | _            |           |         |                 |

|             |          |         |          |          |            |              |           | 1       |                 |

| 5.000       | AD:V     | _       | _        |          | _          | _            | _         |         | _               |

|             |          |         |          |          |            |              |           |         |                 |

| 1.000       | A1:V     | _       | _        |          |            | _            | _         |         |                 |

|             | A2V      |         |          |          |            |              |           |         |                 |

| 0000        | INC.Y    |         |          |          |            |              |           |         |                 |

| .000        | A3:V     |         |          |          |            |              |           |         |                 |

| 1000        |          |         |          |          |            |              |           |         |                 |

|             | B0:V     |         |          |          |            |              |           |         |                 |

| 000         |          |         |          |          |            |              |           |         |                 |

| 5.000       | B1:V     | _       |          |          |            | _            |           |         |                 |

| .000        |          |         |          |          |            |              |           |         |                 |

| 1000 ==     | B2:V     |         |          |          |            |              |           |         |                 |

|             | B3:V     |         |          |          | [          |              |           |         |                 |

| 5,000       | 50.T     |         |          |          |            |              |           |         |                 |

|             | Cin:V    |         |          |          |            |              |           |         |                 |

| 5.000       |          |         |          |          |            |              |           |         |                 |

| 0.000       | 100.0n   | 200.0n  | 300.0n   | 400.0n   | 500.0n     | 600.0n       | 700.0n    | 800.0n  | 900.0n 1        |

| 0.000       | 199.411  | 444.411 | 000.011  | 100.011  | Seconds    | Anno Ann     | - 499.001 | -14.411 | vela an         |

Fig.9 Simulation Results of Ripple Carry Adder

| DEVICE            | NODE<br>COUNT |

|-------------------|---------------|

| MOSFETs           | 136           |

| MOSFET geometries | 2             |

| Voltage sources   | 26            |

| Sub circuits      | 32            |

| Model Definitions | 5             |

| Computed Models   | 2             |

| Independent nodes | 60            |

| Boundary nodes    | 27            |

| Total nodes       | 87            |

TABLE.2 Power Results Of Ripple Carry Adder

| Voltage<br>Source     | Minimum<br>Power                       | Maximum<br>Power                              | Average<br>Power in<br>watts |

|-----------------------|----------------------------------------|-----------------------------------------------|------------------------------|

| VVoltage<br>Source_1  | 2.18999e-007<br>at time<br>4.0552e-007 | 8.26214e-<br>002 at time<br>2.0467e-009       | 1.863877<br>e-003            |

| VVoltage<br>Source_2  | 0.000000e+00<br>at time 0              | 1.02420e-<br>003 at time<br>2.11497<br>e-009  | 4.514442<br>e-006            |

| VVoltage<br>Source_3  | 0.000000e+00<br>at time 0              | 4.59133e-<br>003 at time<br>9.03305<br>e-007  | 1.388041<br>e-005            |

| VVoltage<br>Source_4  | 0.000000e+00<br>at time 0              | 2.40285e-<br>004 at time<br>1.03234<br>e-007  | 3.474678<br>e-007            |

| VVoltage<br>Source_5  | 0.000000e+00<br>at time 0              | 1.02420e-<br>003 at time<br>2.11497e-<br>009  | 4.514442<br>e-006            |

| VVoltage<br>Source_6  | 0.000000e+00<br>0 at time 0            | 4.59133e-<br>003 at time<br>9.03305e-<br>007  | 1.388041<br>e-005            |

| VVoltage<br>Source_7  | 0.000000e+00<br>at time 0              | 1.02420e-<br>003 at time<br>2.11497e-<br>009  | 4.514442<br>e-006            |

| VVoltage<br>Source_8  | 0.000000e+00<br>at time 0              | 4.59133e-<br>003 at time<br>9.03305e-<br>007  | 1.388041<br>e-005            |

| VVoltage<br>Source_9  | 0.000000e+00<br>at time 0              | 1.120357<br>e-003 at time<br>4.01875e-<br>007 | 1.593048<br>e-006            |

| VVoltage<br>Source_10 | 0.000000e+00<br>at time 0              | 4.041827e-<br>003 at time<br>9.03375e-<br>007 | 1.387071<br>e-005            |

# C. MULTIPLEXER

A Multiplexer or mux is a combinational circuits that selects several analog or digital input signals and forwards the selected input into a single output line. A multiplexer of  $2^n$  inputs has n selected lines, are used to select which input line to send to the output.

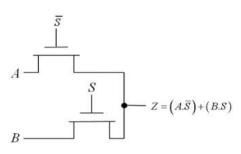

## I) 2 to 1 MULTIPLEXER

Fig.10 2 to 1 Multiplexer

The pass-transistor logic attempts to reduce the number of transistors to implement a logic by allowing the primary inputs to drive gate terminals as well as source-drain terminals.

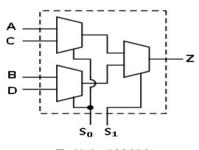

## II) 4 to 1 MULTIPLEXER

4 to 1 multiplexer is designed by using Three 2 to 1 multiplexers and Two select lines S0 and S1.

Fig.11 4 to 1 Multiplexer

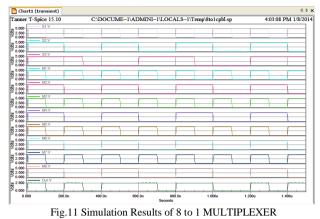

III) 8 to 1 MULTIPLEXER

$8 \mbox{ to } 1 \mbox{ multiplexer}$  is designed by using Two 4 to 1 multiplexers, one 2 to 1 multiplexer and Three select lines S0 S1 and S2.

Fig.10 Schematic view of 8 to 1 MULTIPLEXER

8

TABLE.3 POWER RESULTS OF 8 to 1 MULTIPLEXER

| TABLE.5 POWER RESULTS OF 8 to 1 MULTIPLEXER          |                                          |                                                      |                                   |  |  |

|------------------------------------------------------|------------------------------------------|------------------------------------------------------|-----------------------------------|--|--|

| Voltage<br>Source                                    | Minimum<br>Power                         | Maximum<br>Power                                     | Average<br>Power<br>in watts      |  |  |

| VVoltage<br>Source_1                                 | 2.315643e-<br>007 at time<br>4.0552e-007 | 2.31564e-<br>002 at time<br>1.20213e                 | 2.16039<br>3<br>e <sup>-003</sup> |  |  |

| VVoltage<br>Source_2                                 | 0.000000e+0<br>0<br>at time 0            | 6.79225e-<br>003 at time<br>8.05101e <sup>-007</sup> | 1.39274<br>8<br>e <sup>-003</sup> |  |  |

| VVoltage<br>Source_3                                 | 0.000000e+0<br>0<br>at time 0            | 6.79275e-<br>003 at time<br>4.05101e <sup>-007</sup> | 6.15506<br>5<br>e <sup>-004</sup> |  |  |

| VVoltage<br>Source_4<br>from time<br>0 to 1e-<br>006 | 0.000000e+0<br>0<br>at time 0            | 6.90510e-<br>003 at time<br>2.05312e <sup>-007</sup> | 1.53956<br>6<br>e <sup>-003</sup> |  |  |

| VVoltage<br>Source_5                                 | 0.000000e+0<br>0<br>at time 0            | 1.37392e-<br>003 at time<br>1.00344e                 | 2.82828<br>7<br>e <sup>-006</sup> |  |  |

| VVoltage<br>Source_6                                 | 0.000000e+0<br>00 at time 0              | 1.63667e-<br>003 at time<br>2.01841e                 | 7.65265<br>8<br>e <sup>-006</sup> |  |  |

| VVoltage<br>Source_7                                 | 0.000000e+0<br>0<br>at time 0            | 6.84930e-<br>003 at time<br>-007<br>9.08114e         | 1.29875<br>7<br>e <sup>-003</sup> |  |  |

| VVoltage<br>Source_8                                 | 0.000000e+0<br>0<br>at time 0            | 1.63349e-<br>003 at time<br>-007<br>7.03461e         | 5.69163<br>2<br>e <sup>-006</sup> |  |  |

| VVoltage<br>Source_9                                 | 0.000000e+0<br>0<br>at time 0            | 1.49252e-<br>003 at time<br>4.01605e                 | 3.42314<br>7<br>-006<br>e         |  |  |

| VVoltage<br>Source_10                                | 0.000000e+0<br>0<br>at time 0            | 3.42314 e-<br>003 at time<br>4.01605e                | 1.04093<br>6<br>e <sup>-006</sup> |  |  |

| VVoltage<br>Source_11                                | 0.000000e+0<br>0<br>at time 0            | 1.59591e-<br>004 at time<br>4.02138e                 | 1.81543<br>4<br>e <sup>-007</sup> |  |  |

## Performance Evaluation of Digital CMOS Circuits Using Complementary Pass...

| VVoltage<br>Source_12 | 0.000000e+0<br>0<br>at time 0 | 7.82133e-<br>005 at time<br>2.19524e | 1.50496<br>3<br>e <sup>-007</sup> |  |

|-----------------------|-------------------------------|--------------------------------------|-----------------------------------|--|

|-----------------------|-------------------------------|--------------------------------------|-----------------------------------|--|

#### IV) ARRAY MULTIPLIER

Array multiplier is an efficient layout of a combinational Multiplier. Multiplication of two binary number can be obtained with one micro-operation by using a combinational circuit that forms the product bit all at once thus making it a fast way of multiplying two numbers since only delay is the time for the signals to propagate through the gates that forms the multiplication array. With its good structure, this multiplier is based on the standard add and shift operations. Each partial product is generated by taking into account the multiplicand and one bit of multiplier each time. The impending addition is carried out by high-speed carry-save algorithm and the final product is obtained employing any fast adder the number of partial products depends upon the number of multiplier bits.

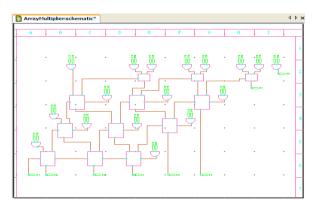

The Schematic of 4x4 Array Multiplier is shown in the following Fig. 12

Fig.12 Schematic view of ARRAY MULTIPLIER

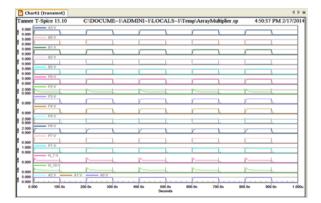

Fig.13 Simulation Results of ARRAY MULTIPLIER TABLE.4 POWER RESULTS OF ARRAY MULTIPLIER

| Voltage<br>Source    | Minimum<br>Power                  | Maximum<br>Power                 | Average<br>Power in<br>watts  |

|----------------------|-----------------------------------|----------------------------------|-------------------------------|

| VVoltage<br>Source_1 | 5.242584e<br>at time<br>4.03243 e | 6.918037e<br>at time<br>3.39658e | 2.86960<br>- <sup>001</sup> e |

| VVoltage<br>Source_2                             | 0.000000e+00<br>at time 0  | 2.43084e-003<br>at time<br>1.02125e         | 1.578898<br>-006<br>e             |

|--------------------------------------------------|----------------------------|---------------------------------------------|-----------------------------------|

| VVoltage<br>Source_3                             | 0.000000e+00<br>at time 0  | 3.04647e-003<br>at time<br>1.02088e         | 1.587092<br>-006<br>e             |

| VVoltage<br>Source_4<br>from time<br>0 to 1e-006 | 0.000000e+00<br>at time 0  | 2.37271e-003<br>at time<br>-007<br>3.02142e | 9.711132<br>e                     |

| VVoltage<br>Source_5                             | 0.000000e+00<br>at time 0  | 2.86320e-003<br>at time<br>1.02125e         | 1.768979<br>-006<br>e             |

| VVoltage<br>Source_6                             | 0.000000e+000<br>at time 0 | 1.27042e-003<br>at time<br>2.0571e          | 1.738584<br>-004<br>e             |

| VVoltage<br>Source_7                             | 0.000000e+00<br>at time 0  | 1.18083e-003<br>at time 2.05e               | 1.398516<br>- <sup>004</sup> e    |

| VVoltage<br>Source_8                             | 0.000000e+00<br>at time 0  | 8.76650e-004<br>at time<br>8.04358e         | 5.968264<br>- <sup>006</sup><br>e |

| VVoltage<br>Source_9                             | 0.000000e+00<br>at time 0  | 1.66791e-003<br>at time<br>-009<br>4.6004e  | 2.139657<br>- <sup>005</sup> e    |

## VI.. CONCLUSION

Adiabatic circuits offers reduction in the power dissipation for the VLSI circuits. Adiabatic circuits adopt a gradually rising and falling power-clock, can result in a considerable energy saving. NMOS Full Adder, Ripple Carry Adder, 8 to 1 Multiplexer and Array Multiplier are proposed using CPBL techniques. CPBL consist of two parts: the Complementary Pass Transistor network and 4-tr Boost Stage, fulfilling the logical evaluation and signal amplification respectively. It is fully powered by 2-phase alternating sinusoidal power clocks Pc and ~Pc produced by RLC resonant circuit. To demonstrate the performance and energy efficiency, 4-Ripple Carry Adder is implemented by CPBL, CPAL which is similar structure. The CPBL implementation reduces about 65% energy compared with the static CMOS and dissipates less energy with respect to CPAL.

#### VII.REFERENCES

- [1] J. Kao, W.-H. Ma, V. Sathe, and M. Papaefthymiou, "Energyefficient low-latency 600 MHz FIR with high-overdrive Charge Recovery Logic"Very Large ScaleIntegration (VLSI) Systems, IEEE Transactions on, vol. 20, no. 6, pp. 977 –988, June 2012.

- [2] J. Hu, T. Xu, and Y. Xia, "Low-power adiabatic sequential circuits with Complementary Pass-transistor Logic" in Circuits and Systems, 2005. 48<sup>th</sup>Midwest Symposium on, pp. 1398 – 1401 Vol. 2 August. 2005.

- [3] Moon, Y., Jeong, D.K, "An Efficient Charge Recovery Logic circuit" IEEE Journal of Solid-State Circuits, Vol. 31, april 1996, pp. 514-522

- [4] Y. Wu, H. Dong, Y. Wang, and J. Hu, "Low-power adiabatic sequential circuits using two-phase power-clock supply" in ASIC, 2005. ASICON 2005. 6th International Conference On, vol. 1, October. 2005, pp. 185–188.

- [5] R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus Pass-Transistor Logic" Solid-State Circuits, IEEE Journal of, vol. 32, no.7,pp. 1079 –1090, July 1997.

- [6] Ms. BhumikaNarang "Layout Design and Implementation of Adiabatic based Low Power CPAL Ripple Carry Adder"International Journal on Recent and Innovation Trends in Computing and Communication, Vol: 1 Issue: 5 pp. 453 – 457, May 2013.

- [7] D. Markovic, B. Nikolic, V.G. Oklobdzija, "A general method in synthesis of Pass-Transistor Circuits" Microelectronics Journal 31 (2000) 991–998.

- [8] BhumikaPatpatia, NehaArora, Prof. B. P. Singh, Kavita Mehta, Neelam Swami, "An Adiabatic Single Phase N-type and P-type CPAL Technique for Full Adder Design" in Proceedings of International Conference on Emerging Trends in Networks and Computer Communications ETNCC-2011 (22-24 April, 2011).

- [9] R.P. MeenaakshiSundari, Dr.R. Anita , M.K. Anandkumar, "Implementation of Low Power CMOS Full Adders Using Pass Transistor Logic"IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 2, Issue 5 (May. – Jun. 2013), PP 38-43

- [10] H. Soeleman and K. Roy, "Ultra-low power digital sub threshold logic circuits" in Low Power Electronics and Design, 1999. Proceedings. 1999 International Symposium on, august. 1999, pp. 94–96.

- [11] D. Deleganes, M. Barany, G. Geannopoulos, K. Kreitzer, A. Singh, and S.Wileratne, "Low voltage swing logic circuits for a Pentium 4 processor integer core" in Design Automation Conference, 2004. Proceedings. 41st, july 2004, pp. 678–680.

- [12] V. S. Sathe, J.-Y. Chueh, and M. C. Papaefthymiou, "Energyefficient GHz-class Charge-Recovery Logic" Solid-State Circuits, IEEE Journal of, vol. 42, no. 1, pp. 38–47, january. 2007.

- [13] W.-H. Ma, J. C. Kao, V. S. Sathe, and M. Papaefthymiou, "A 187mhz sub threshold-supply robust fir filter with Charge-Recovery Logic" in VLSI Circuits, 2009 Symposium on, june 2009, pp. 202 –203.

- [14] Yasuhiro Takahashi, Toshikazu Sekine, NazrulAnuarNayan, Michio Yokoyama, "Power-Saving Analysis of Adiabatic Logic in Sub threshold Region"2012 IEEE International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS 2012) November 4-7, 2012.