International Journal of Innovative Research in Science, Engineering and Technology

Volume 3, Special Issue 3, March 2014

2014 International Conference on Innovations in Engineering and Technology (ICIET'14) On 21<sup>st</sup>&22<sup>nd</sup>March Organized by K.L.N. College of Engineering, Madurai, Tamil Nadu, India

# Performance Analysis of VLSI Based Multilevel Inverter

Sagar U. Shinde<sup>1</sup>, Mithun Aush<sup>2</sup>, Dr. K. Vadirajacharya<sup>3</sup>

Department of Electrical Engineering, Dr. B. A. T. University Lonere, Maharashtra, India<sup>1</sup> Department of Electrical Engineering, Dr. B. A. T. University Lonere, Maharashtra, India<sup>2</sup> Department of Electrical Engineering, Dr. B. A. T. University Lonere, Maharashtra, India<sup>3</sup>

Abstract—This paper compares two different topologies of three phase inverter (i.e. diode clamped followed by cascade H-bridge) which includes five level and seven level inverters. The selection of topology and control techniques may vary according to power demands of inverter. The comparison is done with respect to THD & number of components. The switching pattern for inverter is explained well. For each inverter IGBT's are used as switching devices to make the comparison more accurate. The FFT spectrums for the outputs are presented to study the reduction in the harmonics. This paper deals with selection of multilevel inverter as a trade of between number of components, complexity & THD. The circuit is simulated using MATLAB/SIMULINK.

**Keywords**— Multilevel inverter, neutral clamped, cascaded H-bridge, THD, VSI

#### I. INTRODUCTION

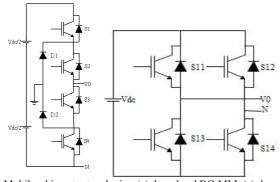

Fig. 1. Multilevel inverter topologies: (a) three-level DC-MLI, (c) three-level CHB-MLI.

Copyright to IJIRSET

www.ijirset.com

M.R. Thansekhar and N. Balaji (Eds.): ICIET'14

The preliminary studies on multilevel inverters (MLI) have been performed using three-level inverters. In recent years, multilevel inverters have gained much attention due to their various advantages such as lower common mode voltage, lower voltage stress on power switches, lower dv/dt ratio to supply lower harmonic contents in output voltage and current. Comparing two inverter topologies at the same power ratings, MLIs also have the advantages that the harmonic components of line-to-line voltages fed to load are reduced owing to its switching frequencies. The most common MLI topologies classified into three types are neutral/diode clamped MLI (DC-MLI), flying capacitor MLI (FC-MLI),and cascaded H-Bridge MLI (CHB-MLI). The two of them are shown in Fig. 1.and compared.

#### **II. INVERTER TOPOLOGIES**

Two major multilevel inverter structures applied to industrial applications listed as diode clamped, and the cascaded H-bridge inverter with separate DC sources. In addition to this, many hybrid multilevel inverters have been developed by using these basic types mentioned above. Among the three types of multilevel inverters, the cascade inverter has the least components for a given number of levels. Cascade multilevel inverters consists of a series of H-bridge cells to synthesize a desired voltage from several separate DC sources. All these properties of cascade inverters allow using various pulse width modulation (PWM) strategies to control the inverter accurately.

#### Performance Analysis of VLSI based Multilevel Inverter

#### Neutral/Diode clamped multilevel inverter Α.

The neutral clamped inverter, also known as diode clamped inverter. The basic architecture of this inverter discussed in references [5], [6]. The neutral clamped inverter delivers the staircase output voltage using several levels of DC voltages developed by DC capacitors.

If n is the number of level, then the number of capacitors required on the DC bus are (n-1), the number of power electronic switches per phase are 2(n-1) and the number of diodes per phase are 2(n-2). This design formula is most common for all the neutral clamped multilevel inverters.

The DC bus voltage is split into five levels using four capacitors C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub>, for seven level using six capacitors C1, C2, C3, C4, C5, and C6. The voltage across each capacitor is  $V_{dc}/4$  and  $V_{dc}/6$  for five level and seven level MLI and the voltage stress across each switch is limited to one capacitor voltage through clamping diodes. The switching sequences of three phase 7-level neutral clamped multilevel inverter are shown in table.1.

As the number of levels increase the harmonic distortion decreases and efficiency of the inverter increases because of the reduced switching losses. The number of levels in multilevel inverters is limited because of the large number of clamping diodes required. The reverse recovery of these diodes is especially with multicarrier PWM techniques in a high voltage application is a major design challenge.

#### В. Cascaded H-Bridge multilevel inverter

An alternative multilevel inverter topology with less power devices requirement compared to previously mentioned topologies is known as cascaded H-bridge multilevel inverter (CHB-MLI) and the topology is based on the series connection of H-bridges with separate DC sources.

Since the output terminals of the H-bridges are connected in series, the DC sources must be isolated from each other. The resulting AC output voltage is synthesized by the addition of the voltages generated by different Hbridge cells. Each single phase H-bridge generates three voltage levels as  $+V_{dc}$ , 0 &  $-V_{dc}$  by connecting the DC source to the AC output by different combinations of four switches  $S_{a1}$ ,  $S_{a2}$ ,  $S_{a1}^{-1}$  and  $S_{a2}^{-1}$  as seen in first cell of fig. 1. For the seven level CHB-MLI, three separate DC sources per phase and generates an output voltage with seven levels. To obtain  $+V_{dc}$ ,  $S_{a1}$  and  $S_{a2}^{-1}$  switches are turned on, whereas  $-V_{dc}$  level can be obtained by turning on the  $S_{a2}$ and  $S_{a1}^{1}$ . The output voltage will be 0 by turning  $S_{a1}$  and  $S_{a2}$  switches or  $S_{a1}^{-1}$  and  $S_{a2}$  switches. If m is assumed as the number of modules connected in series, then the number of output levels n in each phase is given by equation (1). The switching states of a CHB-MLI can be determined by using equation (2)

$$n = 2m + 1$$

$$sw = 3^n$$

(2)The first leg phase voltage (Van) is constituted by multiplying Val and Va2 values of series connected Hwww.ijirset.com

Copyright to IJIRSET

bridge cells and will generate a stepped waveform. The fourier series expansion of the general multilevel stepped output voltage is shown in equation (3) and transform is applied in equation (4), where H is the harmonic number of the output voltage of inverter. The switching angles that are indicated as  $\alpha 1 \dots \alpha 5$ , in equation (3) can be chosen to obtain minimum voltage harmonics and several fundamental frequency switching techniques have been evaluated such as selective harmonic elimination PWM or active harmonic elimination PWM.

$$(\omega t) = \frac{4Vdc}{\pi} \sum_{\substack{H=1,3,5,\dots\\H=1,3,5,\dots\\H=1}}^{\infty} (\cos(H\alpha_1) + \cos(H\alpha_2) + \dots + \cos(H\alpha_5)) \sin \frac{(H\omega t)}{H}$$

(3)

$$V(\omega t) = \frac{4Vdc}{\pi} \sum_{H=1,3,5,\dots}^{\infty} \left(\cos(H\alpha_1) + \cos(H\alpha_2)\right) \sin\frac{(H\omega t)}{H}$$

(4)

The modulation index is defined as M.I. can be calculated as in equation (5)  $M.I. = \frac{(\pi V_1)}{2}$

$$4V_{dc}$$

(5)

Since, the values of Eq. (4) are non-linear, the calculations are obtained by using Newton-Raphson Iteration.

#### III. CARRIER BASED DISPOSITION PWM METHOD

Carrier based disposition PWM methods were first proposed by Carrara et al[2]. For an n-level inverter, n-1 carriers with the same frequency  $f_c$  and the same amplitude A<sub>c</sub>are disposed such that the bands they occupy are contiguous. The reference waveform has maximum amplitude  $A_m$ , a frequency  $f_m$ , and its zero centered in the middle of the carrier set. The reference is continuously compared with each of the carrier signals. If the reference is greater than a carrier signal, then the IGBT corresponding to that carrier is switched on and if the reference is less than a carrier signal, then the IGBT corresponding to that carrier is switched off [3].

Previous works on PWM techniques shows that disposition technique for diode clamped and PSCPWM for cascaded inverter five rises to same harmonic profile for the same number of total switch transition. Hence these techniques can be efficiently applied for Diode Clamped and Cascaded Multilevel Inverter.

Carrier Disposition method arrange N-1 carrier waveform of same amplitude and frequency in continuous bands to fully occupy the linear modulation range of the inverter. The reference or modulating wave is positioned at the center of the carrier set, and continuously compared with the carriers to obtain the necessary gating pulses [3].

(1)

In multilevel inverters, the amplitude modulation index (M.I.) is the ratio of reference amplitude ( $R_a$ ) to carrier amplitude ( $C_a$ ). M.I. =  $R_a / (m-1)C_a$

$$\mathbf{M} = \mathbf{R}_a / (\mathbf{M}^{-1}) \mathbf{C}_a \tag{4}$$

The frequency ratio ( $R_f$ ) is ratio of carrier frequency ( $f_c$ ) to reference frequency ( $f_r$ ).  $R_f = F_c/F_r$ .

# IV. SIMULATION RESULTS

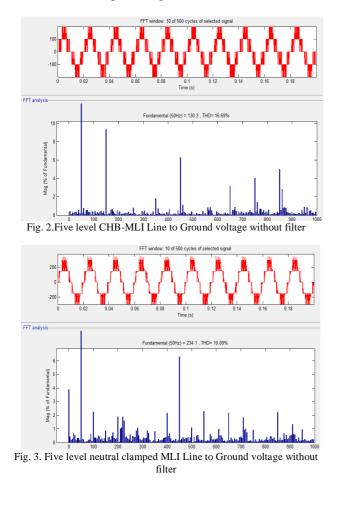

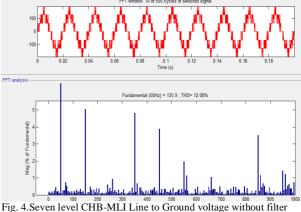

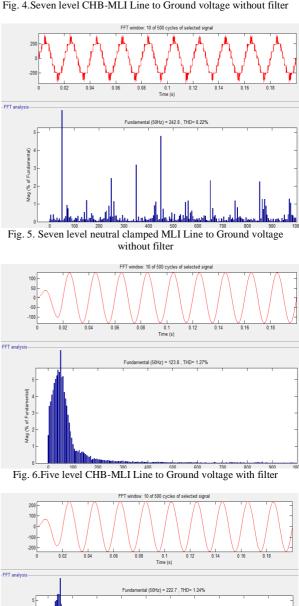

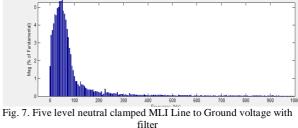

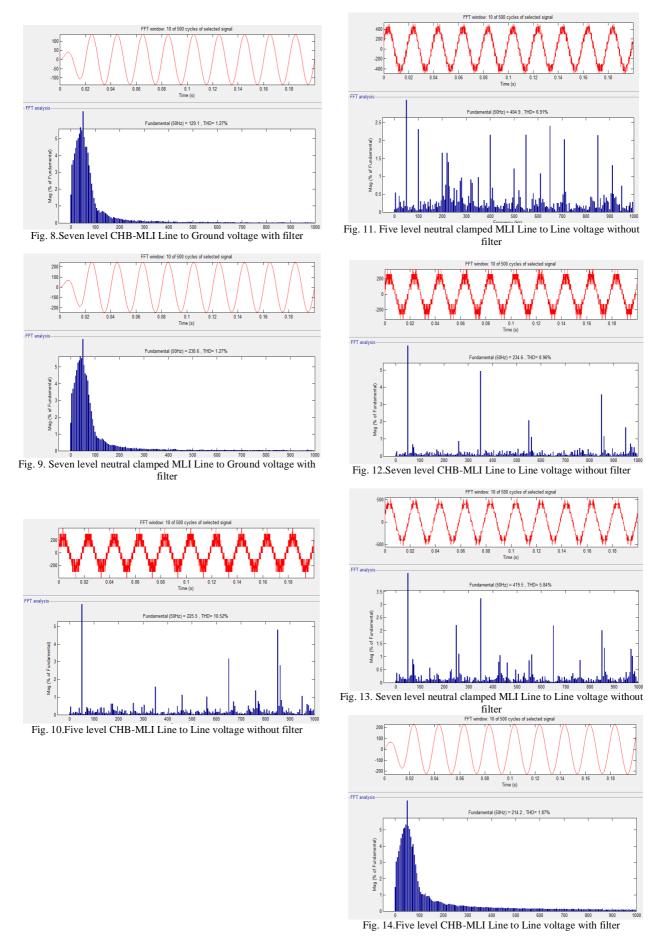

The SPWM for the three-phase five level & seven level CHB-MLI &Neutral clamped MLI is implemented on a MATLAB SIMULINK model. The simulated results for five & seven level are compared for different modulation indexes with the input voltage 600V.

Copyright to IJIRSET

www.ijirset.com

# Performance Analysis of VLSI based Multilevel Inverter

Copyright to IJIRSET

www.ijirset.com

M.R. Thansekhar and N. Balaji (Eds.): ICIET'14

## Performance Analysis of VLSI based Multilevel Inverter

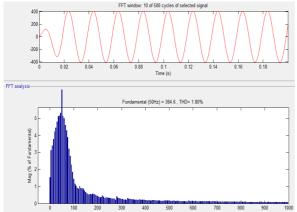

tal (50Hz) = 398.6 , THD= 1.71%

Fig. 15. Five level neutral clamped MLI Line to Line voltage with filter.

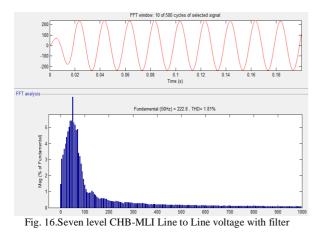

Fig. 17. Seven level neutral clamped MLI Line to Line voltage with filter

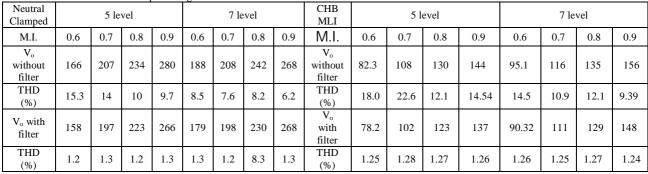

# Table 1: Output voltages & %THD for different modulation index

# VI. CONCLUSION

The neutral clamped and cascaded 3-phase 5 & 7 has been designed and simulated in *MATLAB* / *Simulink* environment With SPWM for different modulation index & results are tabulated in this paper. From the result as shown in the table we can conclude that as we increase the modulation index THD reduces and voltage performance reduces for both 5 level and 7 level inverter

#### REFERENCES

- [1] Muhammad H. Rashid. Power Electronics Circuits, Devices and Applications, third edition 2013.

- [2] G. Carrara, S. Gardella, M. Marchesoni, R. Salutari, G. Sciutto, "A New MultilevelPWM Method: A Theoretical Analysis," *IEEE Transactions on Power Electronics, vol. 7, no. 3, July 1992, pp. 497-505.*

- [3] Leon M.Tolbert and Thomas G. Habetler "Novelmultilevel inverter carrier based PWM method" *IEEE Transaction On Industry Application Vol 35. No 5 Sep 1999 pp 1098-1107.*

- [4] D.G Holmes and "Multi carrier PWM strategies for multilevel inverter" *IEEE Transaction on Industrial Electronics, Volume 49, Issue 4, Aug 2002, pp 858-867.*

Copyright to IJIRSET

www.ijirset.com

M.R. Thansekhar and N. Balaji (Eds.): ICIET'14

- [5] M. A. Saqib and S. A. R. Kashif, "Artificial Neural Network Based Space Vector PWM for a Five-Level Diode-Clamped Inverter," *AUPEC*, 2010.

- [6] G.Durgasukumar and M.K.Pathak, "THD Reduction Performance of Multi-Level Inverter fed Induction Motor Drive," *IICPC*, 2011.