(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

# Dual AGC Model Implementation of the Inner Hair Cell and Auditory Nerve IC in Neuromorphic VLSI

Dr.J.Raja, Saranya.SA ,Suresh Babu.T.N

Professor, Department of ECE, Adhiparasakthi Engineering College, Melmaruvathur, Tamil Nadu, India.

PG Student (VLSI Design), Department of ECE, Adhiparasakthi Engineering College, Melmaruvathur, Tamil Nadu,

### India

Assistant Professor, Department of ECE, Adhiparasakthi Engineering College, Melmaruvathur, Tamil Nadu, India

**ABSTRACT-**An analog inner hair cell and auditory nerve has been implemented for the persons with hearing disabilities. The designed circuit uses fully balanced circuits to reduce the mismatch of the signals that enters through the hearing aid. Ultra low power consumption of the circuit in the machine save the battery life to be used for years. CMOS current mode is being implemented to the computationally developing hearing aid IC. The designed IC can be used to obtain a result in spectrogram by measuring the frequencies from articulogram in future. The power consumption of the circuit is reduced dramatically.

**KEYWORDS**: Auditory Nerve ,dual AGC model Biomimetics, Inner hair cell, Neuromorphic, Very Large Scale Integration (VLSI), Hearing Aid.

### I. INTRODUCTION

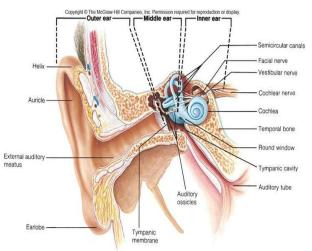

Neuromorphic aims for the increased performance of the analog electronic circuit and for the artificial intelligence like robotics, smartphones, nano technology etc., the growing technology results in advances in minimutrized systems and also nano systems where the tie up between both is power. Power consumption has become the thrist for the modern technology. In biomedical VLSI plays the major role for developing instruments for major and minor operations. Medical applicances like octolography ,electroenceplography, electro cardiogram measures the signals obtained for the patients, the signals whose frequencies are measured through medical devices to obtain the result. An analogue VLSI is adapted to implement in inner hair cell and auditory nerve.Normally human ear consist of outer hair cell(OHC),inner hair cell (IHC) and middle hair cell, the damage of inner hair growth but this cause serious injury. Cochlear implants are to make the disabilities to hear the sound in environment directly without earing aid ,perhaps implanting artificial cochlea produces waxy substances in the ear, these are done in order to have spotless hearing aid. The human ear is a highly sensitive sound receptor in which pressure fluctations in the outer ear are transformed into vibrations of small bones (the ossicles) in the middle ear that are ultimately communicated to the cochlea located in the inner ear ,where the vibrations are further transformed by stereocillia (hair cells) into neural impulses distributed by frequency.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

Fig .1 represents the anatomy of human ear showing the divisions in Hair cells which causes neurotransmitter to stmulate neuron in auditory nerve which sends the impluses to the brain.

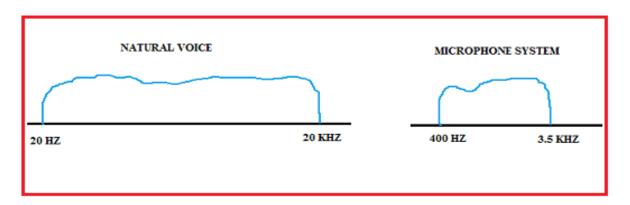

Natural human voice spans a frequency range from 20Hz to 20KHz, however conventional microphone system passes frequencies from 400Hz to 3.5KHz. Therefore phone conversation differs from face-to-face conversation and also the heared by the deaf.

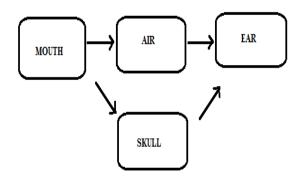

Fig.2 represents the sound produced, passes through the mouth to the skull and to the ear, which corresponds to the normal hearing of a person.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

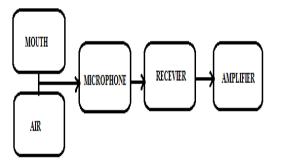

Fig.3 shows the representation of the sound waves picked up by the microphone and it converts to them into electrical energy it is then delivered the receiver which changes the electrical energy and alters the amplification process here involves the boosting up electrical energy inside the machine the filtering is done for clear speech.

Fig 4. Human voice spans a frequency range from 20Hz to 20KHz, however conventional telephone system.

### THRESHOLD OF HEARING

The threshold pressure level of a sound is the lowest level at which an observer can discriminate between the desired sound and the noise background always present in the auditory system. The base of each audio logical examination is the determination of the hearing threshold. It is necessary to know whether the hearing lossis due to disorder of the hearing organ (cochlea) and connecting nerves with the brain(perceptive loss) or the loss because of reduced transmission of sound vibrations through the middle ear mechanism (conductive loss).

### **MEASUREMENT OF SOUND**

Sound intensity is the amount of energy flow per unit time through a unit area perpendicular to the direction of energy flow. The common receivers are microphones which do not measure sound intensity directly. They are sensitive to sound pressure therefore it is pertinent to measure the sound in terms of sound pressure. Sound pressure is related to both amplitude and frequency and sound intensity is proportional to the square of sound pressure. The convenient way for expressing sound pressure and sound intensity in terms of decibel.

### II. CURRENT MODE IMPLEMENTATION

The hearing aid consisting the integrated chip which should be used for a period of years with less consumption of power which can be achieved by Very Large Scale integration (VLSI).

### HIGH SPEED DIGITAL SIGNAL PROCESSING

The chip designed controls the level of noise. The digital chip was integrated into number of hearing aid with high

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 2, February 2015

speed signal processing or DSP. The acoustic signals are sent to signal processing chips to be implemented into the hearing aids. These integrated circuits were produced in hearing aids. One of the major contributions of these chips was the ability to process both speech and other types of noises in real time application. One major down fall of these chips was that they were massive and used up a lot of battery, which made them to nearly impossible to be worn and thus the use of CMOS technology to minimize the consumption of power.

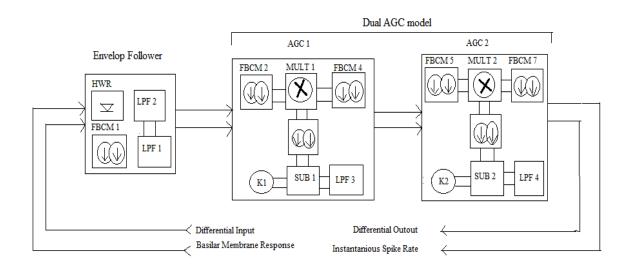

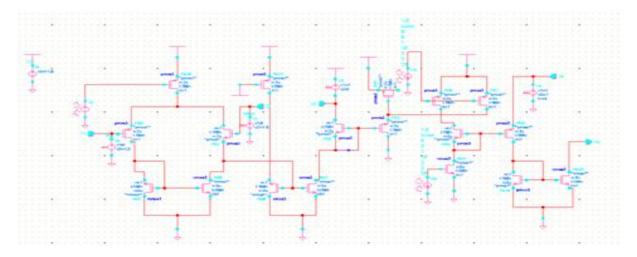

Fig.5Dual AGC Model in AIHCAN Design.

The above fig 5 shows the process of mammalian hear working, the envelope follower consists of half wave rectifier this is buffered with fully balanced current mirror. The function of fully balanced circuit for the is to act as a buffer. The buffered signal enters the next two stages in the dual AGC model. Low pass filtering here filters the unwanted noise. The dual AGC model receives the incoming signal and amplifies the sound that enters the ear. The FBCM provides impedance matching for both multiplier and low pass filter. Reference current level are  $K_1$  and  $K_2$  are provided by the subtraction which the filtered signal is compared with the normal speech. In hearing aid the circuit IHC and AN changes the intensity of the sounds magnitude of 120 dB in sound pressure level. The dynamic response of the IHC circuit separates the binaural cues from the noisy environment. The alternative IHC is designed in dual AGC model. The model does the working of the normal human ear does of amplification, the hair cells remain unvibrated the sound entering simulates the hair cells generating ion channels within the hair cells. The transconductance of the vibrated cells changes as the input sound changes.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

### III. FULLY BALANCED CURRENT MIRROR

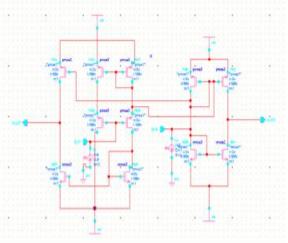

Fig 6 Fully balanced current mirror

The above Fig.6shows, FBCM consisting of two halves, positive and negative it is composed of Wilson current mirror whose output is given to the complementary current mirror. With a low supply voltage of 1.8V,keeping current 1 (I  $_{inN}$ ) as low as 0 and current 2 (I  $_{inP}$ ) as high, keeping the gain to be one. The transistors used in this design, allows consumption of power to be reduced. The collector current does not remain constant with variation in temperature or constant. 'S' should be small as possible to have better stability. The parametric analysis for the capacitor, this analysis helps to choose the exact value for the parameter here the value is choosen as C=3.258pf in order to obtain the stabilized output current for the circuit. The collector current does not remain constant with variation in temperature or power supply voltage. Therefore the operating point will be unstable.

### **CMOS CURRENT MIRROR**

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

STABILITY

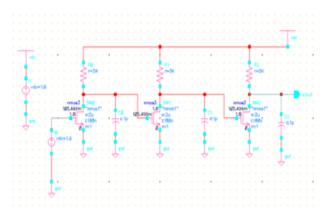

Fig 7.The collector current  $I_c$  is stabilized with varying  $I_{co}$  and is measured by stability factor (S). It is defined as the rate of change of collector current to the in  $I_{co}$ , keeping the bias current and B as constant current for the circuit.

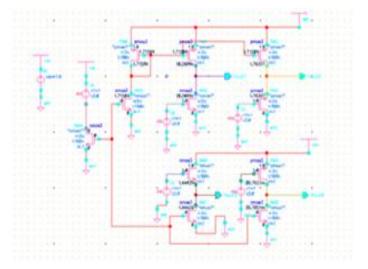

Fig 8.shows the CMOS current mirror allows the combination of both PMOS and NMOS, this circuit is used in inner hair cell circuit because it rectifies the signal before passing it through the filter. This adaptation has been modelled in but it was considered too complex and too large for inclusion on the current chip of IHC. The analog and digital circuits run on separate power supplies to reduce digital noise and the analog signals. However the proposed IHC with current mirror has overcome this problem and this circuit is intended to include in future versions.

Fig 9..The above shown the Inner Hair Cell circuit is designed for the hearing aid for the disabilities. The adjusted bias voltage is fed to the input frequency .The leakage current is kept as lowered level, the voltage  $V_1$  is kept at 0 and  $V_2$  as 1.8V.The inner hair cell circuit is followed by a current level, this rectifies the signal by passing it through LPF.Normally the spike rate of a neuron circuit is limited to 100 spike rates per second.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

### V. SIMULATION AND RESULTS

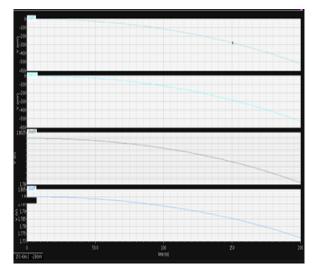

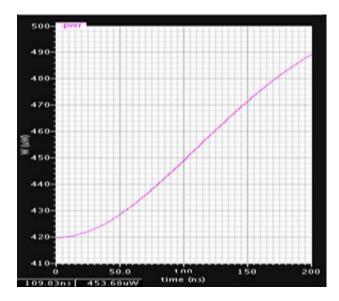

Fig 10.shows the FBCM output explains the transient response with the metal width chooses at 400nW,

and the circuitresponse becomes nonlinear when the input exceeds 1.8A and the output s connected to a  $100k\Omega$  load. The transistor dimensions were optimized forminimizing the area mismatch without significant concern for the DC operating point within the limits. Thus, the PMOS and NMOS dimensions have a equal widths and lengths, assuring their transconductance would be different. The output wave obtained is smaller than the input given thereby the power of the existing FBCM is 122Nw

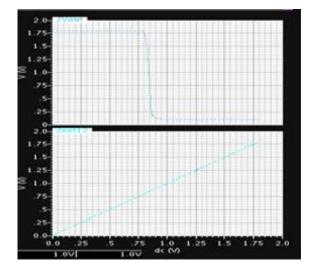

Fig11. IHCThe output of IHC is shown in the Fig 4.15 in which  $V_1$  is set as 0 and  $V_2$  is given 2v the output is obtained at the level of 2v it decreases, thereby reducing the power consumption of the circuit.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

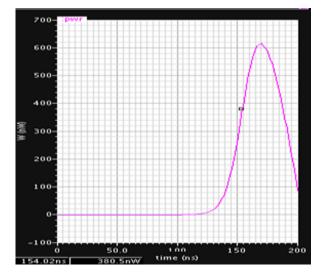

Fig 12.FBCM powerThe power wave is obtained for modified FBCM, shown in Figure 4.19 which implies the decrease in power dramatically after a sudden rise, thus this modified circuit uses less power to be used.

Fig 13.IHC powerTheoutput of IHC is shown in the Fig 4.15 in which  $V_1$  is set as 0 and  $V_2$  is given 2v the output is obtained at the level of 2v it decreases, thereby reducing the power consumption of the circuit.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

Fig 14.shows the DC response output of stability circuit the input range is set between 0V and 1.8V the output is obtained for at 1.75V and gradually decreases and remains constant.

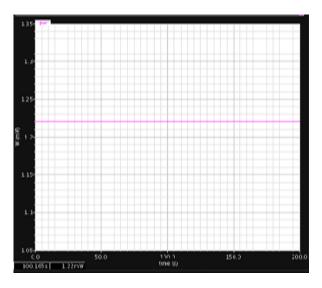

Fig 15.shows the design of current mirror major requirement is the stability shows the power wave and its average power consumption for which the choosen parameter and the DCresponse is obtained for 1.8V. The stability factor (S) should be kept small.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

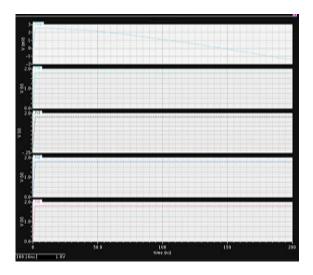

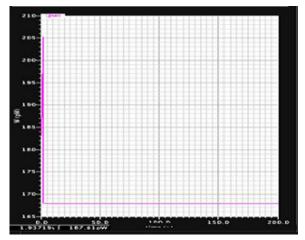

Fig 16.shows the power wave obtained for CMOS current mirror which is combined in IHC circuit to reduce the common mode signals,

thus both the combination increases the circuit complexity and power. The power wave rises to a particular level of 2W and reduces at 1.6W. This circuit when combined with IHC increases power.

| Table Window (XL) |                       |         |

|-------------------|-----------------------|---------|

| s <u>H</u> elp    |                       | cādence |

|                   |                       |         |

| average(g         | average(g             |         |

| 450.7E-6          | 450.7E-6              |         |

| 450.7E-6          | 450.7E-6              |         |

|                   | average(g<br>450.7E-6 |         |

Fig 17.shows the power response obtained in which, due to the circuit complexity the power consumed by the entire circuit is obtained to be higher. The modified IHC circuit designed in analog cadence virtuoso will results in reduced power.

|                      |                 | Table Window (XL) | _ = ×   |

|----------------------|-----------------|-------------------|---------|

| ile ⊻iew <u>T</u> oo | ls <u>H</u> elp |                   | cādence |

| 5                    |                 |                   |         |

| Name (unk 🗵          | average(g       | average(g         |         |

|                      | 0 122.3€-9      |                   |         |

| 10.00                | 122.3£-9        | 122.3E-9          |         |

Fig 18.shows the power analysis of fully balanced circuit and the power wave form gives the value of peak and average power.Hence for the proposed model we'll be able to reduce the number of components which results in reduced power and area.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 2, February 2015

| *                               | ) – 09         |                |         |

|---------------------------------|----------------|----------------|---------|

| <u>F</u> ile ⊻iew <u>T</u> ools | <u>H</u> elp   |                | cādence |

| 9                               |                |                |         |

| Name (unk 🛽                     | average(getDat | average(getDat |         |

| 1.000                           | 62.31E-9       | 62.31E-9       |         |

| 10.00                           | 62.31E-9       | 62.31E-9       |         |

Fig 19. The power of modified FBCM is shown in Figure 4.20 which reveals the power reduction for DCcurrent to be 1.8A.The average power is obtained by selecting the output wave.

| <u>File View Tools</u> | ile <u>V</u> iew <u>T</u> ools <u>H</u> elp |                |  |

|------------------------|---------------------------------------------|----------------|--|

| 8                      |                                             |                |  |

| Name (unk 🗵            | average(getDat                              | average(getDat |  |

| 1.000                  | 447.1E-6                                    | 447.1E-6       |  |

| 10.00                  | 447.1E-6                                    | 447.1E-6       |  |

Fig 20.shows the output almost reduces the level that is proportional to the magnitude of (Vc1-Vc2). The obtained current drives an integrate and fire neuron in the circuit with the power reduction.

| PARAMETER          | EXISTING FBCM | PROPOSED IHC | EXISTING FBCM | PROPOSED FBCM |

|--------------------|---------------|--------------|---------------|---------------|

| No. of Transistors | 14            | 25           | 11            | 20            |

| Average Power      | 122mW         | 450nW        | 62mW          | 447nW         |

Table-I shows that the proposed FBCM and IHCcircuit achieves low power consumption at a low supply voltage of 1.8V which can be used for low power biomimetic applications.

### VI. CONCLUSION

The designed IHC circuit and FBCM is used as a buffer circuit in the chip designed for the hearing aid. Power consumption is the major requirement of the electronic circuit designed in this modern technology. An analog VLSI implementation of the dual AGC model which performs the function as the normal human ear is developed as a chip to place in the ear machine for the person with hearing disabilities this is used inmonaural cue, binaural cue, or multiple binaural systems. Using current-mode circuits the ability totune the system to remove the CMOS mismatch is achieved. Theseresults have been evaluated and established by analog CADENCE Virtuoso environment. The circuits are designed to obtain the power analysis, andto be applied in low-power envelope, real-time processing. And the behavior of flexibility from various levels make the AIHCAN IC a practical module for use in biomimetic processing, especially in smart phones ,battery powered applications and biological systems where the AIHCAN IC can be easily integrated into existing and future systems.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 2, February 2015

#### REFERENCES

David.S Freedman, *Member, IEEE*, Howard I. CohenSocrates Deligeorges, Christian Karl, and Allyn E.Hubbard "An analog VLSI implementation of inner hair cell and auditory nerve using dual AGC model" *IEEE Trans.Biomed.CircuitsSyst.,vol.5,no.4,pp.240-256,2014* K. H. Wee, L. Turicchia, and R. Sarpeshkar, "An articulatory silicon vocal tract for speech and hearing prostheses," *IEEE Trans.*

Biomed.CircuitsSyst., vol. 5, no. 4, pp. 339–346, 2011

[3] A. Hubbard, H. Cohen, C. Karl, D. Freedman, D. Mountain, L.Ziph-Schatzberg, M. Nourzad Karl, S. Kelsall, T. Gore, Y. Pu,Z. Yang, X. Xing, and S.Deligeorges, "Biologically inspired circuitry that mimics mammalian hearing," in *Proc. SPIEConf.Ser.*, 2009, vol.7321.

[4]Y. Shao, Z. Jin, D. Wang, and S.Srinivasan, "An auditory-based feature for robust speech recognition," in *Proc. IEEE Int. Conf.Acoustics,Speech, and Signal Processing, 2009, pp. 4625–4628.*

[5] V. Chan, S.-C. Liu, and A. van Schaik, "AER EAR: A matched silicon cochlea pair with address event representation interface," *IEEETrans. Circuits Syst. I, Reg. Papers, vol. 54, no. 1, pp. 48–59, 2007.*

[6] R. Sarpeshkar, C. Salthouse, J.-J. Sit, M. Baker, S. Zhak, T.-T. Lu, L.Turicchia, and S. Balster, "An ultra-low-power programmable analog bionic ear processor," *IEEE Trans. Biomed. Eng.*, vol. 52, no.4, pp.711–727,2005

[7]M. Baker and R. Sarpeshkar, "Low-power single-loop and dual-loopAGCs for bionic ears," *IEEE J. Solid-State Circuits*, vol. 41, no. 9, pp.1983–1996, 2006.

[8] A. Hubbard, H. I. Cohen, S. Deligeorges, D. Freedman, T. Gore, C. Karl, S. Kelsall, M. Nourzad, Y. Pu, and S. Xue, "Miniaturization of

electronics for a biomimetic acoustic direction finding system for use on multiple platforms," in Proc. SPIE Conf. Ser., 2008, vol. 6963.

[9] F. L. Wightman and D. J. Kistler, "The dominant role of low-frequency interaural time differences in sound localization," J. Acoust. Soc. Amer., vol. 91, no. 3, pp. 1648–1661, 1992.

[10] L. A. Jeffress, "A place theory of sound localization," J. Compar Physiol. Psychol., vol. 41, no. 1, pp. 35–39, 1948.

[11] S. T. Birchfield and R. Gangishetty, "Acoustic localization by interaural level difference," in *Proc. IEEE Int. Conf. Acoustics, Speech, Signal and Processing*, 2005.

[12] J. Weng and K. Y. Guentchev, "Three-dimensional sound localization from a compact non-coplanar array of microphones using tree-based learning," J. Acoust. Soc. Amer., vol. 110, no. 1, pp. 310–323, 2001.