(An ISO 3297: 2007 Certified Organization) Vol. 4, Special Issue 6, May 2015

# Performance Analysis of Digital Circuits Device under Test at Different FPGA Families

T.S Muralirajan<sup>1</sup>, P.SaravanaKumar<sup>2</sup>, S.Parvathi<sup>3</sup>, K.Somu<sup>4</sup>S.Saravanan<sup>5</sup>

P.G. Student, Department of ECE, Maha Barathi Engineering College, Chinnasalem, Tamil Nadu , India<sup>1</sup>

Assistant Professor, Department of ECE, Maha Barathi Engineering College, Chinnasalem, Tamil Nadu, India<sup>2</sup>

Assistant Professor, Department of CSE, SKP Engineering College, Tiruvannamalai, Tamil Nadu, India<sup>3</sup>

Assistant Professor, Department of ECE, Maha Barathi Engineering College, Chinnasalem, Tamil Nadu, India<sup>4</sup>

Professor and Head, Department of EEE, Muthayammal Engineering College, Rasipuram, Tamilnadu, India <sup>5</sup>

**ABSTRACT:** Despite their tremendous success over the years, the Digital circuits are still confronted with some of the critical challenges such as, manufacture, maintenance, and repair. To fulfill this, digital integrated circuits industry defined an Integrated Automatic test generation (ATG) / Automatic Test Equipment System for complex boards / circuits, which comprises Low Cost, Reconfigurable and easy to use digital circuits. It allows circuit parameters to be extracted from HDL Simulation then functionality is verified by using Xilinx Environment. The aim is to develop an ATG technique called Behavior - Based Automatic Test Generation technique (BBATG), where the system uses the structural model to describe circuit board as an interconnection of devices. Thus application of a deterministic algorithm to deduce the tests for complex circuit boards. Unlike most other deterministic ATG using the stuck-atfault model, BBATG use the device behavior fault model which can completely describe functions and pin timing relations for a combination or sequence device, and then needn't decompose devices to gate-level descriptions. The objective of the functional testing is to validate the correct operation of the system with respect to its functional specifications. Functional Testing is carried out for a small number of vector combinations. The main focus is based on easy-to-use and reconfigurable automatic test machine referred as FATE (FPGA-based ATE). So the test generation for digital circuits with VLSI can be further simplified and optimized. The designed FATE is verified with and without fault using Xilinx software and result are included.

**KEYWORDS:** ATG, BBATG, Xilinx software, FATE.

### I. INTRODUCTION

Testing in its broadest sense means to examine a product and to ensure that it functions and exhibits the properties and capabilities that it was designed to possess. Main purpose of testing is to detect malfunctions in the product hardware and to locate their causes so that they may be eliminated. Conventional Test Methods rely primarily on mechanical means and not on use of additional circuits in an OTBT for the purpose of facilitating its testing. Example: Including extra I/O for additional test points, improvement of test features.

The Basic characteristics of conventional methods are used for testing system parts only outside the system, Rely on feeding signals directly through the test interface during listing and Rely on the use of tester-driven timing. Some of the Difficulties in Testing's are Shortage of I/O points, Signal distortions in interface connection, Noise disturbances, Uncertainties in input feeding, Uncertainties in output sensing. (Rejection of good parts reduces apparent yield.), Difficulty in synchronizing test objects timing with tester timing, High costs for test equipment, test generation and execution, and Large volume of data to be processed.

### FAULT DIAGNOSIS SYSTEM

The VLSI circuit manufacturer cannot guarantee the defect- free integrated circuits(IC's). This makes to evolve a fast accurate means of testing such circuits. In a small-scale environment, it may not be feasible to invest large sums of money into complex IC testers. In labs till now Digital testers which will test IC's based on some non-functional

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

parameters like temperature, any short circuits in the IC etc. & are used for testing only Combinational circuits. The digital pattern generator and logic analyzer are used to test the combinational, sequential circuits.

Automatic Test Equipment is a test setup used to detect and diagnose the faults of any DUT (Device under Test). ATE technology has evolved considerably over the years, matching the diagnostic test requirements of advancing avionics. ASIC manufacturers generally resort to the companies when chip development phase has been resolved and an accurate digital test program is ready to be executed by the high-end commercial ATEs [3].

A versatile but inexpensive, testing system for standard digital IC's (7400-series transistor-transistor logic (TTL) based on the use of a FPGA is ATE (Automatic Test Equipment). This tester can be economically implemented for small or medium-scale users of such IC's & provides a quick but thorough checkout of most small & medium-scale functions with minimal operator action. Dedicated special-purpose hardware is minimal, allowing this tester to be implemented on virtually FPGA. Each IC is tested by applying test patterns to input pins of the chip & the resulting chip outputs are then examined for errors resulting from the stuck-at conditions or other functional errors. For Dedicated ATE, all input & output patterns are compacted and stored in a data base and are compared with the expected outputs. For Generalized ATE, the DUT output can be stored in the Logic analyzer& user need to check the functionality based on the input & output results. This ATE can be used to test the combinational and sequential circuits.

The test set for each IC is an exhaustive set of all possible input combinations; this ATE is used for SSI & MSI functions. Earlier the digital IC testers are implemented using Intel micro-processor family. Test patterns are applied to each IC to be tested from a lookup table stored in the memory. Along with appropriate clock signals if needed. Reconfigurable logic device has programmable interconnects so that user can realize desired function in it.

It is also called programmable logic device (PLD) or field programmable gate array (FPGA). Recently logic capacity of PLD becomes large enough to realize various data processing functions within it. Although PLD's performance is not as high as ASIC when it is designed for the same application, its re-programmability has advantages & many applications are proposed. PLD system can be over 100 times faster than processor based system for applications with high parallelism.

Two main categories of ATE machines are available nowadays on the market: high-end ATE and low-cost ATE. High-end ATEs are characterized by high grade of automation, digital and analogy test capability, high-current pin protections and high-speed test execution [2]. On the other hand they are very expensive and require an accurate setup and skilled people, so ASIC manufacturers also needs some other testing solution, which can be executed in house during preliminary chip evaluation phase, when the use of an aforementioned ATE should be unnecessary in terms of time and money. In last decade, beside this range of performing ATE machines low-cost ATEs took place in market.

The main focus is based on easy-to-use and reconfigurable automatic test machine referred as FATE (FPGAbased ATE) .The FPGA is very versatile thus allows us to realize a home-made low-cost ATE to check for the functional correctness of the circuit. Many VLSI designers propose into market various kinds of quick, flexible and feature-rich development boards featuring various sized FPGA.

### **II. PROBLEM DEFINITION**

To develop an efficient test generation method for digital integrated circuits having reduced test generation complexity, high fault coverage and low test application time. Test generation technique is based on the Behavior-Based Automatic Test Generation technique (namely BBATG) should generates behavioral based faults. To perform device tests and yield analysis on their desktop and then transfer the test program directly to FPGA-based ATE (FATE) System.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

#### **BLOCK DIAGRAM**

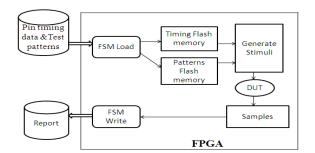

The block diagram of the proposed system shown in Fig 1 consists of Test pattern generation, FSM Load/Write, Generation of Stimulus, Loading data in Flash Memory and Report generation.

Fig 1: Block Diagram of Proposed System

#### **BBATG TECHNIQUE**

The three main components behind the BBATG technique are behavior-based device model, set of reusable device test libraries and automatic test deduction algorithm.

Circuit board model: A circuit board is defined as a system of an interconnection of components. In such a structural model, devices are at the lowest level and consequently are considered as primitive components.

Device model: A device is defined as a black box whose behaviours can be represented by the relationship between its inputs and outputs. Accordingly a device's behaviour model is described as its functional representation with the associated timing relations between the inputs and outputs.

Device Behaviour fault model: A device has a behaviour fault when its behaviour fails. In system test deductions, we only review device behaviour faults. Wire faults between individual devices in a system are attributed as faults at the connecting devices. In order to detect and diagnose fan-in/fan-out faults at system initial input/output pins, users can treat each system connector interface as one device so that wire faults are converted to device faults.

Test pattern generation technique makes use of Behaviour- Based Automatic Test Generation technique (BBATG). In BBATG, a behaviour error signal is presented as an "H" or "L". "H" represents "1" when the signal is normal and "0" when fault; "L" implies "0" when the signal is normal and "1" when fault.

### **III. RESULTS AND DISCUSSION**

### SIMULATION

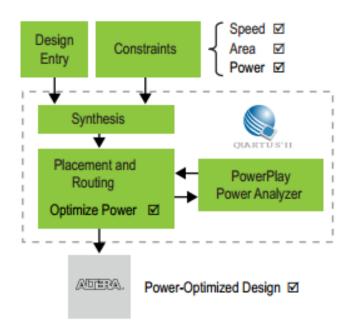

It can perform the functional and timing simulation of your design with the ModelSim®-Altera Edition software, or any EDA simulators supported by Quartus II software. The Quartus II NativeLink feature allows you to run your third-party simulator and other EDA tools from within Quartus II software.

### POITR PLAY ANALYZER FLOW

The Quartus II Poitr Play poitr analysis and optimization tools allow you to estimate poitr consumption throughout the design cycle. They use poitr optimization technology, which provides on average a 10-percent reduction in poitr consumption. The Altera Poitr Play Early Poitr Estimator estimate poitr consumption and produces a Microsoft Excel-based spreadsheet with estimate information. The Poitr Play poitr analyzer performs post-fitting poitr analysis and reports poitr characteristics by device resource and design entity.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

Fig2: Flow of Poitr Estimation.

### **OUTPUT SCREENSHOTS**

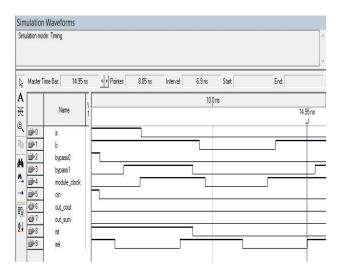

The Simulation Output without fault is observed as '0' for out sum and out\_cout for the given inputs on the, b,  $c_{in}$ , sel, rst pin the output is processed from the flip flops, full adder and multiplexer.

Fig 3: Simulation Waveforms

The Fig 3 shown above is based on the parameter that is free from fault, in which the fault parameters are based timing delay and behavioural i.e., Boolean function of any digital circuits used.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

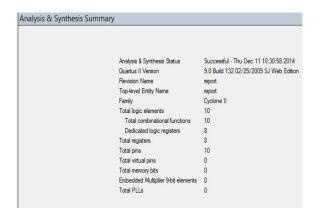

Fig4: Analysis and Synthesis Summary.

|    | Compilation Hierarchy<br>Node | LC<br>Combinationals | LC<br>Registers | Memory<br>Bits | DSP<br>Elements | DSP<br>9x9 | DSP<br>18x18 | Pins | Virtual<br>Pins |                      | Library<br>Name |

|----|-------------------------------|----------------------|-----------------|----------------|-----------------|------------|--------------|------|-----------------|----------------------|-----------------|

| 1  | 🗄  report                     | 10 (0)               | 8 (0)           | 0              | 0               | 0          | 0            | 10   | 0               | report               | work            |

| 2  | ft.ff1                        | 1 (1)                | 1(1)            | 0              | 0               | 0          | 0            | 0    | 0               | (report)ff:ff1       | work            |

| 3  | - (ff.ff2)                    | 1 (1)                | 1 (1)           | 0              | 0               | 0          | 0            | 0    | 0               | report ff:ff2        | work            |

| 4  | - (ff.ff3)                    | 1 (1)                | 1 (1)           | 0              | 0               | 0          | 0            | O    | 0               | (report)ff:ff3       | work            |

| 5  | -  ft.ff4                     | 1 (1)                | 1 (1)           | 0              | 0               | 0          | 0            | 0    | 0               | (report)ff:ff4       | work            |

| 6  | - (ff.ff5)                    | 1 (1)                | 1 (1)           | 0              | 0               | 0          | 0            | 0    | 0               | report ff:ff5        | work            |

| 7  | - (if:ff6)                    | 1 (1)                | 1 (1)           | 0              | 0               | 0          | 0            | 0    | 0               | report ff:ff6        | work            |

| 8  | - (f£ff7)                     | 1 (1)                | 1 (1)           | 0              | 0               | 0          | 0            | 0    | 0               | (report)ff:ff7       | work            |

| 9  | - (řf. ff8)                   | 2 (2)                | 1 (1)           | 0              | 0               | 0          | 0            | 0    | 0               | (report)/fr:ff8      | work            |

| 10 | full_addenfa                  | 1(1)                 | 0 (0)           | 0              | 0               | 0          | 0            | 0    | 0               | reportifull adder.fa | work            |

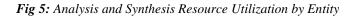

The Figure 4, 5 shows the Internal Analysis and Synthesis for the DUT. It may obtain this state by applying the Analysis and Synthesis View Section once again and it may verify the Device Components which are taken as DUT.

|         | Туре                        | Value       |  |  |  |

|---------|-----------------------------|-------------|--|--|--|

| 1       | Simulation Start Time       | 0 ps        |  |  |  |

| 2       | Simulation End Time         | 1.0 us      |  |  |  |

| 2       | Simulation Netlist Size     | 29 nodes    |  |  |  |

| 4       | Simulation Coverage         | 100.00 %    |  |  |  |

| 4 5 6 7 | Total Number of Transitions | 5495        |  |  |  |

| 6       | Simulation Breakpoints      | 0           |  |  |  |

| 7       | Family                      | Cyclone II  |  |  |  |

| 8       | Device                      | EP2C5T144C6 |  |  |  |

Fig 6: Simulator Summary

The Figure 6 shows the Simulator Summary for the DUT. It may obtain this state by applying the Simulator Summary View Section once again and It may verify the Device Components which are included as DUT where each element consumption of simulation start time, end time, net list size, coverage, total number of transitions and device.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

|   | Type                         | Slack | Required<br>Time | Áctual<br>Time                               | From     | To       | From<br>Clock | To<br>Clock  | Failed<br>Paths |

|---|------------------------------|-------|------------------|----------------------------------------------|----------|----------|---------------|--------------|-----------------|

| 1 | Worst-case tsu               | NA    | None             | 4.147 rs                                     | bypassQ  | ftflþ    |               | module_clock | Î               |

| 2 | Worst-case too               | NA    | None             | 8.142 rs                                     | ff:1181q | out_cout | module_clock  |              | 0               |

| 3 | Worst-case th                | NA    | None             | 0.775 ns                                     | c'n      | 11.115)q |               | module_clock | 0               |

| 4 | Clock Setup: 'module_clock'  | N/A   | None             | Restricted to 420.17 MHz (period = 2.380 ns) | ff:115)q | #.#7)q   | module_clock  | module_clock | 0               |

| 5 | Total number of failed paths |       |                  |                                              |          |          |               |              | 0               |

### Fig7: Timing Analyzer Summary

The Figure 7 shows the Timing Analysis summary for the DUT. It may obtain this state by applying the Timing Analyzer Summary View Section once again and It may verify the Device Components which are taken as DUT where each element is listed as required time, Actual time.

### **IV. CONCLUSION**

The test patterns generation based on the behavioural functionalities of any DUT is processed. BBATG uses the device behaviour fault model and represents a circuit board as interconnection of devices. A behaviour of a device is a set of functions with timing relations on its in/out pins.

When used for a digital circuit board test generation, BBATG utilizes device behaviour libraries to drive behaviour error signals and sensitize paths. Thus the test vectors for effective fault coverage are generated. Data can be processed by a versatile UART interface implemented on FPGA and able to support any baud-rate in order to interface a USB converter.

After the implementation, simple test patterns are loaded to the memory by FSM using FPGA-equipped board. Based on that DUT stimulus is generated, tested and samples should be collected. The low-cost, easy-to-use and reconfigurable automatic test machine referred as FATE (FPGA-based ATE) is yet to be implemented.

The communication between the Laptop and FPGA can be done by the UART. If target FPGA board doesn't support an USB to UART converter, a serial cable communication is also available.

In this case, baud rate is selectable in a predefined range of discrete values. The systemic failures, with the consequent reduction of time-to-market, time-to-yield and time-to volume. Experimental results can be obtained using this test machine for the screening of digital part of complex SoCs confirmed its validity, at least for the addressed applications.

### REFERENCES

[1] Cheng W. T, The back algorithm for sequential test generation, Proc, 1988 IEEE Int. Conf. on Computer Design, pp. 66--69, Oct. 1988.

[2] Giaconia.C, Di Stefano. A, Capponi.G, "Reconfigurable digital instrumentation based on FPGA System-on-Chip for Real-Time Applications," 2003. Proceedings. The 3rd IEEE International Workshop, 30 June-2 July 2003, pp. 120 – 122.

<sup>[3]</sup> Hauch.S, "The roles on FPGA's in reprogrammable systems," in Proceedings of The IEEE, vol. 86, no. 4, April 1998.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Special Issue 6, May 2015

[4] Hawkins C.F, Nagle H.T, Fritzemeier R.R. Guth J.R, The VLSI circuit test problem-a tutorial Industrial Electronics," IEEE Transactions, vol. 36, Issue 2, May 1989, pp. 111 – 116.

[5] Huxun Chen, DeQing Chen, Jinlin Ye, Weizhou Cao, Lei Gao "An Integrated Automatic Test Generation and Executing System" IEEE Conference Sept 2011.

[6]Konala S, ChenP, and Abramovici M, "Built-In-Self-Test of Logic Blocks in FPGAs," Proc. IEEE VLSI Test Symposium, 1996, pp. 387-392.

[7] Luca Mostardini, Luca Bacciarelli, Luca Fanucci, Lorenzo Bertini, Marco Tonarelli "FPGA-based Low-cost Automatic Test Equipment forDigital Integrated Circuits" IEEE International Workshop Sept 2009.

[8] MohmedElbably" An Automatic testing of PLDs" Nineteenth National Radio Science Conference , March 19-23, 2002.

[9] Niermann, T., Patel J.H. HITEC: "A test generation package for sequential circuits", Proceeding of the European Conference on Volume, Issue, 25-28 Feb 1991 Pages;214-218

[10] Saad E.M, Talkhan I.E, Sayed I.M, "A proposed ATE for digital systems Radio Science Conference," 1996. NRSC '96., Thirteenth National, 19-21 March, 1996, pp. 209 – 220.

[11] Schulz M. H and Auth E, Essential: an efficient self-learning test pattern generation algorithm for sequential circuits, Proc. 1989 Int. Test Conf., pp. 28--37, Sept. 1989.

[12] StroudC, Lee E, Yonala S, and Abramovici M, "Using ILA Testing for BIST in FPGAs," Proc. OfInternational Test Conference IEEE, 1996, pp. 68-75.

[13] ww.verigy.com/ (Verigy website)

[14] www.advantest.com/ (Advantest website)

[15] www.inovys.com/ (Inovys website)

[16] www.nextest.com/ (Nextest website)