(An ISO 3297: 2007 Certified Organization) Vol. 4, Special Issue 6, May 2015

# A New Multilevel Inverter Topology withLevel Doubling Network and Fuzzy Controller

Shyni.P.Nair<sup>1</sup>, M. Austin Johnny<sup>2</sup>

PG Student, Department of EEE, CSI Institute of Technology, Thovalai, <sup>1</sup>

Assistant Professor, Department of EEE, CSI Institute of Technology, Thovalai2

**ABSTRACT**: A new multilevel inverter (MLI) topology is proposedusing a level doubling network (LDN). The LDN takes the form of a half-bridge inverter to almost double the number of output volt-age levels. The concept (of the proposed LDN) has the capability of self-balancing during positive and negative cycles without any closed-loop control/algorithm, and it does not consume or supply any power. The topology uses a symmetric cascaded H-bridge MLI but offers an equivalent performance of an asymmetric topology in terms of the number of levels. Also, it maintains the merit of uniform loading of the individual cell for a symmetric MLI. The topology is implemented by connecting only a three-arm H-bridge (only two switches per phase) with the entire three-phase inverter to double the number of levels. Thus, it significantly improves the power quality, reduces the switching frequency, and reduces the cost and size of the power filter. Operation of the circuit is verified by simulation result and experiments from a laboratory prototype.

**KEYWORDS**: AC drives, converter topology, level doublingnetwork (LDN), multilevel inverter (MLI), power quality.

### I. INTRODUCTION

Non-availability of power electronic switches capable to withstand high voltage is the main motivation for the promotion of multilevel inverters (MLIs). MLIs are now very popular and globally recognized topology for many industrial applications, like medium-voltage ac drives, renewable energy, HVDC and FACTS, traction and propulsion systems, electric vehicles, etc. In high-voltage and high-current applications, high switching frequency is prohibited mainly due to switching losses and high dV/dt. Efforts are put to achieve acceptable voltage waveformand power quality through reduced switching frequency. The number of voltage level that can be generated using a minimum number of switching devices remains very crucial for such topologies. A number of approaches are proposed to increase the number of levels of MLI. Cascaded H-bridge (CHB) MLI allows one to achieve high-quality output voltages and input currents and also high reliability due to their intrinsic component redundancy. One of the techniques to increase the number of levels is by intro-ducing asymmetry in voltage ratio of the inverter cells, in asymmetric structure, powers delivered by the various levels are quite different. While most of the power is delivered by the highest voltage cell, the lower voltage cells deal with only a fraction of the same. This is a serious limitation of such configurations for applications in ac drives. An asymmetrical configuration has un-equal power sharing. This does not allow the bridges to be easily replaced (as the high side and low side bridges most likely to be made by different power devices) and hence loses the advantage of modularity. This makes the asymmetric topology not very attractive for medium-voltage (MV) drives and many other applications. Recently, many hybrid multilevel topologies are proposed however, the symmetric CHB structure has definite merits in high-power applications due to fault tolerance/reliability and modularity. This paper proposes a new topology to almost double the number of levels in an MLI, by adding only two switches per phase.

### II. PROPOSED TOPOLOGY

The topology is realized by adding an extra half- bridge connected to a capacitor that maintains half the volt age of other bridges by a self-balancing mechanism. For a three-phase system, three half-bridges (i.e., one half-bridge per

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

phase) in parallel are required.

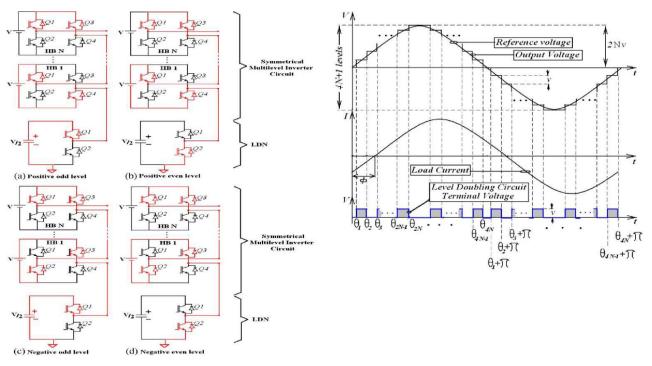

Fig 1Working of Proposed Topology

The Level doubling network works according to the switching given to each phase which is illustrated as below. The multilevel inverter circuit without an LDN can produce an output of about 2N+1 levels whereas by using an LDN an output level of 4N+1 can be obtained. The multilevel inverter with an LDN for single as well as three phase is given below.

|            | Cell 1 (2V) |        |        |        | Cell 2 (2V)   |                  |                |                | Cell 3 (2V)   |        |        |        | Cell 4<br>(V) |        |

|------------|-------------|--------|--------|--------|---------------|------------------|----------------|----------------|---------------|--------|--------|--------|---------------|--------|

| Opt.       | Q<br>1      | Q<br>2 | Q<br>3 | Q<br>4 | Q<br>1        | Q<br>2           | Q<br>3         | Q<br>4         | Q<br>1        | Q<br>2 | Q<br>3 | Q<br>4 | Q<br>1        | Q<br>2 |

| -6V        | 0           | 1      | 1      | 0      | 0             | 1                | 1              | 0              | 0             | 1      | 1      | 0      | 0             | 1      |

| -5V        | 0           | 1      | 1      | 0      | 0             | 1                | 1              | 0              | 0             | 1      | 1      | 0      | 1             | 0      |

| -4V        | 0           | 1      | 1      | 0      | 0             | 1                | 1              | 0              | 0             | 1      | 0      | 1      | 0             | 1      |

| -3V        | 0           | 1      | 1      | 0      | 0             | 1                | 1              | 0              | 0             | 1      | 0      | 1      | 1             | 0      |

| -2V        | 0           | 1      | 0      | 1      | <b>HO</b> g 2 | 2 S <b>j</b> wit | ch <b>iù</b> g | of <b>Q</b> ne | P <b>0</b> as | e 1    | 1      | 0      | 0             | 1      |

| -1V        | 0           | 1      | 0      | 1      | 0             | 1                | 0              | 1              | 0             | 1      | 1      | 0      | 1             | 0      |

| <b>0</b> V | 0           | 1      | 0      | 1      | 0             | 1                | 0              | 1              | 0             | 1      | 0      | 1      | 0             | 1      |

| 1V         | 0           | 1      | 0      | 1      | 0             | 1                | 0              | 1              | 0             | 1      | 0      | 1      | 1             | 0      |

| 2V         | 0           | 1      | 0      | 1      | 0             | 1                | 0              | 1              | 1             | 0      | 0      | 1      | 0             | 1      |

| 3V         | 0           | 1      | 0      | 1      | 0             | 1                | 0              | 1              | 1             | 0      | 0      | 1      | 1             | 0      |

| 4V         | 1           | 0      | 0      | 1      | 1             | 0                | 0              | 1              | 0             | 1      | 0      | 1      | 0             | 1      |

| 5V         | 1           | 0      | 0      | 1      | 1             | 0                | 0              | 1              | 0             | 1      | 0      | 1      | 1             | 0      |

| 6V         | 1           | 0      | 0      | 1      | 1             | 0                | 0              | 1              | 1             | 0      | 0      | 1      | 0             | 1      |

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

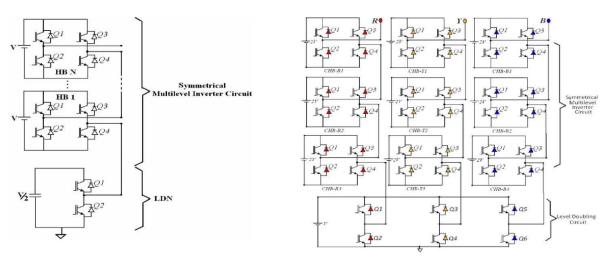

Fig 3 Level Doubling Network for Single And Three Phase

### III. INHERENT SELF-BALANCING CAPABILITY

Due to various possible transients and disturbances, the dc bus voltage of the LDN may become higher or lower than the desired voltage for short duration.

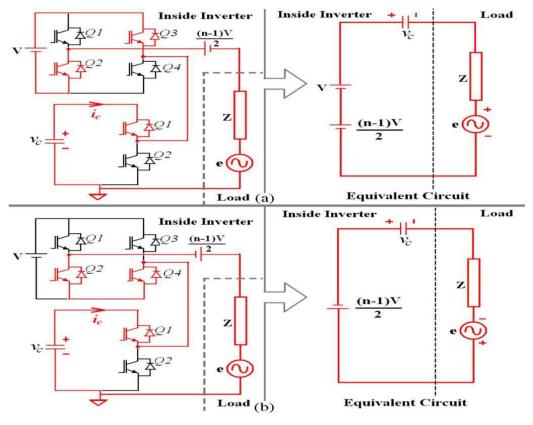

Fig 4 Equivalent Circuit

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Special Issue 6, May 2015

This section illustrates the self-balancing capability of the LDN without any closed-loop control. The basic assumptions for this explanation are the following.

1. The output voltage and current waveforms will have half-wave symmetry.

2. There will be a negligible dc component in the output current waveform under steady state.

3. A load with back EMF will also have half-wave symmetry in back EMF.

The self balancing capability of the LDN network is shown in the fig. The LDN has the capability of self balancing without any closed loop controlling algorithm.

### IV. FUZZY CONTROLLER

By implementing a fuzzy controller, the efficiency of the system can be improved. The fuzzy controller is usually implemented on the input side of the level doubling network and hence the self balancing capability is getting improved thereby an efficient output can be obtained by this method.

| Simulation Parameters        | Value      |  |  |  |

|------------------------------|------------|--|--|--|

| Number of H-Bridge Per Phase | 3          |  |  |  |

| Inverter Structure           | Symmetric  |  |  |  |

| Number of Phases at Output   | 3          |  |  |  |

| Input to DC Bus of H-Bridges | 94V        |  |  |  |

| H-Bridge DC-Bus Capacitances | 11,000 µF  |  |  |  |

| LDN DC Bus Capacitance       | 66,000 μF  |  |  |  |

| Load time constant           | 500 µs     |  |  |  |

| Switching Frequency of       | 5kHz       |  |  |  |

| Multicarrier PWM Signal      |            |  |  |  |

| Initial LDN voltage          | 0V and 94V |  |  |  |

Fig 5 Simulation Parameters

Thus by implementing a fuzzy controller on the input side of the Level Doubling Network, the switching losses can be reduced to a higher extend and also efficiency of the system can be improved.

### V. SIMULATION RESULTS

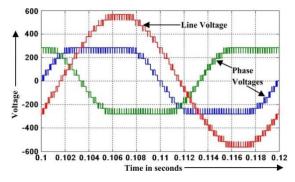

The performance of the topology is evaluated by simulating the circuit in MATLAB/Simulink. A Simulink model is developed for the three-phase version of the proposed topology. The output voltage and current waveforms and their total harmonic distortion (THD) are analyzed in detail. Also, the performance of the LDN and its energy consumption are investigated.

Fig 6 Simulation Result for Mli With Ldn

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Special Issue 6, May 2015

#### VI. CONCLUSION

This paper has presented a new concept to increase the number of levels in a cascaded MLI. A three-phase bridge network is used to almost double the number of levels of the three-phase cascaded MLI. The concept may be applied for both symmetric and asymmetric topologies. However, when applied with a symmetric topology, this has not only increased the levels but also maintained uniform power loading of the individual cell of the cascaded configuration. The dc bus of the H-bridge block ideally remains in self-balancing condition.

#### REFERENCES

- [1] H. Abu-Rub, J. Holtz, J. Rodriguez, and B. Ge, "Medium-voltage multilevel converters-State of the art, challenges, and requirements in industrial applications," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2581–2596, Aug. 2010. M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol.

- [2] 57, no. 7, pp. 2197-2206, Jul. 2010.

- [3] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters,"IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [4] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high-power applications," IEEE Trans. Ind. Appl., vol. 36, no. 3, pp. 834-841, May/Jun. 2000.

- Y.-S. Lai and F.-S. Shyu, "Topology for hybrid multilevel inverter," Proc. IEE Elect. Power Appl., vol. 149, no. 6, pp. 449–458, Nov. 2002. [5]

- [6] J. Dixon, J. Pereda, C. Castillo, and S. Bosch, "Asymmetrical multilevel inverter for traction drives using only one dc supply," IEEE Trans. Veh. Technol., vol. 59, no. 8, pp. 3736–3743, Oct. 2010

[7] X. Kou, K. A. Corzine, and Y. L. Familiant, "Full binary combination schema for floating voltage source multilevel inverters," IEEE Trans.

- Power Electron., vol. 17, no. 6, pp. 891-897, Nov. 2002.

- C. N. Ng, P. J. Dhyanchand, and V. M. Nguyen, "High Voltage Inverter Utilizing Low Voltage Power Switches," U.S. Patent Appl. 5 666 278, [8] Sep. 9, 1997.

- [9] H. Gruning, "Power Electronic Circuit Arrangement Having Plural Power Converters," U.S. Patent Appl. 5 805 437, Sep. 8, 1998.

- [10] A. L. Batschauer, S. A. Mussa, and M. L. Heldwein, "Three-phase hybrid multilevel inverter based on half-bridge modules," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 668-678, Feb. 2012.

- [11] M. Saeedifard, P. M. Barbosa, and P. K. Steimer, "Operation and control of a hybrid seven-level converter," IEEE Trans. Power Electron., vol. 27, no. 2, pp. 652-660, Feb. 2012.

- [12] P. Lezana and R. Aceiton, "Hybrid multicell converter: Topology and modulation," IEEE Trans. Ind. Electron., vol. 58, no. 9, pp. 3938-3945, Sep. 2011.

- [13] E. Najafi and A. H. M. Yatim, "Design and implementation of a new multilevel inverter topology," IEEE Trans. Ind. Electron., vol. 59, no. 11, pp. 4148-4154, Nov. 2012.

- [14] D. E. Soto-Sanchez, R. Pena, R. Cardenas, J. Clare, and P. Wheeler, "A cascade multilevel frequency changing converter for high-power applications," IEEE Trans. Ind. Electron., vol. 60, no. 6, pp. 2118-2130, Jun. 2013.

- [15] K. Wang, Y. Li, Z. Zheng, and L. Xu, "Voltage balancing and fluctuation suppression methods of floating capacitors in a new modular multilevel converter," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1943-1954, May 2013.

- [16] M. Khazraei, H. Sepahvand, K. A. Corzine, and M. Ferdowsi, "Active capacitor voltage balancing in single-phase flying-capacitor multilevel power converters," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 769–778, Feb. 2012. [17] C. A. Silva, L. A. Cordova, P. Lezana, and L. Empringham, "Implementation and control of a hybrid multilevel converter with floating dc links

- for current waveform improvement," IEEE Trans. Ind. Electron., vol. 58, no. 6, pp. 2304-2312, Jun. 2011.

- [18] J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel voltage-source-converter topologies for industrial medium-voltage drives," IEEE Trans. Ind. Electron., vol. 54, no. 6, pp. 2930-2945, Dec. 2007.

- [19] R. Teodorescu, F. Blaabjerg, J. K. Pedersen, E. Cengelci, and P. N. Enjeti, "Multilevel inverter by cascading industrial VSI," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 832-838, Aug. 2002.