(A High Impact Factor, Monthly, Peer Reviewed Journal) Vol. 5, Issue 2, Februray 2016

# **Bridgeless Topology for Power Quality Improvement in Switching Power Supply**

Pheba Merrin Jacob<sup>1</sup>, Mangala Devi K T<sup>2</sup>

P.G. Student, Department of Electrical and Electronics, Toc H Institute of Science and Technology, Kerala, India<sup>1</sup>

Assistant Professor, Department of Electrical and Electronics, Toc H Institute of Science and Technology, Kerala,

India<sup>2</sup>

**ABSTRACT**: Many electronic appliances such as personal computers require Switched Mode Power Supplies (SMPS) for powering up. Normally, a Diode Bridge Rectifier (DBR) followed by a filter capacitor is used at the front end of these SMPSs. DBR causes significant deterioration in the power quality leading to very low power factor and high harmonic distortion at the ac mains. This work deals with the design, analysis, and simulation of a power factor correction SMPS using a bridgeless buck-boost converter at the front end. Single-phase ac supply is fed to a pair of back-to-back-connected buck-boost converters to eliminate the diode bridge rectifier, which results in reduction of conduction losses and power quality improvement.

**KEYWORDS**: Switch mode power supply, power quality, bridgeless, buck-boost.

## I. INTRODUCTION

The growth of consumer electronics has meant that the average home has a lot of mains driven electronic devices such as low energy lighting, battery chargers, televisions, and computers their peripherals etc. Invariably these electronic devices have mains rectification circuits, which is the dominant cause of mains harmonic distortion. Most applications comprising of ac-dc power converters need the output dc voltage to be well regulated with good steady-state as well as transient performance.

The circuit which was typically favoured until recently (diode rectifier-capacitor filter) for the utility interface minimizes the cost, but it severely deteriorates the quality of the supply thereby affecting the performance of other loads connected to it also causing other well-known problems. The current waveform is very peaky, non-sinusoidal, and highly distorted; the PF is around 0.48. At full load, the total harmonic distortion (THD) of input ac mains current is 83.5%. The performance of the power supply is violating the limits set by various international standards such as the International Electrotechnical Commission (IEC) 61000-3-2.

Due to these issues, improved-power-quality SMPSs are extensively being researched, which are expected to draw a sinusoidal input current at a high PF. Improvement in power quality also results in better reliability and enhanced efficiency. To achieve a perceivable improvement in power quality, PF correction (PFC) circuits are employed in these SMPSs at the utility interface point. Active power factor correction refers to the method of increasing PF by using active electronic circuits with feedback that control the shape of the drawn current. High-frequency switching techniques have been used to shape the input current waveform successfully.

### II. RELATED WORK

The use of non-isolated PFC converters at the front end of these power supplies is a commonly accepted solution to achieve a good power quality at varying input voltages andloads. Single-ended primary inductance converter (SEPIC) topology utilizes a bidirectionalswitch and two fast diodes [9]. The absence of an input diode bridge and the presence of only one diode in the owing current path during each switching cycle result in less conduction lossand improved

(A High Impact Factor, Monthly, Peer Reviewed Journal)

#### Vol. 5, Issue 2, Februray 2016

thermal management compared to existing PFC rectifiers. These advantages re desirable features for high-power and high-voltage applications.

Various bridgeless single ended primary-inductance converter and Cuk converters areproposed in the literature, which result in low voltage stress, improved thermal management, and low conduction losses [10] - [12]. New bridgeless single-phase ac-dc power factor correction (PFC) rectifiers based on Cuk topology are proposed in [13]. The absence of an input diode bridge and the presence of only two semiconductor switches in the current owing path during each interval of the switchingcycle result in less conduction losses and an improved thermal management compared to the conventional Cuk PFC rectifier. These are designed to work in discontinuous conductionmode (DCM) to achieve almost a unity power factor and low total harmonic distortion of the input current.

In another bridgeless Cuk topology, two input rectifier diodes are replaced by twoswitches in order to eliminate one switch in the conventional CUK PFC rectifier. By usingDCM operation mode in the proposed converter, the control circuit is simplified and thecurrent loop is omitted. However, the component count is increased in these converters, which is not suitable for low-power SMPS applications, although the output voltage range fairly large.

While the high-frequency switching PFC stage reduces the line current harmonics, it also has drawbacks, such as: it introduces additional losses, thus reducing the overallefficiency; it increases the EMI, due to the high-frequency content of the input current; and it increases the complexity of the circuit, with negative effects on the reliability of theequipment, as well as on its size, weight and cost. The general aim of this thesis work is toinvestigate use of bridgeless buck-boost topology in the front end for rectification and power factor correction and to use synchronous switching at the back end converter.

### III. CIRCUIT CONFIGURATION AND ANALYSIS

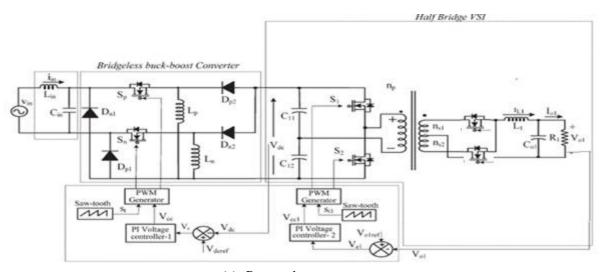

(a) Proposed convertor

The system configuration of the proposed SMPS is shown in Figure (a). Single-phase ac supply is fed to two buck-boost converters through an inductor-capacitor( $L_{in}$ - $C_{in}$ ) filter to eliminate the high-frequency ripples. This EMI filter, or electromagneticinterference filter, is an electronic passive device which is used in order to suppress conducted interference that is present on a signal or power line.

In the bridgeless buck-boost stage, two buck-boost converters are connected back-to-back so that each takes care of onehalf cycle of the ac supply. The upper buck-boost converter that conducts during the positivehalf cycle of the ac supply consists of one high-frequency switch  $S_p$ , inductor  $L_p$ , and two diodes  $D_{p1}$  and  $D_{p2}$ . Similarly, the lower buck-boost converter that operates during the negative half cycle consists of one high-frequency switch  $S_n$ , inductor  $L_n$ , and two diodes  $D_{n1}$  and  $D_{n2}$ . Both inductors  $L_p$  and  $_{Ln}$  of buck-boost converters are designed in DCM to obtain the performance of the input ac mains.

(A High Impact Factor, Monthly, Peer Reviewed Journal)

### Vol. 5, Issue 2, Februray 2016

**Operation of bridgeless buck-boost converter:** The bridgeless buck-boost converter is designed in DCM for single control loop and for inherent PFC.

**Mode 1**: In the first state, when the upper switch Sp is on, inductor Lp starts storingenergy from the input, and the inductor current increases to the maximum value. Diode Dp1 completes the current flow path in the input side.

**Mode 2:** In the second state, Spis turned off, and the energy in inductor Lp is transferred to the output, thus reducing its current from maximum value to zero.

**Mode 3**: In the last state of one switching cycle, neither the switch and nor the diodeconducts, and the inductor current remains zero, ensuring DCM operation.

In the next switching cycle, the same sequence of operation repeats itself. Similarly for negative half cycle of the input voltage, the lower buck-boost converteroperates, and the same sequence of operation continues.

The controlled output dc voltage of the dual buck-boost converter is fed to the half-bridge VSI for high-frequency isolation, for voltage scaling. The use of synchronous switching will improve the efficiency of the convertor. The operation of the half-bridge VSI in one switching cycle can be described in four states.

### **IV. DESIGN AND CONTROL**

Buck boost converter has to be designed to operate in discontinuous conduction mode (DCM). So the value of upper and lower inductors need to be calculated cautiously. The values of upper and lower inductors are the same, and they are chosen based on the change in inputcurrent in one switching cycle during on condition of the switch. The inductor value for aspecified current ripple is expressed as  $Lp = DTV_{avg}/\Delta_{iLpon}$

where D is the duty cycle, i.e.,  $t_{ON}=T$ , where  $t_{ON}$  is the 'on' time of the switch and T is the total period in one switching cycle, and  $V_{avg}$  is the average of single-phase ac input voltageacross the input of the buck-boost converter. In DCM condition, the inductor current rippleis considered maximum, and it must be equal to twice the input current.

$$Lp = \frac{DTVavg}{2*Iin} = 607\mu H$$

The control of the SMPS is carried out using two independent controllers. The front-end bridgeless buck-boost converter utilizes the voltage follower approach, while the half-bridge VSI utilizes the average current control.Initially the control loop computes the output voltage error and then the voltage error is given to a PI voltage controller and the output of this is further given to a PWM generator to obtain the ON/OFF control pulses.

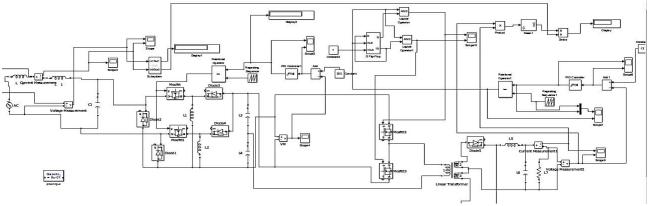

#### V. MODELLING AND SIMULATION

Performance of the proposed multiple-output SMPS is simulated in MATLAB/Simulink environment using Sim-Power-System toolbox and discrete time sampling. A sampling time of 0.8 sec is considered during simulation. Various power quality indices such as true power factor PF, and input current THD are analysed for assessing the power quality at single-phase ac mains.

(a) Proposed Converter

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Vol. 5, Issue 2, Februray 2016

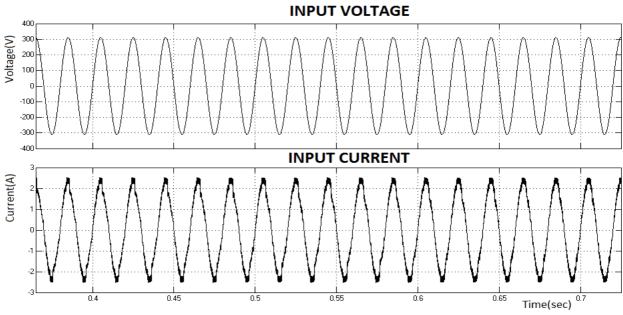

(b)Input Voltage and Current

Input voltage waveform which is shown in Figure (b). It shows that the voltage is purelysinusoidal. The input current is sinusoidal and in phase with the ac input voltage, ensuring high PF operation with very low harmonic distortion.

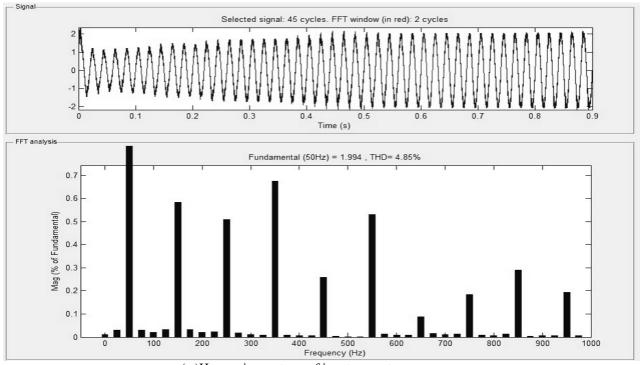

(c)Harmonic spectrum of input current

(A High Impact Factor, Monthly, Peer Reviewed Journal)

### Vol. 5, Issue 2, Februray 2016

Harmonics of line current using FFT analysis is as shown in Figure (c). Power factorof 0.99 and THD of 4.8% is achieved at mains.

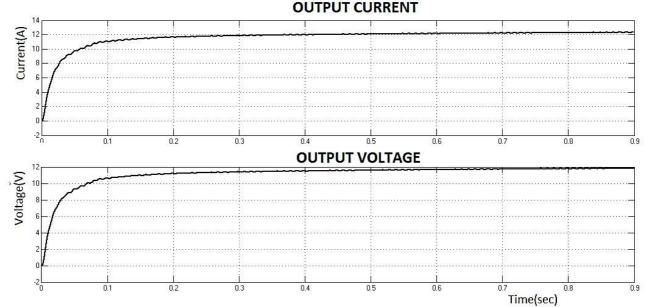

#### (d) Output voltage and current 12V/12.5A

Output current and voltage for range is as shown in Figure (d). The output voltage of the buck-boost converter and output dc voltages of VSI are maintainedconstant.

#### VI. CONCLUSION

A bridgeless converter based multiple-output SMPS has been designed and simulated. The output dc voltage of the first stage buck-boost converter has been maintained constant and it is operated in DCM to achieve inherent PFC at the single-phase ac mains. A satisfactory performance has been achieved with power quality indices remaining within the acceptable limits set by IEC 61000-3-2. Power factor of 0.99 and THD of 4.8% is achieved at the mains.

#### REFERENCES

- [1] Roger C. Dugan, Mark F. McGranaghan, Surya Santoso, H. Wayne Beaty, "Electrical Power Systems Quality", Second Edition 2011

- [2] P. J. Moore and I. E. Portugues, "The inuence of personal computer processing modes on line current harmonics," IEEE Trans. Power Del., vol. 18, no. 4, pp. 1363-1368, Oct.2003

- [3] Limits for Harmonic Current Emissions (Equipment Input Current 16 A per Phase), Int. Standard IEC 61000-3-2, 2000

[4] Muhammad H. Rashid, "Power electronics hand book: devices, circuits, and applications", Butterworth Heinemann, 2011

[5] Singh, S. Singh, A. Chandra, and K. Al-Haddad, "comprehensive study of single-phase ACDC power factor corrected converters with high

frequency isolation," IEEE Trans.Ind. Informat. vol. 7, no. 4, pp. 540- 556, Nov. 2011. [6] K.Matsui et al., "A comparison of various buck-boost converters and their applicationto PFC," in Proc. 28th IEEE IECON, 2002, vol. 1, pp. 30-36.

[7] W.-Y. Choi and J.-S. Yoo, "A bridgeless single stage half bridge AC/DC converter," IEEE Trans. Power Electron., vol. 26, no. 12, pp. 3884-3895, Dec. 2011.

[8] W. Wei, L. Hongpeng, J. Shigong, and X. Dianguo, "A novel bridgeless buckboost PFC converter," in Proc. IEEE PESC, Jun. 15-19, 2008, pp. 1304-1308.

[9] E. H. Ismail, "Bridgeless SEPIC rectifier with unity power factor and reduced conduction losses," IEEE Trans. Ind. Electron., vol. 56, no. 4, pp. 1147-1157, Apr. 2009.

[10] A. A. Fardoun, E. H. Ismail, A. J. Sabzali, and M. A. Al-Safar, "New efficient bridgeless Cuk rectifiers for PFC applications," IEEE Trans. Power Electron., vol. 27, no. 7, pp.3292-3301, Jul. 2012.

[11] M.Mahdavi and H. Farzaneh-Fard, "Bridgeless Cuk power factor correction rectifier with reduced conduction losses," IET Power Electron., vol. 5, no. 9, pp. 1734-1740, Sep.

(A High Impact Factor, Monthly, Peer Reviewed Journal)

### Vol. 5, Issue 2, Februray 2016

2012.

[12] Y. Jang and M. M. Jovanovic, "Bridgeless high-power-factor buck converter," IEEETrans. Power Electron., vol. 26, no. 2, pp. 602-611, Feb. 2011.

[13] L. Huber, Y. Jang, and M. M. Jovanovic, "Performance evaluation of bridgeless PFC boost rectifiers," IEEE Trans. Power Electron., vol. 23, no. 3, pp. 1381-1390, May 2008.

[14] Shikha Singh, Bhim Singh, G. Bhuvaneswari ,VashistBist, Ambrish Chandra and Kamal Al-Haddad M, "Improved-Power-Quality Bridgeless-Converter-Based Multiple-Output SMPS," IEEE Transactions on industry applications, vol. 51, no. 1, pp.721-732 January/February 2015 [15] Power Integrations, Application Note AN-53, Active Power Factor Correction

[16] J. Y. Lee, G. W. Moon, and M. J. Youn, "Design of a power-factor correction converter based on half bridge topology," IEEE Trans. Ind. Electron., vol. 46, no. 4, pp. 710-723, Aug. 1999.