An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 3, March 2016

6<sup>th</sup> International Conference in Magna on Emerging Engineering Trends 2016 [ICMEET 2016] On 10<sup>th</sup> & 11<sup>th</sup> March, 2016

Organized by

Dept. of ECE, EEE & CSE, Magna College of Engineering, Chennai-600055, India.

# **Encryption on Field-Programmable Gate** Arrays

K.Tagore, P.Venkatesh, K.Mary supreethi Assistant Professor, Dept. of ECE, CIET, LAM, India Dept. of ECE, CIET, LAM, India

Dept. of ECE, CIET, LAM, India

**ABSTRACT**- This paper presents two designs for the advanced encryption standard on field-programmable gate arrays (FPGAs) which occupies low area. The first design is an 8-bit application-specific instruction processor, which supports key expansion (currently programmed for a 128-bit key), encipher and decipher. The design utilizes less than 60% of the resources of the smallest available Xilinx Spartan II FPGA (XC2S15). The average encipher-decipher throughput is 2.1 Mbps when clocked at 70 MHz. The design has numerous applications where low area and low power are priorities. The second design, using the Xilinx PicoBlaze soft core is included to provide an embedded 8-bit microcontroller comparison baseline.

**KEYWORDS:** advanced encryption standard (AES), application-specific instruction processor (ASIP), field-programmable gate array (FPGA).

### I. INTRODUCTION

In January 1997, the National Institute of Standards and Technology (NIST) set out to establish a new standard of cryptographic algorithm to protect sensitive computer information and telecommunications systems in the Federal Government. The new algorithm would replace the aging Data Encryption Standard (DES) cipher algorithm, developed by IBM in the early 1970's. As a FIPS standard, AES will officially be identified as an approved cipher algorithm that can be used by U.S. Government organizations to protect sensitive (unclassified) information. Those Government organizations will be able to use the other FIPS approved algorithms in addition to, or in lieu of, AES.

The AES and its implementation for both application-specific instruction processor (ASIC) and field-programmable gate array (FPGA) technologies has been the subject of much research and continues to be a topic of interest in both academic and commercial environments.

In recent years, there has been a trend towards using FPGA in the production versions of electronic systems. It is no longer true that FPGAs are only used for prototyping. Their inclusion in the final version, would at first appear more expensive, however the ability to update the design and reduced time to market are strong commercial drivers. This was furthered by the introduction by the FPGA manufacturers of effectively mask programmed standard-cell versions of their technologies. This has resulted in an increased demand on optimal FPGA designs.

The main contribution of this paper is an ASIP capable of performing AES encipher and decipher operations using a truly8-bit datapath. The design avoids use of LUTs and proposes use of composite field data path for the SubBytes and InvSubBytes transformations. In addition, the MixColumns and all remaining operations are performed using a dedicated 8-bit Galois Field multiply-accumulate architecture. An iterative approach to multiplication was taken by implementing hardware support for finite-field doubling or finite-field multiplication by two (ffm2), halving and modulo-two addition. The ASIP achieves an average encipher-decipher throughput of 2.1 Mbps and utilizes less than two thirds of the resources of the smallest Xilinx Spartan-II part (XC2S15). To complete the design space exploration, a second design is also presented in this paper which utilizes the PicoBlaze [10] complex state machine soft core processor to provide a comparative 8-bit embedded processor design. The ASIP is shown to offer a threefold speed advantage for a similar area.

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 3, March 2016

# 6<sup>th</sup> International Conference in Magna on Emerging Engineering Trends 2016 [ICMEET 2016]

# On 10<sup>th</sup> & 11<sup>th</sup> March, 2016

### Organized by

#### Dept. of ECE, EEE & CSE, Magna College of Engineering, Chennai-600055, India.

### **II. ASIP DESIGN**

The first decision was to select an appropriate datapath width for the processor. As already described in the introduction, a number of the previous low-resource designs had opted for a 32-bit datapath. Examination of the AES mathematics revealed the possibility of using an 8-bit datapath which had not been previously explored. Using less than 8 bits is believed to be impractical as the AES predominately uses 8-bit Galois Field arithmetic.

The design of the ASIP was an iterative process. The design was conceptually split into three principal areas: the hardware, the instruction set and the application program. The definition of the instruction set effectively formed a design partition between the software and hardware aspects. A number of design iterations were followed. This is the classical hardware-software co-design issue.

From the initial stages of the design, three key issues were identified which contributed to most of the area. The first concerned the computation of SubBytes, for which existing implementations vary from look-up tables to computing the function mathematically. The second, was the definition of a suitable primitive operation (namely ffm-accumulate) to efficiently perform the Galois Field mathematics in the AES MixColumns, AddRoundKey, and KeyExpansion operations. The final issue was program ROM size reduction for which the two traditional techniques of iteration and subroutines were considered. These three issues are discussed in detail in the following sections.

#### A. Low-Area SubBytes

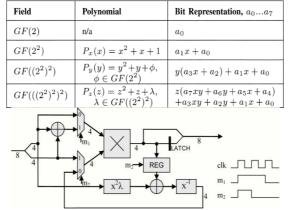

The most obvious method for implementing the SubBytes operation on FPGA was using a look-up table (LUT) based around a block memory (the "S-box"). The table for the forward and inverse transformation would require 512 bytes (4kbits). Given the dual port nature of Xilinx block memories this ROM could be used for two simultaneous operations. Here, an alternative, lower area, solution was required. A number of existing works [1]–[10] demonstrated how Sub-Bytes may be computed using Composite Field mathematics rather than a LUT.In order to perform an equivalent inversion in composite field arithmetic additional isomorphic transformations are required. These can be found using the method described in Paar [7]. The composite field theory was applied a number of times to construct a set of fields starting with the base field and building up successively to reach. Each stage has its own primitive trinomial and binary value format. Table I summarizes the field construction.

The objective was to perform the multiplicative inverse of the supplied value in  $GF(((2^2)^2)^2)$  over a number of cycles sharing the composite field multiplier. Here, the input byte is split into two 4-bit nibbles V=Az + B.

### **TABLE I: COMPOSITE FILD ARITHMETIC**

Fig.1 Block diagram of multiplicative inverse in  $GF(((2)^2)^2)^2$

The computational path of SubBytes was relatively long and this would dominate the cycle time of the entire processor. As the SubBytes operation was not the dominant operation in terms of quantity (as a fraction of the total instructions

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 3, March 2016

### 6<sup>th</sup> International Conference in Magna on Emerging Engineering Trends 2016 [ICMEET 2016] On 10<sup>th</sup> & 11<sup>th</sup> March, 2016

Organized by

### Dept. of ECE, EEE & CSE, Magna College of Engineering, Chennai-600055, India.

needed to perform the AES) this would have unduly limited the performance. Thus, SubBytes was split further into a total of five cycles to remove it from the critical path.

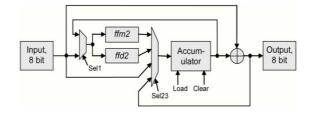

Fig.2 Block diagram of new subbytes circuit

This approach reduced the total forward and inverse SubBytes circuit to 42 slices on an XC2S15, a reduction in size of 27% compared to the original high-throughput version [9].

### **B. 8-BitffmAccumulate**

The AES MixColumns operator is fundamentally a 32-bit and there have been a number of designs [5][6] based around a 32-bit datapath. Only one design [9], for ASIC, was found which reported using an 8-bit datapath. However, the design married a 32-bit MixColumns to the 8-bit datapath by successively loading three 8-bit input registers in sequence to form the required 32-bit word with a similar process at the output. Here, a truly 8-bit alternative is sought with the corresponding area saving.

Examining the AES algorithm, a set of primitive operations were determined which cover the remaining operations of ShiftRows, mixColumns, and KeyExpansion. These were found to be ffm2 and XOR. For this design, the decipher function was also required and as it is undesirable to store the entire set of RoundKeys, a further operation of finite-field halving or finite-field division by two (ffd2) was needed for reverse KeyExpansion. The ShiftRows operator was implemented as a set of 8-bit data moves between memory locations. There are numerous examples in the MixColumns and Key-Expansion calculations where the result of an 8-bit operation was further acted upon. This was either in terms of repeated finite-field addition or repeated ffm2s. Thus, the inclusion in the datapath of an accumulator reduced the demands placed on the data memory. These requirements led to the development of a multiply-accumulate architecture capable of supporting moving 8-bit data 8-bit finite-field addition (XOR) and multiplication and division by two in  $GF(2^8)$ . An execution unit specific to this type of operation was developed and its circuit is presented in Fig.

Fig. 3 Circuit diagram for "multiply-accumulate" functions.

### C. Program ROM Size Reduction

One of the critical design decisions was which looping constructs, if any, were to be supported. A very simple processor could be constructed which only permitted execution of linear code. However, once the cost of the large program ROM size was balanced against the area and performance penalties for implementing even the most limited forms of iteration then linear code was no longer a viable option. The standard techniques for reducing the size of a program are iteration and subroutines. However, both techniques require specialist support from the processor hardware thus their inclusion would increase the area cost and complexity of the processor.

The final ASIP hardware provided support for one level of subroutines and two levels of iteration with one of the loop counters being used to conditionally provide indexed addressing. This enabled programming of the entire AES cipher process using only a few hundred instructions from an instruction set consisting of only 15 instructions.

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 3, March 2016

# 6<sup>th</sup> International Conference in Magna on Emerging Engineering Trends 2016 [ICMEET 2016] On 10<sup>th</sup> & 11<sup>th</sup> March, 2016

110 & 11 Warch, 201

Organized by

Dept. of ECE, EEE & CSE, Magna College of Engineering, Chennai-600055, India.

#### **III. ASIP HARDWARE**

### **TABLE 2: PROCESSOR INSTRUCTION SET**

| Opcode         | Src. Addr.         | Dst. Addr. | Operation                                                                                                            |  |

|----------------|--------------------|------------|----------------------------------------------------------------------------------------------------------------------|--|

| 0000<br>nop    | —                  | —          | no operation                                                                                                         |  |

| 0001<br>unused |                    |            |                                                                                                                      |  |

| 0010<br>jsr    | 00 $A_L$           | 00 $A_H$   | $rtn \leftarrow (pc) + 1, pc \leftarrow A_H A_L$                                                                     |  |

| 0011<br>retn   | —                  | 111111     | $pc \leftarrow (rtn)$                                                                                                |  |

| 0100<br>Idloop | n 0 cnt            | 111111     | $\{x _{n=0}, y _{n=1}\} \leftarrow cnt$                                                                              |  |

| 0101<br>ldflag | RXZEIO             | 111111     | $(flags) \leftarrow RXZEIO$                                                                                          |  |

| 0110<br>djnz   | n 0 A <sub>L</sub> | $0 0 A_H$  | $N \leftarrow N - 1, N = \{x _{n=0}, y _{n=1}\}$<br>if $N \neq 0$ , then $pc \leftarrow A_H A_L$                     |  |

| 0111<br>outp   | src                | 111111     | $output \leftarrow (src)$                                                                                            |  |

| 1000<br>sboxs  | src                | 111111     | $sb \leftarrow (src)$                                                                                                |  |

| 1001<br>sboxc  | src                | dst        | $(dst) \leftarrow sb$<br>repeat #4 times                                                                             |  |

| 1010<br>Idi    | imm                | dst        | $(dst) \leftarrow imm$                                                                                               |  |

| 1011<br>inp    | _                  | dst        | $(dst) \leftarrow (input)$                                                                                           |  |

| 1100<br>ffmsrc | src                | dst        | $\begin{array}{l} acc \leftarrow \textit{ffm2}(src) \\ (dst) \leftarrow (src) \ xor \ acc_{prev} \end{array}$        |  |

| 1101<br>ffmace | src                | dst        | $\begin{array}{l} acc \leftarrow \textit{ffm2}(acc_{prev}) \\ (dst) \leftarrow (src) \ xor \ acc_{prev} \end{array}$ |  |

| 1110<br>xorsrc | src                | dst        | $\begin{array}{l} acc \leftarrow (src) \ xor \ acc_{prev} \\ (dst) \leftarrow (src) \ xor \ acc_{prev} \end{array}$  |  |

| 1111<br>xorace | src dst            |            | $(dst) \leftarrow (src) \ xor \ acc_{prev}$                                                                          |  |

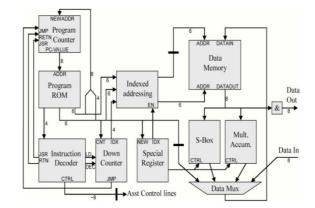

The traditional microcontroller architecture was adopted with separate program and data memories (i.e., Harvard Architecture). Two levels of looping were supported using two dedicated four bit counters X and Y. The loading of these was performed using the LDLOOP instruction and a single instruction DJNZ decreases a specified counter and performs a conditional jump if the value was nonzero. It was decided that a single four bit index, conditionally applied to source and destination RAM addresses, and associated with a loop counter (Y) was optimal. This addressing was enabled by the X flag and only operates on the lower 32 addresses (i.e., those associated with key and data and not the temporary storage). The value of the index was added modulo 16 or if the R flag was set, negated prior to the addition. The use of a single level of subroutines was supported using a dedicated return address register associated with the program counter. The JSR instruction calls a subroutine and the RETN instruction resume execution at the instruction immediately after the previous JSR.

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 3, March 2016

# 6<sup>th</sup> International Conference in Magna on Emerging Engineering Trends 2016 [ICMEET 2016]

# On 10<sup>th</sup> & 11<sup>th</sup> March, 2016

Organized by

Dept. of ECE, EEE & CSE, Magna College of Engineering, Chennai-600055, India.

### Fig.3 ASIP Architecture

The complete instruction set for the processor is summarized in Table II. Fig. shows the architecture of the processor. It should be noted that due to the clocking requirement of block memories, instructions take multiple cycles.

### IV. ASIP SOFTWARE

### a. Forward Key Expansion

The key expansion, defined in the AES specification, can express as a set of operations which are performed each round to generate the next RoundKey.

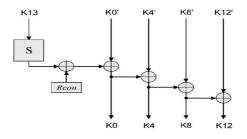

Fig.4: Forward Key Expansion.

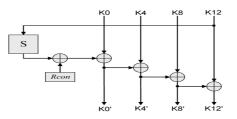

### b. Reverse Key Expansion

Reverse key expansion was approached using a similar method to the forward key expansion. However, the process starts with (k3', k7', k11', k15') and works backwards to finally yield (k0', k4', k8', k12'). This time the Rcon value was propagated in the reverse direction using ffd2.

Fig.5 Reverse Key Expansion

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 3, March 2016

# 6<sup>th</sup> International Conference in Magna on Emerging Engineering Trends 2016 [ICMEET 2016]

# On 10<sup>th</sup> & 11<sup>th</sup> March, 2016

Organized by

### Dept. of ECE, EEE & CSE, Magna College of Engineering, Chennai-600055, India.

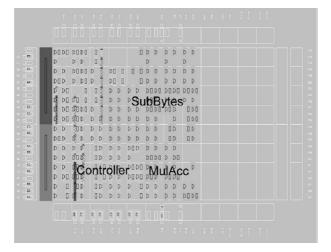

### V. RESULTS

Fig.4&5 shows that the placement of this design fits comfortably into the smallest Spartan-II device (XC2S15) occupying about 60% of the resources. The design required 145 slices (depending on user constraints) and two block memories. The block memory used as the register file was only partially utilized (360 bits) which gives rise to an alternative implementation using distributed memory with a cost of 42 additional slices and saving one of the block memories. No comparable 8-bit FPGA designs were found so comparison was made against the best 32-bit designs. Additionally, a second design was developed using the freely available Xilinx PicoBlaze core. This was done to provide a small embedded software baseline for comparison in terms of throughput and area. A concession was made in terms of implementing SubBytes as a ROM based lookup table.

Fig.6 Placement on XC2S15 FPGA

| <b>TABLE 3:</b> | <b>IMPLEMENTATION RESULTS</b> |

|-----------------|-------------------------------|

|-----------------|-------------------------------|

| Design & FPGA<br>(device)                    | ASIP(Spartan<br>II XC2S15) | Picoblaze<br>Spartan II<br>(XC2S15) |

|----------------------------------------------|----------------------------|-------------------------------------|

| Max.Clock                                    | 73                         | 90                                  |

| Freq.(Mhz)                                   |                            |                                     |

| Datapath Bits                                | 8                          | 8                                   |

| Slices                                       | 145                        | 127                                 |

| No.of BRAMS used                             | 2                          | 2                                   |

| BRAM Size                                    | 4                          | 4                                   |

| Bits of BRAM used                            | 4,580                      | 10,676                              |

| Eqiv. slices for<br>memory                   | 140                        | 333                                 |

| Total Eqiv. Slices                           | 250                        | 451                                 |

| Ave.<br>Throughput(Mbps)                     | 2.175                      | 0.80                                |

| Performance, Typ.<br>Throughput per<br>slice | 8.3                        | 1.5                                 |

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 3, March 2016

# 6<sup>th</sup> International Conference in Magna on Emerging Engineering Trends 2016 [ICMEET 2016]

# On 10<sup>th</sup> & 11<sup>th</sup> March, 2016

### Organized by

### Dept. of ECE, EEE & CSE, Magna College of Engineering, Chennai-600055, India.

#### **VI. CONCLUSION**

Both the ASIP and PicoBlaze based designs are the smallest known FPGA implementations to date. Such designs have application across a wide range of areas especially those needing a short time to market and relatively low power.

### REFERENCES

- X. Zhang and K. K. Parhi, "High-speed VLSI architectures for the AES algorithm," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 9, pp. 957–967, Sep. 2004.

- [2] A. Hodjat and I. Verbauwhede, "A 21.54 Gbits/s Fully Pipelined AES Processor on FPGA," in Proc. FCCM'04, Apr. 2004, pp. 308–309.

- [3] J. Zambreno, D. Nguyen, and A. Choudhary, "Exploring Area/Delay Trade-Offs in an AES FPGA Implementation," in Proc. LNCS FPL'04, Antwerp, Belgium, 2004, vol.3203,pp.575-585.

- [4] P. Chodowiec and Gaj, "Very Compact FPGA Implementation of the AES Algorithm," in Proc. LNCS'03,2003,vol.2779,pp.319-333.

- [5] G. Rouvroy F. X. Standaert, J. J. Quisquater, and J. D.Legat," Compact and efficient encryption/decryption module for FPGA implementation of the AES Rijndael very well suited for small embedded applications," in Proc. ITCC'04, Apr. 2004, vol. 2, pp. 583–587.

- [6] V. Fischer and M. Drutarovsky, "Two Methods of Rijndael Implementation in in Reconfigurable Hardware," in Proc. CHES'01, 2001, vol. 2162, pp. 77–92.

- [7] F. X. Standaert, G. Rouvroy, J. Quisquater, and J. Legat, "A Methodology to Implement Block Ciphers in Reconfigurable Hardware and its Application to Fast and Compact AES RIJNDAEL," in Proc. ACMFPGA'03, Monterey, CA, 2003, pp. 216–224.

- [8] M. Feldhofer, S. Dominikus, and J. Wolkerstorfer, "Strong Authention for RFID Systems Using the AES Algorithm," in Proc. LNCSCHES'04, 2004, pp. 357–370.

- [9] A. Satoh, S. Morioka, K. Takano, and S. Munetoh, "A Compact Rijndael Hardware ArchitectureWith S-Box Optimization," in Proc. LNCSASIACRYPT'01, Dec. 2001, vol. 2248, pp. 239–254.

- [10] K. Chapman, PicoBlaze 8-bit Microcontroller. 2002 [Online].Available: http://www.xilinx.com/products/design\_resources/proc\_central/grouping/picoblaze.htm,Xilinx.