(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

# Fault Tolerant Parallel Filters with Efficient Addition Structure

### TayyabUnnissa Begum<sup>1</sup>, M. Hymavathi<sup>2</sup>

Assistant Professor, Department of ECE, Lords Institute of Engineering and Technology, Telangana, India<sup>1, 2</sup>

**ABSTRACT**: In today's world there's an excellent need for the design of low power and area efficient high performance DSP system. FIRfilter is taken into account to be the elemental device within the broad application of wireless in addition because the video and image processing system. With the aim of obtaining the reliable operation, these filters are protected exploitation the Error correction Code. The pipelined FIR filter design that reduces the critical path by interleaving the pipelined latches on the datapath, with the sense of accelerating the quantity flatches then the system latency. However the parallel processed FIR filter design will increase the sample rate thereby replicating thehardware, so the multiple range of inputs gets processed parallely and at identical time generating multiple varieties of outputs with the disadvantage of magnified space within the design. To overcome this disadvantage and within the sense of holding theseadvantage of multiprocessing, the hardware economical filter structure is to be proposed, and these filter structure is to be recovered from error by the application of Error Correction Code.

KEYWORDS: FIR filter, Error Correction Code, Parallel Processing.

### I. INTRODUCTION

Finite impulse response (FIR) digital filters are common parts in several digital signal processing (DSP) systems. Throughout the years, with the progressively development in terribly large scale integration (VLSI) technology, the realthe \$64000} time realization of FIR filter with less hardware demand and fewer latency has become more and more important. as a result of the complexness of implementation grows with the length of filter, many algorithms are created to develop effective architectures for realization of FIR filters in application specific integrated circuits (ASIC) and field programmable gate arrays (FPGA) platforms and one in all them is error robust design. The most portion of error tolerant -based FIR computation is parity blocks that stores the precomputed values and might be read out simply, that makes FIR computation compatible for FPGA realization, as a result of the memory is that the basic parts of FPGA.

Moreover, this technology represents variety of attractive features like simplicity, regularity and modularity of design. Also, the error detection technique is designed to meet various speed requirements, as an example, it is designed for high-speed implementation wherever all bits of one word are processed per clock, it can even be designed for medium-speed implementation wherever many bits of one word (not all bits) are processed per clock. In recent years, fault tolerant-based FIR filter has gained substantial quality as a primary DSP operation and are rapidly replacement classic analog filters.

### II. RELATED WORK

Triple Modular Redundancy has three identical logic circuits (logic gates) are used to compute thespecified Boolean function. The set of data at the input of the first circuit are identical to the input of the secondand third gates. In computing, triple modular redundancy, sometimes called triple-mode redundancy. TMR is afault-tolerant form of N-modular redundancy, in which three systems perform a process and that result isprocessed by a majority-voting system to produce a single output.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 3, March 2016

If any one of the three systems fails, the othertwo systems can correct and mask the fault. The TMR concept can be applied to many forms of redundancy, such as software redundancy in the form of N-version programming, and is commonly found in fault-tolerant computer systems. Some ECC memory uses triple modular redundancy hardware (rather than the more commonHamming code), because triple modular redundancy hardware is faster than Hamming error correction software.

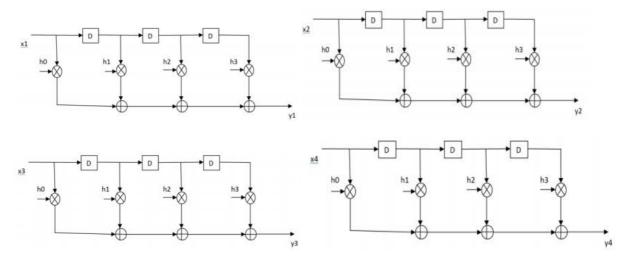

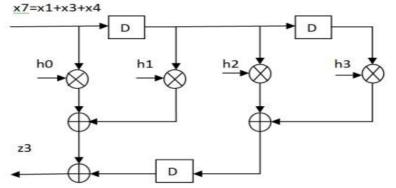

The existing pipeline filter structure is shown in the Fig. 1. This filter structure is designed for four input and fourfilter coefficients. The four filters are considered to bex 1, x2, x3 and x4 and the filter coefficients are found to beh0, h1, h2 and h3. The output generated will be y1, y2, y3 and y4.

Fig.1 Four filter pipelined structure

#### A. Original Module

The original module should be represented in the Fig.1.Inthis module the applied input gets convoluted by using its filtercoefficients then it generates the convoluted output.

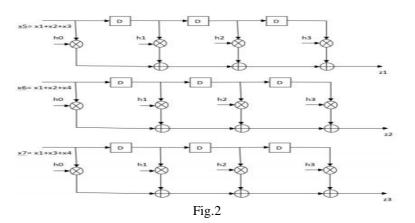

#### **B. Redundant Module**

The redundant module is the module used for achieving the realiable operation over the original module. Theredundant module is said to be the parity module which is used to generate the parity bits. These parity bits are presented as z1, z2, z3. The module takes a block of k bits and generated the block of n bits and the parity is obtained asn-k bits.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 3, March 2016

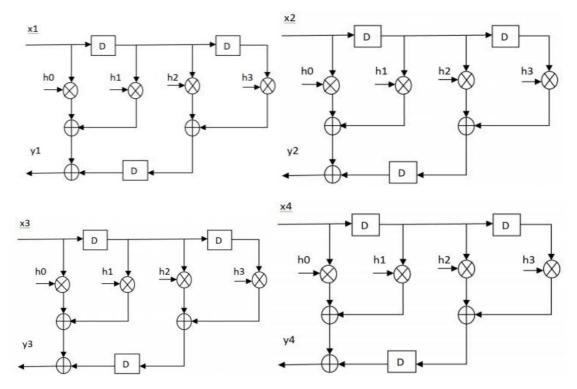

#### III. PROPOSED SYSTEM

The proposed filter structure has a difference in theadder structure implementation as compared with the existing pipeline structure. This efficient adder structure implementation in the pipelined filter is given in the Fig.4.below.

#### A. Original Module

The original module is represented in the Fig.4.In this module the applied input gets convoluted by using the efficient adderstructure. The original module is represented in sameFig.3.

Fig.3.Proposed Efficient Adder Pipelined Structure

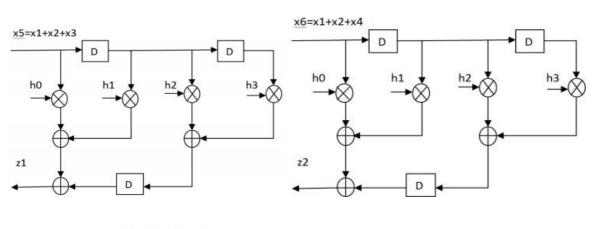

#### **B.Redundant Module**

The redundant module is same as that of the existing systems redundant module used for achieving the reliable operation over themain module. This module is used for generating the parity bits also represented as z1, z2 and z3. The parity is calculated as n-k bits.

Let us consider a simple example of Hamming code with k=4 and n=7, here the parity bits  $p_{1,p_2}$  and  $p_3$  are computed based on the data bits  $d_{1,d_2,d_3}$  and  $d_4$  as follows:

$p1 = d1 \pm d2 \pm d3$  $p2 = d1 \pm d2 \pm d4$  $p3 = d1 \pm d3 \pm d4$

The redundant module for the proposed system is shown in he Fig.5.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

Fig.4. Proposed Redundant Module

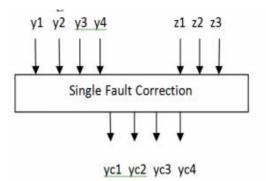

#### **C.Single Error Correction Module**

The single error correction module is used to correct the single bit error in the generated convoluted output at the proposed areaefficient adder structure. The single error correction module is shown in the Fig.5.

Fig.5 Proposed Single Error Correction Module

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

### IV. SIMULATION RESULTS

The Simulation results and the RTL schematic for the existing and proposed module are given below:

Fig.6. Simulation result for the Existing system

Fig.7. RTL schematic view proposed filter structure

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

Fig.8.Simulation Result of proposed system

#### V. CONCLUSION

In this paper, the Filter is designed with efficient hardware implementation structure for getting the reduced power with reducedhardware cost. The altered filter structure produces the analogous result as that of the existing module. The power consumption shouldbe reduced from 320mW to 312mW. The resource utilization can be obtained by analysing the slices, flipflops, used gate clk's, and IOB's. The single bit error correction is accomplished by using the Hamming Error Correction Code in the proposed system.

#### REFERENCES

- [1] K.K. Parhi, VLSI Digital Signal Processing systems: Design and Implementation. New York: Wiley, 1999.

- [2] Zhen Gao, Pedro Reviriego, Wen Pan, Zhan Xu, Ming Zhao, Jing Wang, and Juan Antonio Maestro, "Fault Tolerant Parallel Filters Based on ErrorCorrection Codes", IEEE Transactions On Very Large Scale Integration(VLSI) Systems, 1063-8210 © 2014 IEEE.

- [3] Z. Jiang and A. N. Willson, "Efficient digital filtering architectures usingpipelining/interleaving," IEEE Trans. Circ. Syst.-II, vol. 44, pp. 110–118, Feb. 1997.

- [4] Aarti Sharma1, Sanjay Kumar, "VLSI Implementation of Pipelined FIRfilter," International Journal of Innovative research inElectrical, Electronics, Instrumentation and Control Engineering vol.1 Issue5, Agust 2013.

- [5] Jaya Bar Madhumita Mukherjee, "A Comparative study on Directform-1, Fine grain and Broadcast structure of digital FIR filter", International Journal of Electronics, Communication & Soft ComputingScience and Engineering, Volume 2, Issue 5.

- [6] Ravinder Kaur, Ashish Raman, Member, IACSIT, Hardev Singh and Jagjit Malhotra, "Design and implementation of High speed IIR and FIRfilter using Pipelining," International Journal of Computer Theory and Engineering, Vol. 3, No. 2, April 2011.

- [7] A.Kamaraj, C.Kalyana Sundaram, J.Senthilkumar, "Pipelined FIR FilterImplementation using FPGA", International Journal of Scientific Engineering and Technology, vol1, Issue No.4, Oct. 2012

- [8] Jiang Xiaoyan and Bao Yujun, "FIR Filter Design Based on FPGA", 2010 International Conference on Computer Application System Modeling (ICCASM 2010).

- [9] Milenko Ciric and Vojkan Radonjic, "Realization of Multistage FIRFilters Using Pipelining-Interleaving", Telfor Journal, Vol. 4, No. 2, 2012.

- [10] N. Parijatha, K.R.A. Hinduja and A.C. Shaker, "FPGA Optimized LowPower and High Speed FIR Filter Structures For DSP Applications", International Journal of Engineering Research & Technology, vol. 2, pp. 1-5, Mar. 2013.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

### BIOGRAPHY

**TayyabUnnissa Begum** presently, working as Assistant Professor, Department of ECE, Lords Institute of Engineering and Technology, Telangana, India. Her research interests are in area of low power VLSI, FPGA architectures.

**M. Hymavathi** presently, working as Assistant Professor, Department of ECE, Lords Institute of Engineering and Technology, Telangana, India. Her research interests are in area of low power VLSI, FPGA architectures.