(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

# Design and FPGA Implementation of Digital Circuits Using Reversible Logic

Selsiya E<sup>1</sup>, Kalaiselvi D<sup>2</sup>

PG Scholar, Sri Venkateswara College of Engineering and Technology, Chennai, India<sup>1</sup>

Asst. Professor, Dept of ECE, Sri Venkateswara College of Engineering and Technology, Chennai, India<sup>2</sup>

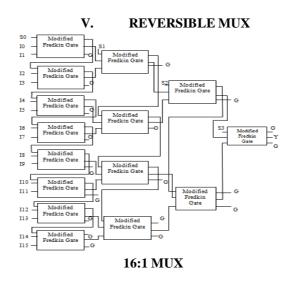

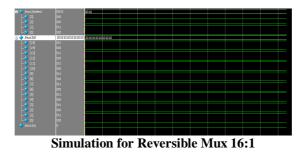

**ABSTRACT:** Interconnections are increasingly the dominant contributor to delay, area and energy consumption in CMOS digital circuits. Reversible logic can decrease the average power required for level transitions and reduces the number of required interconnections, hence also reducing the impact of interconnections on over all energy consumption. Multiplexing is the generic term used to designate the operation of sending one or more analog or digital signals over a common transmission line at dissimilar times or speeds and as such, the scheme used to do that is called a Multiplexer. In digital electronics, multiplexers are similarly known as data selectors as they can "select" each input line analog switches are encased made in a single form of IC package individuals conflicting to the "mechanical" type selectors into day era, such reversibility has become essential part of digital world to make digital circuits more efficient. Reversible logic proposes a new method to reduce interconnections and power for various multiplexers.

**KEYWORDS:** Reversible logic, Fredkin gate, Digital Circuits, MVLand Latch.

### I. INTRODUCTION

Conservative logic is called reversible conservativelogic when there is a one-to-one mapping between the inputs and the outputs vectors along with the property that there are equal number of 1s in the outputs as in the inputs. Conservative logic circuits are not reversible, if one-to-one mapping between the inputs and the outputs vectors is not preserved.

Conservative logic can be reversible in nature or may not be reversible in nature. Reversibility is the property of circuits in which there is one to- one mapping between the inputs and the output vectors, that is for each input vector there is a unique output vector and vice-versa.

QCA is one of the emerging nanotechnologies in which it is possible to implement reversible logic gates. QCA makes it possible to achieve circuit densities and clock frequencies beyond the limits of existing CMOS technology. In QCA, computing logic states of 1 and 0 are represented by the position of the electrons inside the QCA cell. Thus, when the bit is flipped from 1 to 0 there is no actual discharging of the capacitor as in conventional CMOS. Hence, QCA does not have to dissipate all its signal energy during transition. Further, propagation of the polarization from one cell to another is because of interaction of the electrons in adjacent QCA cells. As there is no movement of electrons from one QCA cell to the other, there is no current flow. Therefore, QCA has significant advantage compared to CMOS technology in terms of power dissipation. Due to high error rates in nano-scale manufacturing, QCA and other nanotechnologies target reducing device error rates.

This paper is organized as follows. Section II presents the conservative logic gates, Section III presents design of testable reversible latches, Section IV describes QCA, Section V presents design of testable reversible flip-flop, Section VI discusses theapplication of the proposed two vectors, all 0s and all 1s, Section VII provides some discussions and conclusions.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 3, March 2016

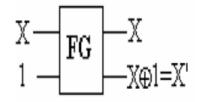

#### II. CONSERVATIVE LOGIC GATES

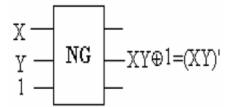

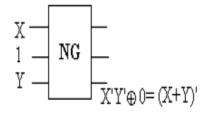

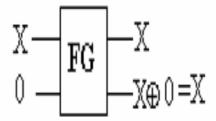

In order to design the sequential circuits, the conventional logic gates are appropriately designed from the reversible gates. The reversible gates used to design the conventional logic are so chosen to minimize the number of reversible gates used and garbage outputs produced. The design of AND function using Fredkin gate. The design of NAND and NOR function using New Gate respectively. Feynman Gates can be used for copying the outputs and to avoid the fan out problem in reversible logic. In the Feynman gate, there are exactly two outputs corresponding to the inputs and a '0' in the second input will copy the first input to both the outputs of that gate. Hence it can be concluded that Feynman gate is the most suitable gate for single copy of bit since it does not produces any garbage output. The Feynman gate as copying output and NOT function respectively. May stuck at 0 or 1 leading to accessingwrong address, no address, or multiple addresses.

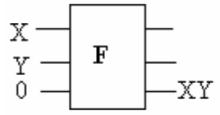

Fig.1 Fredkin Gate as AND Gate

Fig.2 New Gate As NAND Gate

Fig.3 New Gate As NOR Gate

Fig.4 Feynman Gate As Copying Output

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

Fig.5 Feynman Gate As Not Gate

Novel Reversible Flip Flops are designed using Feynman Gate, New gate and Fredkin Gate. The designed FFs are highly optimized in terms of number of reversible gates and garbage outputs.

Reversible logic elements, both with and without the property of conservatism, can be defined in many different logic systems. For the purposes of this paper, the class of reversible elements that can be modeled as binary-valued logic circuits will be called classical reversible logic elements. Much work has been done in defining and characterizing classical reversible logic and applying the concepts toward power conservation and specific technology implementations. This section will briefly define basic results in classical reversible logic.

| Gate Type        | Functionality                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------|

| 1*1 Not          | $x^+ = x$                                                                                       |

| 2*2 Feynman [4]  | $\begin{array}{l} x^+ = x \\ y^+ = x \oplus y \end{array}$                                      |

| 3*3 Tuffuli [19] | $ \begin{aligned} x^+ &= x \\ y^+ &= y \\ z^+ &= xy \oplus z \end{aligned} $                    |

| 3*3 Fredkin [5]  | $ \begin{array}{l} x^+ = x \\ y^+ - xy \oplus xz \\ z^+ - \overline{x}z \oplus xy \end{array} $ |

**Table.1 Gate functionality**

#### III. DESIGN REVERSIBLE LATCHES

The characteristic equation of the D latch can be written as  $Q^+ = D \cdot E + E \cdot Q$ . In the proposed work, enable (E) refers to the clock and is used interchangeably in place of clock. When the enable signal (clock) is 1, the value of the input D is reflected at the output that is  $Q^+ = D$ . While, when E = 0 the latch maintains its previous state, that is  $Q^+ = Q$ . The reversible Fredkin gate has two of its outputs working as 2:1 MUxes, thus the characteristic equation of the D latch can be mapped to the Fredkin gate (F). The realization of the reversible D latch using the Fredkin gate. But FO is not allowed in conservative reversible logic. Moreover, the design cannot be tested by two input vectors all 0s and all 1s because of feedback, as the output Q would latch 1 when the inputs are toggled from all 1s to all 0s and could be misinterpreted as stuck-at-1 fault.

In this paper, we propose to cascade another Fredkin gate to output Q as shown in Fig. The design has two control signals, C1 and C2. The design can work in two modes: normal mode and test mode.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

### IV. BASIC PRINCIPLES OF MVL

Depending on the assigned values to the inputs variables, MVL function will represent the value in domain  $D = \{0, 0\}$ 1,., K = L-1 and then a unique truth table can be obtained. Analogous to Products of Sums (POS) or Sum of Products(SOP) which is a unique representation of the function forbinary algebra, canonical Sum of Extended Products (SOEP) form is defined for universal set of operators for quaternary MVL algebra. The already mentioned operators SUC, MAX,eAND1, eAND2, eAND3 in the introduction, define auniversal set for quaternary logic under the proposed algebra. Once the universal set is defined, to minimize the number of terms and literals of the MVL function postulates and theorems are needed, thus a minimal covering is determined. Also suitable algebra laws are defined to develop algorithmsin a proper way and to implement software tools forperforming the minimization. In binary algebra, there are many techniques for function minimization such as K maps, Espresso, QuineMcCluskeyetc [17]. Depending on the MVL algebra under consideration all these binary techniques can be xtended to the MVL domain. The next step for the synthesis is to design gates in eitherCMOS current mode or CMOS voltage mode. In voltagemode there is problem of how to define voltage levels todiscriminate different logic reference levels for defining thethreshold value of CMOS inverters. As this paper addressesvoltage mode to design gate some characteristics must bedefined to overcome this issue, for example – powerconsumption, frequency response, fan-in, fan-out, noisemargins etc that has an effect on the W/L relation between thePMOS and NMOS gates and also on how to choose thereference voltage to discriminate among logic levels for the MVL. In recent years quaternary circuits has been studied increasingly as they have the practical advantage of transforming a four-valued signal into a two-valued signal. The next step is to define an algebra which is easy to learnand convenient to use, must have a well-known methodologywhich is feasible to implement from both algorithmic andgates point of views. A possible way is to extend the well-known concepts of the binary switching algebra to MVLalgebra. This approach is adopted in this work.

MVL variables are denoted as Aj for notation purpose.MVL constants are represented by lower case letters such as j,k, 1 and the base of the digital representation is denoted by Lwith domain  $D = \{0, 1, 2, ..., K = L-1\}$ . The Maximumoperator is denoted by "+" symbol. The proposed closed MVLalgebra is the ordered set with domain D in which acting oneunary Successor(SUC) operator and two binary extendedAND(eAND) and Maximum(MAX) operators (+, \*j) and twoelements 0 and (L-1) with the following definitions.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 3, March 2016

#### **IV. CONCLUSION**

Therefore conservative reversible logic gates are used to designed sequential circuits. The proposed system is used in the Feynman gate. This paper proposed reversible sequential circuits based on conservative logic that is testable for any unidirectional stuck-at faults using only two test vectors, all 0s and all 1s. The proposed sequential circuits based on conservative logic gates outperform the sequential circuit implemented in classical gates in terms of testability. The sequential circuits implemented using conventional classic gates do not provide inherited support for testability. Hence, a conventional sequential circuit needs modification in the original circuitry to provide the testing capability. Also as the complexity of a sequential circuit increases the number of test vector required to test the sequential circuit also increases. For example, to test a complex sequential circuit thousand of test vectors are required to test all stuck-atfaults, while if the same sequential circuit is build using proposed reversible sequential building blocks it can be tested by only two test vectors, all 0s and all 1s. Thus, the main advantage of the proposed conservative reversible sequential circuit irrespective of its complexity. The reduction in number of test vectors minimizes the overhead of test time for a reversible sequential circuit. The proposed work has the limitation that it cannot detect multiple stuck-at-faults as well as multiple missing/additional cell defects. In conclusion, this paper advances the state-of-the-art by minimizing the number of test vectors needed to detect stuck-at-faults as well as single missing/additional cell defects.

#### REFERENCES

[1] J. Ren and V. K. Semenov, "Progress with physically and logically reversible superconducting digital circuits," IEEE Trans. Appl. Superconduct., vol. 21, no. 3, pp. 780–786, Jun. 2011.

[2] S. F. Murphy, M. Ottavi, M. Frank, and E. DeBenedictis, "On the design of reversible QDCA systems," Sandia National Laboratories, Albuquerque, NM, Tech. Rep. SAND2006-5990, 2006.

[3] H. Thapliyal and N. Ranganathan, "Reversible logic-based concurrently testable latches for molecular QCA," IEEE Trans. Nanotechnol., vol. 9, no. 1, pp. 62–69, Jan. 2010.

[4] P. Tougaw and C. Lent, "Logical devices implemented using quantum cellular automata," J. Appl. Phys., vol. 75, no. 3, pp. 1818–1825, Nov. 1994.

[5] P. Tougaw and C. Lent, "Dynamic behavior of quantum cellular automata," J. Appl. Phys., vol. 80, no. 8, pp. 4722–4736, Oct. 1996. [6] M. B. Tahoori, J. Huang, M. Momenzadeh, and F. Lombardi, "Testing of quantum cellular automata," IEEE Trans. Nanotechnol., vol. 3, no. 4, pp. 432–442, Dec. 2004.

[7] G. Swaminathan, J. Aylor, and B. Johnson, "Concurrent testing of VLSI circuits using conservative logic," in Proc. Int. Conf. Comput. Design, Cambridge, MA, Sep. 1990, pp. 60–65.

[8] E. Fredkin and T. Toffoli, "Conservative logic," Int. J. Theor. Phys., vol. 21, nos. 3–4, pp. 219–253, 1982.

[9] P. Kartschoke, "Implementation issues in conservative logic networks,"M.S. thesis, Dept. Electr. Eng., Univ. Virginia, Charlottesville, 1992.[10] G. Swaminathan, "Concurrent error detection techniques using parity,"M.S. thesis, Dept. Electr. Eng., Univ. Virginia, Charlottesville, 1989.

[11] H. Thapliyal, M. B. Srinivas, and M. Zwolinski, "A beginning in thereversible logic synthesis of sequential circuits," in Proc. Int. Conf.MilitaryAerosp.Program. Logic Devices, Washington, DC, Sep. 2005, pp. 1–5.

[12] S. Mahammad and K. Veezhinathan, "Constructing online testablecircuits using reversible logic," IEEE Trans. Instrum. Meas., vol. 59,no. 1, pp. 101–109, Jan. 2010.

[13] H. Thapliyal and N. Ranganathan, "Design of reversible sequential circuits optimizing quantum cost, delay and garbage outputs," ACM J.Emerg. Technol. Comput. Syst., vol. 6, no. 4, pp. 14:1–14:35, Dec. 2010.

[14] M. Hasan, A. Islam, and A. Chowdhury, "Design and analysis of onlinetestability of reversible sequential circuits," in Proc. Int. Conf. Comput.Inf. Technol., Dec. 2009, pp. 180–185.

[15] M. Pedram, Q. Wu, and X. Wu, "A new design for double edge triggeredflip-flops," in Proc. Asia South Pacific Design Autom.Conf., 1998, pp.417-421.