ISSN (Online) : 2319 - 8753 ISSN (Print) : 2347 - 6710

## International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4th National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10th-11th March 2016

# Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

# Design of Low Power Based PentaMTJ in Combinational and Sequential Circuits

Theenathayalan.M<sup>1</sup>, Ashok kumar.M<sup>2</sup>

PG Scholar, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>1</sup>

Asst. Professor, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>2</sup>

**ABSTRACT**: spintronics has emerging technology and improve leakage current based conventional CMOS system. The important properties of magnetic tunnel junction is the low power and high speed. The spintronics process is used to logic and memory. This technology is the spin characteristics of electron, addition to fundamental charge in order to perform complex electronic operation. Therefore this analysis will include technology has reduced power and existing leakage performance of conventional CMOS system. The model of behavioural based used on Verilog simulation of the PentaMTJ.

**KEYWORDS**: spintronics, magnetic tunnel junction, non-volatile logic, magnetic logic.

#### I. INTRODUCTION

The spintronics is the non volatile, low power and under research going on the process. The spin is the storing in information and charge of processing and as potential to replace CMOS memory logic and memory. The submicrometer has scalling of CMOS analysis the leakage power to another this power components but digital level of signal is represented on conventional CMOS based on the logic function by absence and presence of the charge voltage or ground. The digital signal has up and down spin of electron. The principle of magnetic tunnel junction is the tunnel magnetoresistance.

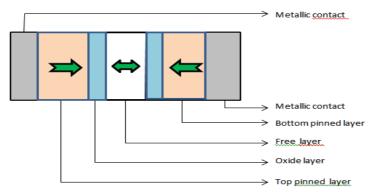

Fig.1. Structure of PentaMTJ

The MTJ are two ferromagnetic layer and oxide layer then improve the performance of CMOS logic circuits analysis for power dissipation. The different logic gates used in MTJ are processing and storing function as analysis for reduced the part of memory and interconnect power, delay to store data in memory. The drawback have magnetic tunnel logic gate is power and delay on the reported magnetic logic function. The magnetic tunnel junction based magnetic XOR gate comparing six of MTJ and area requirement is less then increase the number of MTJ. Logic gate required convert the voltage signal to current signal of magnitude for writing MTJ. The logicgates has only one of MTJ can reduce the part of logic operation. Example for operating voltage and initial state. Friedman proposed implemented

Copyright to IJIRSET <u>www.ijirset.com</u> 158

ISSN (Online): 2319 - 8753 ISSN (Print): 2347 - 6710

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10th-11th March 2016

## Organized by

## Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

logic operation of linear function like NAND and NOR. Non linear function is the two input XOR/XNOR to be implemented using NAND/NOR gate operation. Horwitz and hill proposed on a spin diode logic and CMOS logic gate but also CMOS based leakage power dissipation are constant voltage supply of the spin diode. The PentaMTJ is the two pinned ferromagnetic layer and one free layer. It insulating oxide are used to magnesium oxide layer. The two resistance of state like conventional MTJ one is parallel state and other to antiparallel state. It is used to the realization of memory. Huda and sheikholeslami has proposed a novel PentaMTJ based spin transfer torque magnetic random access memory for disturbance free reading. It is also presented a PentaMTJ based ternary content addressable memory and less delay. PentaMTJ of realization digital circuits have many advantage. First, magnetic logic gates of PentaMTJ is not require self referencing circuits and due the presence of contrary to MTJ. Second, extra hardware is don't needed for complementary output and presence of precharge sense amplifier sensing. Third, output of spintronics is direct sensed on the precharge sense amplifier. It is no need to initialize the state of the output MTJ for sensing. The sensing of power consumption is reduced power and speed of enhanced to use of PCSA.

## II. STRUCTURE OF PentaMTJ

The structure of PentaMTJ is the two pinned layer such as one is the top pinned layer and another to bottom pinned layer. The two pinned layer of magnetization is opposite direction and two part layer has fixed. The first state is assigned parallel to free layer. It is proposed PentaMTJ structure the less current of writing as compared the conventional MTJ. It is converting antiparallel to parallel state for one stack and another stack automatic come to antiparallel state.

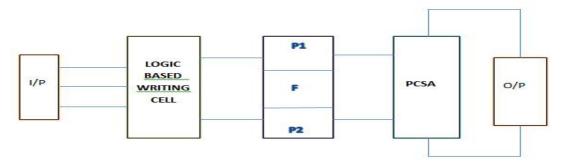

Fig.2. Block diagram of logic gate based PentaMTJ

The process of one stack is null and another contrary to two different MTJ. The data is no experience of double barrier always assumed that single barrier is model also valid for TMR ratio of double barrier. This two pinned layer and single free layer structure of PentaMTJ have already verified the macromagnetic simulation process. The pentaMTJ have low resistance of the conventional MTJ and it well of small value of oxide thickness analysis on MTJ. Perpendicular magnetic anisotropy based the spin transfer torque is the reduced switching voltage

#### III. LOGIC FUNCTION IN MEMORY

The part of three types 1. Two state resistance of PCSA sensing process, 2.logic of pentaMTJ, 3. Writing PentaMTJcell.PCSA of dynamic logic circuit have two phase, one is precharge phase and another to evalution phase. The branch of PCSA discharge has resistance branch discharge output more capacitance. The low resistance branch is pull down toward ground and high resistance branch pull up toward VDD.It is proposed logic gates, simultaneous precharging and writing the PentaMTJ is possible. pentaMTJ of PCSA is separated on MOS transistor M2 and M3. The precharging, clock is low disconnect the upper half from lower half. The stacking and high process voltage temperature variation are the conventional MTJ the deep submicrometer analysis the resistance mismatch on the PCSA has failure of MTJ/CMOS logic circuits. The PentaMTJ of writing logic function is the only one direction as this antiparallel to parallel state.

Copyright to IJIRSET <u>www.ijirset.com</u> 159

ISSN (Online): 2319 - 8753 ISSN (Print): 2347 - 6710

## International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10th-11th March 2016

## Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

#### IV. LOGIC GATE BASED PentaMTJ

The logic based PentaMTJ is XOR/XNOR logic functionn and the sensing portion is identical. This information are stored have pinned layer in series or parallel of transistor. The silmulation of logic gate result is both complementary and normal output. Now two input of A and B is 0 of output to corresponding discharge of PCSA and 1 are no discharge in normal output.

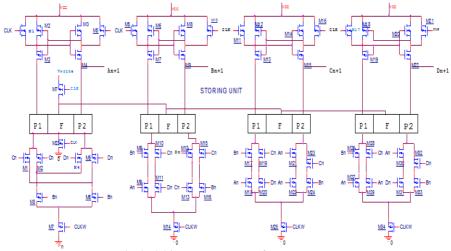

#### V. 4-BIT GRAY COUNTER

The combinational and sequential circuit is the logic function depends upon previous ouput and present state input. The 4-bit gray counter is logic function have sequential circuits and the present state of sequential circuit like gray counter is stored in flip flops. This is very power consumption of the stand by condition. The state of previous level is the previous have restored on pentaMTJ with few hundred picoseconds. In graycounter, PCSA are sensing to generating next state and pentaMTJ have present state storage, assign the writing circuit of next state to the present state.

Fig.3. 4-bit gray counter of PentaMTJ

The 4-bit gray counter compare to the pentaMTJ storage, the precharge sense amplifier are three sensing precess of the coming on the power. Therefore characteristics of the writing circuits.An,Bn,Cn are the present state and another to An+1, Bn+1, Cn+1 are next state. Then state in pentaMTJ using clock pulsewidthof 1.5ns and time period 2ns. The sensing and precharging is analysis of clock high 500ps using short low clock 200ps.

## VI. DISCUSSION AND RESULT

The PentaMTJofself referencing process is the reduce the area and the switching current density of PMA is directly proportional to the anisotropy, magnetization and free layer of the thickness. The MTJ/PentaMTJ of thermal stability factors contains capability of the digital logic. The timing delay depends upon switching is inversely propostional to the writing current. The MTJ/pentaMTJ of thermal stability factors contains capability of the digital logic. The timing delay depends upon switching is inversely propostional to the writing current. The zhang et al proposed to switching delay can 0.5ns of particular voltage or current.

Copyright to IJIRSET <u>www.ijirset.com</u> 160

ISSN (Online): 2319 - 8753 ISSN (Print): 2347 - 6710

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10th-11th March 2016

# Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

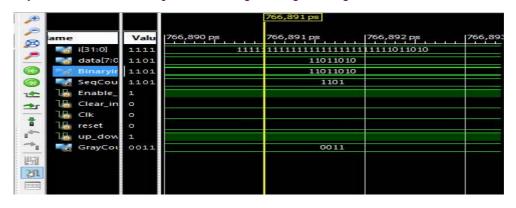

Fig.4. Simulation of 4-bit gray counter

The MTJ/PentaMTJ of thermal stability factors contains capability of the digital logic. The timing delay depends upon switching is inversely propostional to the writing current. Thezhang et al proposed to switching delay can 0.5ns of particular voltage or current. In our proposing PentaMTJ is 1.5ns and writing are computing this delay. In clock pulse of time period clock pulse in gray counter is taken 5ns and frequency of 500MHZ and PCSA sensing time is assuming 500ps doing precharge and sensing. It is increase the frequency in the gray counter and reduce andswitching time. Advantage of PentaMTJ based gray counter are require less number of transistors compared to gray counter. The writing every of PentaMTJ have logic gate based less every compared to MTJ.

# VII. CONCLUSION

It is short interconnect delay, low power and non volatile and the pentaMTJ of logic reduced area based logic function. The future scope of this pentaMTJ is the reduced current density required for switching and increase the switching speed.

# REFERENCES

- [1] A. Lyle *et al.*, "Magnetic tunnel junction logic architecture for realization of simultaneous computation and communication," *IEEE Trans. Magn.*, vol. 47, no. 10, pp. 2970–2973, Oct. 2011. S. Tehrani*et al.*, "Recent developments in magnetic tunnel junction MRAM," *IEEE Trans. Magn.*, vol. 36, no. 5, pp. 2752–2757, Sep. 2000.

- [2] S. A. Wolf et al., "Spintronics: A spin-based electronics vision for the future," Science, vol. 294, no. 5546, pp. 1488–1495, 2001. G. A. Prinz, "Magnetoelectronics," Science, vol. 282, pp. 1660–1663, Nov. 1998.

- [3] W. Xu, T. Zhang, and Y. Chen, "Design of spin-torque transfer magnetoresistive RAM and CAM/TCAM with high sensing and search speed," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 18, no. 1, pp. 66–74, Jan. 2010.

- [4] S. Huda and A. Sheikholeslami, "A novel STT-MRAM cell with disturbance-free read operation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 6, pp. 1534–1547, Jun. 2013.

- [5] S. Tehraniet al., "Recent developments in magnetic tunnel junction MRAM," *IEEE Trans. Magn.*, vol. 36, no. 5, pp. 2752–2757, Sep.2000. G. A. Prinz, "Magnetoelectronics," *Science*, vol. 282, pp. 1660–1663, Nov. 1998.

- [6] C. Chappert, A. Fert, and F. N. Van Dau, "The emergence of spin electronics in data storage," *Nature Mater.*, vol. 6, no. 11, pp. 813–823, Nov. 2007.

Copyright to IJIRSET www.ijirset.com 161