An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

# Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

# VHDL Implementation of Genetic Algorithm for Evolutionary Combinational Circuits

Vidyavathi.A<sup>1</sup>, Chidambaram.S<sup>2</sup>

PG Scholar, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>1</sup>

Professor, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>2</sup>

**ABSTRACT**: Electronic hardware's demandsthat the simple in architecture, power consumption, speed in operation and should be automatically regenerating the program if the program is failure. Genetic algorithm is one of the evolutionary algorithms. Using evolutionary algorithm we can get the desired program automatically. FPGA configuration bits are perfectly matches with binary bits of evolvable hardware. So evolvablehardware is mainly used to implement the evolutionary algorithm. The reconfigurable FPGA is used to save the time when we redesign the failure program. In this paper we discuss about the evolvable unit for adder.

KEYWORDS: Genetic algorithm (GA), reconfigurable FPGA, evolvable hardware, adder, evolutionary algorithm

I.

#### INTRODUCTION

Artificial intelligence, reconfigurable hardware, autonomous system and fault tolerance are combined and formed evolvable hardware. EHW is mainly used in two areas (i) new solutions are automatically generated (ii).Implement the adaptive devices. Evolvable hardware is used implement the stochastic algorithm. The mainly used to stochastic algorithm is genetic algorithm [1]. Genetic algorithm is designed based on the biological evolution process and use the concepts of natural selection and genetic inheritance. A genetic algorithm maintains candidates of population solution for the problem and it makes evolve by continuously applying the stochastic operators.

Field Programmable Gates arrays are a subset of field programmable devices(FPD) [3].FPGAs are programmable logic devices that permit the implementation of digital system.FPGAs are the most popular digital reconfigurable devices in the evolvable hardware community. FPGA based implementation of Evolvable Hardware can be divided into two grroups. (i)The FPGA serves in the fitness calculation only. The EA (whitch is executed on a persenal camputer or a digital signal processor(DSP)) sends configuration bitstreams representing candidate circuit to the FPGA in order to obtaian their fitness value.(ii)The entire evolvable system is implemented in an FPGA,were evolutionary algorithm implemented on same chip or separate boards to evolving designs [4].

FPGA are typically composed of an array of uniform logic cells, interconected through programmable inteconection matrices, witch configurable to perform a given function by means of an array of a configuration bitstreams. Each logic cell is composed of combinational and sequential programmable components, whose inputs and outputs are conneted to a programmable interconnectcion matrix [5]. FPGAs are composed of Look-up tables LUT), configurable logic blocks (CLB) and an interconnection network

#### II. GA AND VIRTUAL RECONFIURABLE CIRCUIT

Genetic algorithm is first introduced by "JOHN HOLLAND" in 1975. Genetic algorithm is inspired by the biological evolution process. Generally it uses the concepts of "genetic inheritance" and "natural selection" Initialization: Initially many individual solutions are randomly generated to form an initial population [7]. The population size depends on the nature of the problem, but typically contains several hundreds or thousands of possible solutions. Selection:During each successive generation, a proportion of the existing population is selected to breed a new generation. Individual solutions are selected through a fitness-based process, where fitter solutions (as measured by a fitness function) are typically more likely to be selected.

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

#### Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

Fitness: The chromosomes define the structure of the logic circuit. An encoding system is to be representing the structure of combination logic circuit [8]. The length of the chromosomes depends on the size of the entire structure. The number of bits in the chromosomes represents the type of gate. The collection of all individuals of the cell represents a solution The next step is to generate a second generation population of solutions from those selected through genetic operators: crossover (also called recombination), and/or mutation. Termination: This algorithm terminates when either a maximum number of generations has been produced, or a satisfactory fitness level has been reached for the population.

Fig.1. flow chart for Genetic algorithm

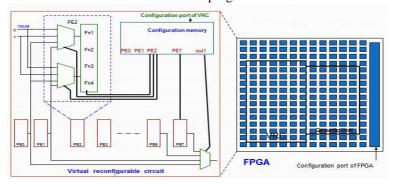

Virtual Reconfigurable circuit was introduced by Sekanina.L in 2006. VRC is the combination of software reconfigurable devices and genetic algorithm [9]. The structure of the VRC circuit is determined by downloading the binary bit strings called architecture bits. This is one of the new kinds of reconfigurable platform using the conventional FPGA. Once VRC is uploaded into FPGA the following parts are created at specified positions. (i)An array of programmable elements, (ii) Configuration port, (iii) Configuration memory and (iv) programmable interconnection network [10]. VRC architecture is similar to the Cartesian genetic programming architecture. Multiplexers are used as routing elements. Programmable elements have a number of registers to store the information. Programmable interconnection network is used to connect the programmable elements.

Fig.2. virtual reconfigurable circuit

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

## Organized by

## Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

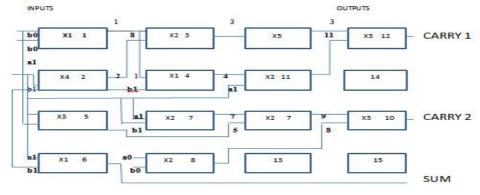

#### III. PROPOSED UNIT FOR ADDER

Evolvable hardware is used to increase the speed and performance. Evolvable hardware is mainly suitable for the space missions. The commonly used evolutionary algorithm is genetic algorithm. By using genetic algorithm we can get the desired circuit automatically if the circuit is failure. Evolutionary algorithm works based on the principle of natural evolution and self-adoption

Fig.3 proposed circuit

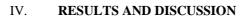

#### 1. Initialization

The different 44x4 bits outputs are generated for every rising edge clock by using XOR logic .The simulated waveform is shown in fig 4. This random number we considered as initial population of individuals. This random number generation process until termination of Genetic Algorithm (sufficient fitness achieved).

#### Fig.4.Simulation result for initialization.

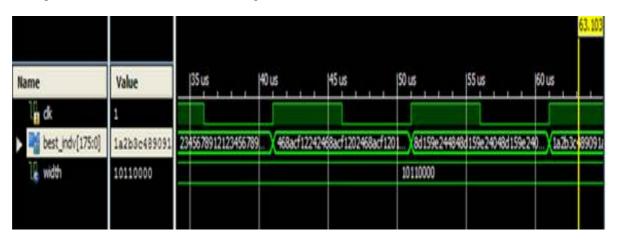

#### 2. Crossover

Crossover is an alternative method to generaste random numbers. Crossover simulated result shown in fig 8. best\_indv signal represents input data and random\_pattern represents output data. Single point crossover technique used for to generate random numbers.

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

# **Organized by**

## Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

| Name                       | Value        | 0 us                  | 20 us                   | 40 us                   | 60 us                   | 80 us            |

|----------------------------|--------------|-----------------------|-------------------------|-------------------------|-------------------------|------------------|

| l <mark>a</mark> dk        | 0            | 1                     |                         |                         |                         |                  |

| best_indv[175:0]           | 123456789098 | 8                     | 123456789               | 9876543211234567890987  | 654323456789            |                  |

| Image: Transformpatternc[] | 123456789876 | 8                     | 123456789               | 7654323456723456723456  | 783456789345            |                  |

| random_patterno[:          | 123456789098 | 123456789098765432112 | 3456                    | 4321123456 12           | 45678909876543211234567 | 990982cc8accceee |

| la condition               | 101          | 8                     |                         | 101                     |                         |                  |

| temp[175:0]                | 51519de265dd | 94546778997765544322  | 2333                    | 2eecaa8854444666888aaaa | cc8acccceeef 515:       | 9de265dd95510c88 |

| Reference                  | 51519de265dd | 28a8cef132eecaa       | 8854444666888aaaacc8acc | ceeef 515               | 9de265dd95510c8888ccd1  | 1555599159999ddd |

| 1 cond                     | 101          |                       |                         | 101                     |                         |                  |

Fig.5. Simulation result for crossover

Fitness Calculation Simulated output window is shown in fig 6, here best\_indv considered as an input and best\_fit representing output, it shows each and every best\_indv's fitness status. Pe\_indv[15:0] representing Programmable Elements input status, pe\_indv\_out representing pe\_indv output status, inputs[3:0] representing a0,a1,b0,b1 status. Fns [15:0] represents Logical Function condition.

|                     |              |      |                      |                      |                 |                      |                  |              | 173.927420  | us        |

|---------------------|--------------|------|----------------------|----------------------|-----------------|----------------------|------------------|--------------|-------------|-----------|

| Name                | Value        | 11   | 20 us                | 130 us               | 140 us          | 150 us               | 160 us           | 170 us       | 1           | 180 us    |

| l <mark>a</mark> dk | 1            |      |                      |                      |                 |                      |                  |              |             |           |

| dest_indv[175:0]    | 010110011110 | 01   | 1000101011001.       | 0001010110011        | 0010101100111   | 0101011001111        | 1010110011110.   | 0101         | 100111100.  | 10110011  |

| 1 rst               | 0            |      |                      |                      |                 |                      |                  |              |             |           |

| best_fit[3:0]       | 1111         | 1010 | 1011                 | 1100                 | X               | 1101                 | 1110             | $\mathbf{x}$ | 1111        | 0000      |

| inputs[3:0]         | 0001         | 1011 | 1100                 | 1101                 | 1110            | X 1111               | 0000             | $\mathbf{x}$ | 0001        | 0010      |

| s012_out[2:0]       | 001          | 101  | 011                  | 100                  | 101             | 110                  | X 000            | $\sim$       | 001         | 010       |

| pe_col[3:0]         | [01011001111 | [0   | [1000 10 10 1 100 1. | [0001010110011       | [0010101100111. | . [0101011001111     | [1010110011110.  | . (010       | 100111100.  | [1011001  |

| pe_indv[15:0]       | [01011001111 | [0   | [10001010110,0.      | . 000 10 10 1 100, 1 | [00101011001,1  | [01010110011,1       | [10101100111,1.  | 010          | 1001111,0.  | [1011001  |

| pe_indv_out[15:0]   | 000000010001 | 11   | 0010000111001.       | 0110011101010.       | 1111111101110.  | 1010100001101        | 001000000000.    | 0000         | 000100011.  | 00000000  |

| fns[15:0]           | [111,001,001 | [0   | [110,100,000,11.     | . [100,001,000,10.   | [001,010,001,01 | . [011, 100,010, 10. | [111,000,100,00. | .)(1111      | 001,001,00. | [110,010, |

| in 12[15:0]         | [01011001,00 | [0   | [10001010,0111.      | [00010101,1111.      | (00101011,1110. | [01010110,1100.      | [10101100,1000.  | [010         | 1001,0001   | [1011001  |

| Ug i                | 0            |      |                      |                      |                 | 0                    |                  |              |             |           |

| Ug in1              | 0            |      |                      |                      |                 |                      |                  |              |             |           |

| Lig in2             | 0            |      |                      |                      |                 | 2                    |                  |              |             |           |

| fit_value[3:0]      | 1111         | 1010 | 1011                 | 1100                 | X               | 1101                 | 1110             | $\sim$       | 1111        | 0000      |

|                     |              |      |                      |                      |                 |                      |                  |              |             |           |

|                     |              |      |                      |                      |                 |                      |                  |              |             |           |

|                     |              |      |                      |                      |                 |                      |                  |              |             |           |

Fig.6. Simulation result for fitness calculation

#### V.CONCLUSION

Proposed 2-bit adder is designed by using 16 number of PEs. The configuration of every PE is represented in the chromosomes as input1, input2, and function. 11 bits are needed to configure a single PE. The length of the chromosome is  $\Lambda$ =51 and size of the search space is up to |C| =10<sup>11</sup>. For dynamic adaption EHW using bio-inspired techniques like Genetic Algorithm (GA). Once a 2-bit adder is evolved using genetic algorithm, other combinational logic and sequential logic circuits will be the next step to evolve.

#### REFERENCES

[1] Parisa Soleimani 1, Reza Sabbaghi-Nadooshan 2, Sattar Mirzakuchaki3, and Mahdi Bagher "Using Genetic Algorithm in the Evolutionary Design of Sequential Logic Circuits" IJCSI International Journal of Computer Science Issues, Vol. 8, Issue 3, may 2011.

<sup>[2]</sup> S. Karakatic, V. Podgorelec, M. Hericko "Optimization of Combinational Logic Circuits with Genetic Programming" Elektronika Ir Elektrotechnika, ISSN 1392 1215, vol.19 Mar 2013

<sup>[3]</sup> K.H.Chong, I.B. Aris, M.A.Sinan "Digital Circuit Structure Design via Evolutionary Algorithm Method" Journal of Applied science 7(3):380-385.2007.ISSN 1812-5654

<sup>[4]</sup> Rakesh Kumar, Senior Member, IACSIT and Jyotishree, Member, IACSIT "Blending Roulette Wheel Selection & Rank Selection in Genetic Algorithms" International Journal of Machine Learning and Computing, Vol. 2, No. 4, August 2012.

<sup>[5]</sup> Firas Alabsi, Reyadh Naoum "Fitness Function for Genetic Algorithm used in Intrusion Detection System "Vol. 2 No. 4; April 2012.

[6] Prashant Sen, Priyanka Pateriya "Implementation of Generic Algorithm Using VHDLon FPGA" International Journal of Scientific & Engineering Research Volume 2, Issue 9, September-2011 ISSN 2229-55518.