An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

#### Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

# Quaternary Logic Lookup Table in Standard CMOS

Shalini Subbaiah<sup>1</sup>, Sujitha Venkateshwaran<sup>2</sup>, Syeda Arshiya Tabreen<sup>3</sup>, K.A.Dattathreya<sup>4</sup>

UG Scholars, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>1,2,3</sup>

Assistant HOD, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>4</sup>

**ABSTRACT:** Interconnections are increasingly the dominant contributor to delay, area and energy consumption in CMOS digital circuits. Multiple-valued logic can decrease the average power required for level transitions and reduces the number of required interconnections, hence also reducing the impact of interconnections on overall energy consumption. In this paper, we propose a quaternary lookup table (LUT) structure, designed to replace or complement binary LUTs in field programmable gate arrays. The circuit is compatible with standard CMOS processes, with a single voltage supply and employing only simple voltagemode structures. A clock boosting technique is used to optimize the switches resistance and power consumption. The proposed implementation overcomes several limitations found in previous quaternary implementations published so far, such as the need for special features in the CMOS process. The experimental results demonstrate the correct quaternary operation and confirm the power efficiency of the proposed design.

**KEYWORDS**: Field-programmable gate array (FPGA), lookup table (LUT), multiple-valued logic (MVL), quaternary logic, standard CMOS technology.

#### I. INTRODUCTION

In conventional binary CMOS digital circuits, static power consumption is tightly related to leakage currents, and dynamic power consumption is determined by (1), where C is the capacitance of the nodes being driven and  $V_{\text{DD}}$  is the power supply voltage.

### $P_D \propto \mathrm{CV}^2_{\mathrm{DD}}.$ (1)

The CMOS process has evolved by shrinking the transistors (thus reducing *C*) and employing lower supply voltages (lower  $V_{DD}$ ), therefore saving power and integrating more functionality into the same area. However, capacitance *C* also includes the routing capacitance associated with thewires connecting the logic gates. It has been reported that routing is exceeding transistors contributions for latency and power dissipation of designs in modern CMOS processes [1].An approach to mitigate the impact of interconnections is to use multiple-valued logic (MVL) [3], hence, more information can be carried in each wire, reducing the routing network. Therefore, a single wire carrying a signal with *N* logic levels can replace  $log_2N$ wires carrying binary signals. Reducing the routing leads to a direct reduction of the line capacitances and the overall circuit area.

This paper proposes a novel view of MVL circuits through the design of a look up table (LUT) based on the quaternary representation that exploits simple voltage-mode standard CMOS circuits and optimized switches using a simplified clock boosting (CB) technique. The proposed MVL LUT can replace or complement conventional binary logic, since the designed circuit is simple, efficient and we can combine both; i.e., they use the same implementation/fabrication technology.

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

## Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

#### II. QUATERNARY LOGIC AND LUTS

A quaternary variable can assume four different logic levels. Assuming a rail-to-rail voltage range and equal noise margins for the four logic levels, three different reference voltage values are required,  $1/6V_{DD}$ ,  $3/6V_{DD}$ , and  $5/6V_{DD}$ , to determine a quaternary value. Since a quaternary variable (*Q*) is able to carry twice as much information as a binary variable (*B*), we have the following relation:

$$|Q| = 2 \times |B|. \tag{3}$$

Therefore, two binary variables may be grouped into one quaternary variable without information loss, merging two nodes into one. It should be noted that there is no direct conversion of binary to quaternary logic gates in conventional CMOS, since the binary circuits use the available power rails to represent the binary symbols. For quaternary logic there are two more intermediate levels, which cannot be obtained directly using the same techniques. On the other hand, viable implementations of quaternary circuits have already beenachieved for LUTs, as demonstrated in [9].

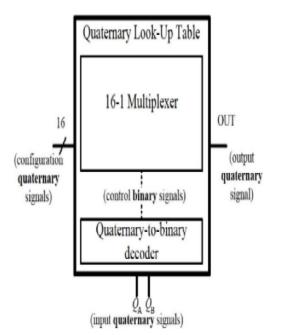

Fig. 1Proposed quaternary LUT

A LUT is an array indexing operator, where the output is mapped by the input, based on the configuration memory. The configuration values are initially stored in the LUT configuration memory, and according to the input, the logic value in the addressed position is assigned to the output.

The number of possible functions that may be represented in a quaternary LUT is much larger than in a binary LUT with the same number of inputs and outputs. Therefore, apart from reducing the total number of connections, MVL also leads to a reduction of the total number of gates when compared with a binary implementation.

#### III. PROPOSED QLUT TOPOLOGY AND IMPLEMENTATION

The proposed 2-input 1-output QLUT is shown in Fig. 1. For this given QLUT complexity, 16 quaternary configuration inputs are necessary, one for each possible combination of the two quaternary inputs. The

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

### **Organized by**

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

configuration word defines the reconfigurable quaternary function. In practice, the input signals are used to select which one of the configuration inputs is connected to the output. The proposed QLUT is composed of two main blocks: a 16-1 multiplexer using an array of switches, that establishes a low-resistance path between one configuration input and the output according to the input values; and a quaternary-to-binary decoder, consisting of a 2-bit analog-to-digital (ADC) frontend followed by combinational logic used to generate the control signals feeding the multiplexer. These blocks are described in the following sections.

A. 16-1 Multiplexer: Due to the quaternary nature of its inputs, the 16-1 multiplexer shown in Fig. 1 may be thought of as an analog multiplexer. The output is assumed to be of a capacitive nature and its value is defined by the interconnection network to which the QLUT output is connected.

**B.** Quaternary-to-Binary Decoder: The 2-bit quaternary-to-binary decoder allows the use of a single row of switches to drive the input configuration signals to the output of the QLUT. To do so, it is necessary to generate 16 control signals, to be applied in the clk1 inputs of each switch. These switches are employed to connect one quaternary configuration input to the output. To generate the required control signals, the quaternary variables are decoded into binary, allowing the use of binary logic gates. Thus, an ADC frontend is necessary, considering the analog nature of the quaternary signals.

| QA | QB      | XA | WA | ZA    | xB    | wB      | ZB      | cs(activebit)  |

|----|---------|----|----|-------|-------|---------|---------|----------------|

| 04 | 04      | 12 | 12 | 12    | 12    | 12      | 12      | <i>cs</i> (1)  |

| 14 | $0_4$   | 02 | 12 | 12    | 12    | 12      | 12      | cs(2)          |

| 24 | $0_{4}$ | 02 | 02 | 12    | 12    | 12      | 12      | <i>cs</i> (3)  |

| 34 | $0_{4}$ | 02 | 02 | 02    | 12    | 12      | 12      | <i>cs</i> (4)  |

| 04 | 14      | 12 | 12 | 12    | 02    | 12      | 12      | cs(5)          |

| 14 | 14      | 02 | 12 | 12    | 02    | 12      | $1_{2}$ | <i>cs</i> (6)  |

| 24 | 14      | 02 | 02 | 12    | 02    | 12      | 12      | cs(7)          |

| 34 | $1_{4}$ | 02 | 02 | 02    | 02    | 12      | 12      | cs(8)          |

| 04 | 24      | 12 | 12 | 12    | 02    | $0_{2}$ | 12      | cs(9)          |

| 14 | 24      | 02 | 12 | 12    | $0_2$ | $0_2$   | $1_{2}$ | <i>cs</i> (10) |

| 24 | 24      | 02 | 02 | 12    | 02    | $0_{2}$ | 12      | <i>cs</i> (11) |

| 34 | 24      | 02 | 02 | $0_2$ | 02    | $0_2$   | 12      | <i>cs</i> (12) |

| 04 | 34      | 12 | 12 | 12    | 02    | 02      | 02      | cs(13)         |

| 14 | 34      | 02 | 12 | 12    | 02    | 02      | 02      | cs(14)         |

| 24 | 34      | 02 | 02 | 12    | 02    | 02      | 02      | cs(15)         |

| 34 | 34      | 02 | 02 | 02    | 02    | 02      | 02      | <i>cs</i> (16) |

TABLE I: COMBINATIONAL BLOCK LOGIC FUNCTION

| QA       | $Q_B$ | $C_{IN}$ | Sum | $C_{OUT}$ | QA     | $Q_B$    | $C_{IN}$         | Sum | COUT |

|----------|-------|----------|-----|-----------|--------|----------|------------------|-----|------|

| 0.4      | 04    | 0.4      | 04  | 0.4       | 0.4    | 04       | 1.4              | 14  | 0.4  |

| 0.4      | 14    | 0.4      | 1.4 | 0.4       | 0.4    | $1_4$    | 1.4              | 24  | 0.4  |

| 04       | 24    | 0.4      | 24  | 0.4       | 0.4    | 24       | 1.4              | 34  | 0.4  |

| 0.4      | - 34  | 0.4      | 34  | 0.4       | 0.4    | 34       | - L <sub>4</sub> | 0.4 | 1.4  |

| 14       | 04    | 0.4      | 1.4 | 0.4       | 14     | $0_4$    | 1.4              | 24  | 0.4  |

| 1.4      | 14    | 0.4      | 24  | 0.4       | 14     | 14       | 1.4              | 34  | 0.4  |

| $-1_{4}$ | 24    | 0.4      | 34  | 0.4       | $-1_4$ | 24       | 1.4              | 0.4 | 1.4  |

| 1.4      | 34    | 0.4      | 0.4 | 14        | 14     | 34       | 1.4              | 14  | 1.4  |

| 2.6      | 0.4   | 0.4      | 24  | 0.6       | 24     | 0.6      | 1.4              | 34  | 0.4  |

| 24       | 14    | 0.4      | 34  | 0.4       | 24     | 14       | 1.4              | 0.4 | 1.4  |

| 24       | 24    | 0.4      | 0.4 | 14        | 2.4    | 24       | 1.4              | 14  | 1.4  |

| 24       | - 34  | 0.4      | 1.4 | 14        | 24     | 34       | 1.4              | 24  | 1.4  |

| 34       | 04    | 0.4      | 34  | 0.4       | 34     | $-0_{4}$ | 1.4              | 0.4 | 1.4  |

| 34       | 1.4   | 0.4      | 0.4 | 14        | 34     | $1_4$    | 1.4              | 14  | 1.4  |

| 34       | 24    | 0.4      | 1.4 | 14        | 3.4    | 24       | 1.4              | 24  | 1.4  |

| 34       | - 34  | 04       | 24  | 14        | 34     | 34       | 14               | 34  | 14   |

#### TABLE II: FULL ADDER LOGIC FUNCTION

#### IV. **FULL ADDER CIRCUIT**

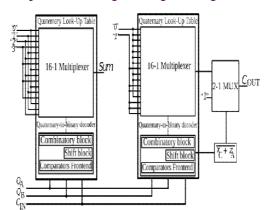

In this section, we employ the proposed QLUT to implement a full adder. The conventional and direct approach would require four QLUTs to properly implement this function, two QLUTs for each output, sum and carry out, working with the two possible values of the carry in. However, we propose minor modifications to the designed QLUT, which allows the reduction of the number of QLUTs only to two. This is achieved at the cost of a slight increase in binary combinational logic and a 2-1 multiplexer, as shown in F

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

### 10<sup>th</sup>-11<sup>th</sup> March 2016 Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

Fig. 2.QLUT full adder high level configuration.

#### **V.SOFTWARES AND SIMULATION RESULTS**

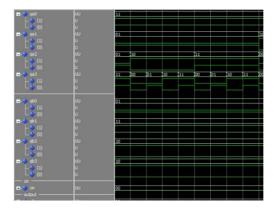

The softwares used in simulation are Xilinx, DSCH associated with Microwind and Model Sim Altra. At first we used DSCH Software, a logic editor and simulator used in validating the architecture of the circuit before the design phase, to develop schematics of each module using which we can generate the Verilog file .When the Verilog file is given to the Micro wind software, it generates the sketches required for IC Fabrication Process.For the verification of the project, the Verilog file is given to the Model sim Software, which in turn produces the Test Bench Results as shown below:

Fig 3.Experimental Outcome

#### VI. CONCLUSION

In this paper, we have reported an innovative QLUT design that can be used for multiple valued combinational logic or as a building block in FPGAs. The QLUT internal functionality is implemented using simple standard CMOS structures. This feature is achieved through a quaternary-to-binary decoder that quantize the input signals. This decoder is based on voltage-mode self-referenced comparators that allows the use of a standard CMOS technology and overcomes previous design drawbacks. Also, a CB technique was used to decrease the switches resistance and increase the operation frequency, while at the same time, achieving low power consumption. Therefore, the presented design is a valid solution to reduce the interconnections impact, without

An ISO 3297: 2007 Certified Organization

Volume 5, Special Issue 2, March 2016

4<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '16)

10<sup>th</sup>-11<sup>th</sup> March 2016

#### Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India.

increasing power consumption or losing performance. Experimental results were performed on an ASIC implementation of a full adder employing the designed QLUT.

#### REFERENCES

- 1. J. Rabaey, Low Power Design Essentials (Integrated Circuits and Systems). New York, NY, USA: Springer-Verlag, 2009.

- 2. L. Shang, A. S. Kaviani, and K. Bathala, "Dynamic power consumption in virtex-II FPGA family," in Proc. ACM/SIGDA Int. Symp. FieldProgram. Gate Arrays, 2002, pp. 157-164.

- 3. Z. Zilic and Z. Vranesic, "Multiple-valued logic in FPGAs," in Proc. Midwest Symp. Circuits Syst., 1993, pp. 1553-1556.

- 4. E. Ozer, R. Sendag, and D. Gregg, "Multiple-valued logic buses for reducing bus energy in low-power systems," IEE Comput. Digital Tech., vol. 153, no. 4, pp. 270-282, Jul. 2006.

- K. Current, "Current-mode CMOS multiple-valued logic circuits," IEEE J. Solid-State Circuits, vol. 29, no. 2, pp. 95–107, Feb. 1994. 5.

- J. Kim, "An area efficient multiplier using current-mode quaternary logic technique," in Proc. 10th IEEE Int. Solid-State Integr. 6. Circuit Technol., Nov. 2010, pp. 403-405.

- 7. W. S. Chu and W. Current, "Current-mode CMOS quaternary multiplier circuit," Electron. Lett, vol. 31, no. 4, pp. 267–268, 1995.

- R. da Silva, C. Lazzari, H. Boudinov, and L. Carro, "CMOS voltagemode quaternary look-up tables for multi-valued FPGAs," 8. Microelectron. J., vol. 40, no. 10, pp. 1466–1470, 2009.

- C. Lazzari, J. Fernandes, P. Flores, and J. Monteiro, "An efficient low power multiple-value look-up table targeting quaternary 9 FPGAs," in Integrated Circuit and System Design. Power and Timing Modeling, Optimization, and Simulation (Lecture Notes in Computer Science), R. van Leuken and G. Sicard, Eds., New York, NY, USA:

- 10. Springer-Verlag, 2011, pp. 84-93.

- 11. J. H. Anderson and F. N. Najm, "Power estimation techniques for FPGAs," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 12, no. 10, pp. 1015-1027, Oct. 2004.

- J. Uyemura, *Circuit Design for CMOS VLSI*. Boston, MA, USA: Kluwer Academic Publishers, 1992.

T. G. Rabuske, C. R. Rodrigues, and S. Nooshabadi, "A 5MSps 8-bit SAR ADC with single-ended or differential input," Microelectron. J., vol. 43, no. 10, pp. 680-686, 2012.

- 14. D. Brito, J. Fernandes, P. Flores, and J. Monteiro, "Design and characterization of a QLUT in a standard CMOS process," in Proc. IEEE 19th ICECS, Dec. 2012, pp. 288-291.