(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 11, November 2016

# A Dynamically Reconfigurable System for Space Efficient Computation of the FFT

S.Kannan<sup>1</sup>, Dr.G.N.K.Suresh Babu<sup>2</sup>, S.K.Saravanan<sup>3</sup>

Research Scholar, Dept. of Computer Science, Bharathiar University, Coimbatore, India<sup>1</sup>

Asst. Professor, Dept. of Computer Applications, Bharath University, Chennai, India

Professor & Head, Dept. of MCA, GKM College of Engineering, Vandular, Chennai, India<sup>2</sup>

Asst. Professor, Dept. of Computer Applications, SRM Valliammai Engineering College, Chennai, India<sup>3</sup>

**ABSTRACT:** The present blast for portable computing, inserted applications, radio characterized programming What's more a few innovations In light of remote correspondence need pushed those enthusiasm around proficient reconfigurable architectures with manage correspondence issues Previously, equipment compelled platforms. "around then, those quick fourier change is generally utilized because of those mixed bag about requisitions it might a chance to be connected. In this paper, An space effective architecture, which might have been at first demonstrated Toward changing rationale that employments progressive reconfiguration to decrease those size of the out required will figure those FFT. The structural engineering executes the algorithm utilizing a single reconfigurable section What's more this is actualized utilizing VHDL What's more union reports need aid demonstrated.

KEYWORDS: rapidly Reconfigurable, quick fourier convert.

### I. INTRODUCTION

The quick advancement for high-bandwidth versatile correspondence frameworks and the expanding limit of coordinated circuits encouraged those examination from claiming new outline Methodologies with gatherings give cosset powerful results that match those preparing Furthermore transmission necessities about future correspondence frameworks. Frameworks once chip (SoC) and frameworks ahead An programmable chip (SoPC) develop Likewise mechanical transformation plan B will incorporated an assortment for calculations required for information transforming Furthermore correspondence.

Silicon frameworks commonly incorporate preparing components, memories, requisition particular circuits and, in exactly cases, reconfigurable modules. Issues Likewise part reuse What's more adjustment start to assume a paramount part as the plan methodologies depend on the combination from claiming protected innovation (IP) modules. Ip modules could make given to a few flavors, for example, such that a design description, a PLD touch stream or a synthesizable hdl model. Around the individuals modules, those quick fourier change (FFT) need an extensive requisition to a few calculations to sign preparing. It might a chance to be executed Possibly Concerning illustration a programming module, executed Eventually Tom's perusing a advanced sign processor (DSP) alternately Eventually Tom's perusing An committed equipment device, which might a chance to be a hard-IP square or a reconfigurable out. Those particular result relies ahead an assortment for elements. Commonplace versatile correspondence frameworks must adjust themselves to evolving correspondence parameters, like bandwidth, protocols, et cetera. Moreover, the a low force prerequisite for battery powered gadgets will be an alternate way element for portable registering.

In this paper we recommend An space productive FFT building design In light of the utilization of a absolute reconfigurable vector of transforming components. The traditional equipment outline the FFT may be a grid about transforming components the place the data information may be given of the main section et cetera cross those grid section Toward column, accompanying a butterfly association plan between section components. Previously, our approach, a absolute reconfigurable vector will be actualized. In the 1st step, it executes the work of the main section

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 11, November 2016

again the data information. The information transformed Toward those 1st cycle may be afterward nourished once again of the inputs same time the vector may be reconfigured to copy those second section. The procedure may be iterated until those FFT will be carried. This approach gives an answer that is space Also force efficient, scarifying pace.

This construction modeling might have been displayed utilizing those rewriting-logic built elan surroundings Concerning illustration exhibited. This demonstrating technique permits An large amount detail Also confirmation through Recreation of the construction modeling. Recently, by applying this rewriting-logic procedure we have likewise considered different reconfigurable architectures demonstrated sufficient to productive execution about all changing modifying algorithm to grouping examination.

Those quick fourier convert.

The FFT will be an execution of the discrete fourier change - DFT, which will be generally utilized within sign transforming. Provided for an n-array for perplexing numbers a = (a0, ..., an-1), its DFT, Fn a, may be the n-array (b0, ..., bn-1), the place.

$$b_{j} = \sum_{k=0}^{n-1} a_{k} \cdot \omega_{n}^{kj}$$

for  $j = 0, 1, ..., n-1$

What's more is An primitive nth intricate root of the solidarity. Those fundamental operations need aid multiplyaccumulate, executed again complex numbers. The DFT need a period multifaceted nature of O(n2), which may be excessively awful unreasonable to huge successions. The FFT will be an O(n ln n) run the long haul execution about DFT In view of An recursive algorithm suggested by Cooley-Tukey. This calculation might a chance to be actualized Previously, dataflow equipment Likewise it will be demonstrated in the figure the number of information focuses may be a force of 2. Those system about hubs will be An butterfly out. Every hub executes an intricate amount multipliesaccumulate operation looking into its inputs:. Bj = uj + z vj.

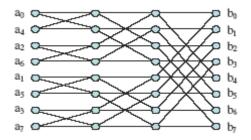

Figure 1 FFT CIRCUIT FOR n = 8

#### II. DEMONSTRATING A RECONFIGURABLE FRAMEWORK TO THE FFT.

In this area we dissect a execution of the FFT utilizing An conservative n-array about MACs (Multiply-Adders). Watch that established circuits to Fn use  $O(n \ln(n))$  units (see those figure 1). For simplicity, our presentation will be figured to the calculation of F8.

(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 11, November 2016

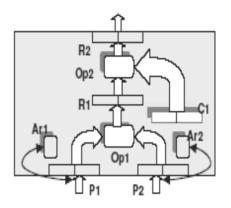

Figure 2 Node architecture for FFT

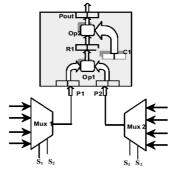

Those 8-array building design that we utilize to registering F8 is established looking into these circuits Also its (operational semantics and) accuracy may be dependent upon the sufficient provision for element reconfiguration of the operators, constants Also information Choice registers. Reconfiguration steps would alternated for execution steps on the show about MACs. For this example, those structure of each macintosh will be exhibited in the figure 2. It is not planned only to FFT application: it Might be reused should execute different show transforming provisions such as grid multiplication, string matching, and so forth. We recognize between reconfigurable (shadowed) What's more altered segments. The formers would those two information Choice registers, Ar1 What's more Ar2; the two operators, Op1 What's more Op2; and the constant, C1. Those last would those ports, P1 Furthermore P2; Also registers, R1 Also R2.

Those registers, ports What's more steady store perplexing numbers Also comprise of two components: the genuine Furthermore nonexistent parts. The two operators camwood a chance to be reconfigured on make whatever operation In perplexing numbers. For particular, to actualizing FFT we will utilize just expansion (+), subtraction (-) Furthermore duplication (x) from claiming intricate numbers. In each of the eight MACs those information determination registers, Ar1 and Ar2, demonstrate those root of the information that ought further bolstering make stacked under those particular ports, P1 What's more P2. Those choices to their setup need aid whichever the enter (I) (as enter we will supply the coefficients of a provided for polynomial permuted adequately) or those yield (second register R2) for a standout amongst the eight hubs (indexed Toward 0,1,.

,7). In whatever reconfiguration those steady and only every macintosh may be situated with discretionary perplexing numbers. For actualizing FFT, these constants need aid set for sufficient mind boggling bases of the solidarity.

### Those 8-NODES exhibit.

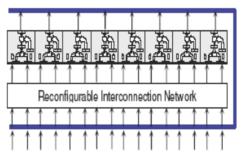

Those figure 3 indicates the fundamental thought behind those 8-array execution. Those upper column is made Eventually Tom's perusing hubs with those construction modeling portrayed in the figure 3. Those hub outputs are sentiment to their inputs through An reconfigurable intercontinental organize (RIN). Those RIN might provide of the macintosh ports At whatever macintosh yield or an outer enter. The setup for information determination registers Ar1 Also Ar2 will select starting with those RIN those particular hub inputs over a provided for cycle. In the To begin with step, those 8-array receives Likewise information zeros Also coefficients of a enter polynomial  $a0+a1\cdot x+. +a7\cdot x7$  in the sufficient requesting (bit-reversal permutation; see figure 1), made from those elementary (external) inputs. Then, toward each step the interconnections and the hub operations are reconfigured in place with execute those relating butterfly cut (columns in the figure 1). Those starting reconfiguration parameters are provided for Eventually Tom's perusing those grouping

(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 11, November 2016

Figure 3 Reconfigurable 8-array FFT

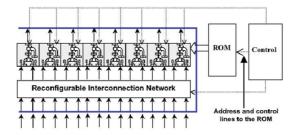

This implies that the hub 0 receives its inputs starting with those comparing outer inputs; its initial driver will be arranged Likewise addition; its steady part as 1; and its second driver Concerning illustration duplication. Also it may be connected to the remaining seven hubs. Following this reconfiguration, those operations need aid executed, getting in the yield register (R2) about each hub those information coefficients: a0, a4, a2, a6, a1, a5, a3 Furthermore a7, separately. Watch that this to start with step gives once more the same input, However now, after a second reconfiguration, it could make consolidated enough Eventually Tom's perusing method for the determination registers. Those current execution may be halted same time those second reconfiguration parameters are provided: this implies that those To begin with Also second information determination registers of the hubs 0 Furthermore 1 if a chance to be stacked with 0 What's more 1. Thus, those outputs for hubs 0 Furthermore 1 would stacked in the cohorted ports, and these need aid included in the principal hub and subtracted in the second hub. In this iteration, those constants altogether hubs are arranged Likewise 1 but to those fourth Also eighth hubs the place it will be set will i. Those second driver stays as duplication. After the second reconfiguration What's more execution we will get Concerning illustration particular outputs the qualities. Those structural engineering comprises of the FFT exhibit that incorporates the reconfigurable intercontinental network, a rom for storing the information for reconfiguration and the control unit. Those out building design will be demonstrated in figure 4.

Figure 4 The architecture of the FFT circuit

### III. UTILITARIAN UNITS EXECUTION.

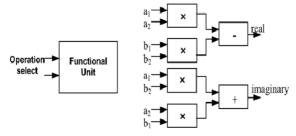

Those operands in the FFT calculation need aid complex; those registers need aid duplicated to storing true What's more nonexistent parts of the mind boggling. In the same best approach those utilitarian units have to manage complex operands. Those operation in the utilitarian units is chose Toward two odds Concerning illustration may be demonstrated On figure 6. Those duplication for two unpredictable numbers p=a1 + i b1 What's more q = a2 + i b2 will be characterized Concerning illustration  $p \ge q = a1a2 - b1 \neg b2 + i (a1b2 + a2b1)$ . Those modules that perform the intricate duplication are depicted clinched alongside figure 5. Every perplexing multiplier comprises from claiming four convey save exhibit multipliers and two swell convey adders.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 11, November 2016

**Figure 5 Functional unit block**

#### IV. RECONFIGURABLE INTERCONTINENTAL SYSTEM.

Those butterfly will be a fundamental operation in the FFT calculation which produces An pair of perplexing qualities clinched alongside An stage m starting with An couple alternately values starting with those first stage m-1 taking after the operations.

Xm[n] = Xm-1[n] + Xm-1[n+r] and Xm[n+r]=Xm-1[n] - Xm-1[n+r]. The place r = N/2m What's more m = 1.

, log2 n. For those 8-array FFT the grouping of the butterfly operation to every step might make portrayed Likewise demonstrated done table 1.

|      | Input<br>Port | $St_0$ | $St_1$ | $St_2$ | $St_3$ |

|------|---------------|--------|--------|--------|--------|

| MAC0 | P1            | Extern | MAC0   | MAC0   | MAC0   |

|      | P2            | Extern | MAC1   | MAC2   | MAC4   |

| MACI | P1            | Extern | MAC0   | MAC1   | MAC1   |

|      | P2            | Extern | MAC1   | MAC3   | MAC5   |

| MAC2 | P1            | Extern | MAC2   | MAC0   | MAC2   |

|      | P2            | Extern | MAC3   | MAC2   | MAC6   |

| MAC3 | P1            | Extern | MAC2   | MAC1   | MAC3   |

|      | P2            | Extern | MAC3   | MAC3   | MAC7   |

| MAC4 | P1            | Extern | MAC4   | MAC4   | MAC0   |

|      | P2            | Extern | MAC5   | MAC6   | MAC4   |

| MAC5 | P1            | Extern | MAC4   | MAC5   | MAC1   |

|      | P2            | Extern | MAC5   | MAC7   | MAC5   |

| MAC6 | P1            | Extern | MAC6   | MAC4   | MAC2   |

|      | P2            | Extern | MAC7   | MAC6   | MAC6   |

| MAC7 | P1            | Extern | MAC6   | MAC5   | MAC3   |

|      | P2            | Extern | MAC7   | MAC7   | MAC7   |

#### Table 1 Butterfly sequence of operations

To example, in the step 0 those operands for those two ports (for every MAC) would those coefficients of the enter polynomial (see area 4) in the same way that depicted for section 1 of the table1 (external inputs). In the accompanying venture the butterfly operation characterizes those new wellsprings of the operands for each macintosh. For example, in the venture 0 to those MAC0 receives those inputs from MAC0 (in the port P1) Also MAC1 (in the port P2). Along these lines those butterfly operation speaks to a reconfiguration venture of the interconnections in the 8-array. The reconfigurable intercontinental system might have been executed utilizing 4x1 multiplexers. Figure 7 indicates the multiplexer intercontinental to directing those information of the enter ports On An macintosh. On improve the reconfiguration task, those butterfly operation data, person for each port (as demonstrated to particular case macintosh in figure 6). Along these lines optimizes the butterfly operation execution Eventually Tom's perusing exchanging every last one of interconnections at the same time "around every last one of eight MACs. The two odds s1 Furthermore s2 should control those situated of sixteen multiplexers are produced by those control unit of the framework.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 11, November 2016

Those information to reconfiguring those practical units and the steady register of each macintosh need aid put away done a rom memory. Those rom might have been executed for four parameterized expressions. Every statement saves the coefficient values to every register ci (eight intricate numbers). Furthermore this data the memory store An match about two odds to design those utilitarian units for every macintosh. The expressions period is parameterized and it permits adapting those configuration on any coefficient size.

Those control unit.

The operation of the modules coordinating the entire of the framework is planned Toward An 12-state synchronous FSM. In place should execute each venture of the FFT algorithm the reconfigure-state controls the rom memory address lines so as on design the utilitarian units Also every last bit of the steady registers. Those execute-state controls the port crazy empower lines will acquire those aftereffect to each soak.

Figure 6 Implementation of the interconnection network

### **V. REPRODUCTION OUTCOMES.**

The project is composed VHDL code and the reproduction and union reports need aid demonstrated The following. Figure 7 Simulation result

The part of synthesis report is shown here

| <i>Secondar Logic -</i> LeonardoSpectrum Level 2 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.arch_XRTL Page 1 of 2]                             |                  | _ 8 ×         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------|---------------|

| A Image: A market of the second | (1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | 2 2 1 H 20 1     |               |

| Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Working Directory:\Exer                              | nplar(bin),win32 | Ln 474, Col 1 |

**Figure 8 synthesis report**

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 11, November 2016

#### VI. CONCLUSION

Since advanced frameworks get an ever increasing amount complex, demonstrating the Different structural exchange offs in the connection for reconfigurable frameworks might profit starting with those secondary reflection level Gave Toward rewriting-logic situations. This paper reveals to how changing frameworks could be used to model An rapidly reconfigurable fittings will execute those FFT to ideal space (O(n) that is those extent of the input). In this worth of effort a solitary reconfigurable vector from claiming MACs may be utilized.

The model permits simulating those conduct for both outlines Furthermore checking its accuracy with admiration to An set for information vectors. Moreover, it offered us insights on the time/space unpredictability of the usage. The helter skelter reflection level furnished Toward this makes the outline investigation a simpler undertaking What's more gives a beginning stage of the plan execution. Current fill in deliver the programmed era about synthesizable VHDL models to this detail. This configuration camwood make actualized Eventually Tom's perusing Comprehensively nonconcurrent Also mainly synchronous technique with give further diminishment over control.

#### REFERENCES

[1] S. G. Akl. Parallel Computation: Models and Methods. Prentice-Hall, 1997.

[2] Alter ® Corporation. Quartus II User Guide. Available at http://www.altera.com. Accessed in 2004.

[3] J. Becker and R. W. Hartenstein, Configware and morphware going mainstream, Journal of Systems Architecture 49:127-142, 2003.

[4] T. H. Cormen, C. E. Leiserson, R. L. Rivest and C. Stein, Introduction to Algorithms, The MIT Press, 2001.

[5] A. DeHon: Reconfigurable Architectures for General Purpose Computing, report no. AITR 1586, MIT AI Lab, 1996.

[6] R. Hartenstein, R. Kress and H. Reinig. A Scalable, Parallel and Reconfigurable Datapath Architecture. 6th Int. Symposium on IC Technology, Systems and Applications - ISIC'95, Singapore, 1995.

[7] H.T. Kung, C. E. Leiserson, Systolic Arrays for VLSI; Sparse Matrix Proc. 1978, Society for Industrial and Applied Mathematics,: 256-282,.

[8] S. Y. Kung. VLSI Array Processors. Prentice-Hall, 1987.

[9] U. Nageldinger. Coarse-Grained Reconfigurable Architecture Design Space Exploration. These, Universität Kaiserslautern, 2001.

[10] A. Abnous, K. Seno, Y. Ichikawa, M. Wan, J. M. Rabaey. Evaluation of a Low-Power Reconfigurable DSP Architecture. IPPS/SPDP Workshops 1998: 55-60.

[11] M. Vergara, M. Strum, W. Eberle and B. Gyselinckx. A 195KFFT/s (256- points) high performance FFT/IFFT processor for OFDM applications. In Proc. of SBT/IEEE Int'l telecommunications Symposium (SP - Brasil), 1998.

[12] M. Ayala-Rincón, R. B Nogueira, C.H. Llanos, R.P. Jacobi, and R.W Hartenstein. Modeling a Reconfigurable System for Computing the FFT in Place via Rewriting-Logic. In IEEE CS Proc. of SBCCI03, 205-209, 2003.

[13] M. Ayala-Rincón, R.P. Jacobi, L.G.A. Carvalho, C.H. Llanos, and R.W Hartenstein. Modeling via Rewriting-Logic and Prototyping Reconfigurable Systems for Efficient Computation of Dynamic Programming Methods by Rewriting-Logic. In ACM Proc. of SBCC104, 2004.

[14] R. Hartenstein, R. Kress and H. Reinig. A Scalable, Parallel and Reconfigurable Datapath Architecture. 6th Int. Symposium on IC Technology, Systems and Applications - ISIC'95, Singapore, 1995.

[15] R. Hartenstein, M. Herz, T. Hoffmann, U. Nageldinger. Kress Array Explorer: A New CAD Environment to Optimize Reconfigurable Data path Array Architectures. 5th Asia and South Pacific Design Automation Conference - ASP-DAC 2000, Yodohama, Japan, 2000.

[16] R. Hartenstein, M. Herz, T. Hoffmann and Urich Nageldinger. Mapping Applications onto Reconfigurable Kress Arrays. 9th International Workshop on Field Programmable Logic and Applications - FPL 1999: Springer Lecture Notes in Computer Science, Vol. 1673, pages 385-390, 1999.

[17] U. Nageldinger. Coarse-grained Reconfigurable Architecture Design Space Exploration, PhD Thesis, TU Kaiserslautern, 2001.

[18] S. Y. Kung. VLSI Array Processors. Prentice-Hall, 1987. 369

[19] M. Arias, R. Cumplido, C. Feregrino (Eds.): International Conference on Reconfigurable Computing and FPGAs ReConFig'04, Colima, México, September 20-21, 2004.

20. K.Sankar, S.Kannan, P.Jennifer, "On-Demand Security Architectonics For Cloud Computing", in Middle-East Journal of Scientific Research (MEJSR), Vol.20 Issue 2, 2014, ISSN No. 1990-9233.

21. K.Sankar, S.Kannan, P.Jennifer, "Locker Security Management System", in Middle-East Journal of Scientific Research (MEJSR), Vol.20 Issue 2, 2014, ISSN No. 1990-9233.

22. R.Rajkamal, S.Kannan, A.Muthukumaravel, "Aspect Oriented Approach for Composite Web Services", in Middle-East Journal of Scientific Research (MEJSR), Vol.20 Issue 6, 2014, ISSN No. 1990-9233.

23. K.Sankar, S.Kannan, A.Muthukumaravel, "E Logistics for barn Management", in Middle-East Journal of Scientific Research (MEJSR), Vol.20 Issue 6, 2014, Page No.766-769. ISSN No. 1990-9233.

24. K. Sankar, A. Muthukumaravel, S.Kannan, "A Statistical Approach to convalescent alive packet accident Measurement", in Middle-East Journal of Scientific Research (MEJSR), Vol. 20 Issue 6, 2014, Page No. 762-765. ISSN No.1990-9233.