## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 9, September 2016

# Design of CMOS 8-bit Comparator with Efficient VLSI Design Constraints

Gotru Angel Priyanka <sup>1</sup>, Buralla Muralikrishna <sup>2</sup>, Bhaskara Rao Doddi <sup>3</sup>

P.G. Student, Dept. of Electronics & Communication Engineering, Visakha Engineering College, Narava, A.P, India<sup>1</sup> Associate Professor, Dept. of Electronics & Communication Engineering, Visakha Engineering College, A.P, India<sup>2</sup> Assistant Professor, Dept. of Electronics & Communication Engineering, Visakha Engineering College, A.P, India<sup>3</sup>

**ABSTRACT**: We present a Comparator with less Transistor count and low power by having less Active number of Transistors. There are less number of Transistors in series such that by default Speed can be better. Total number of transistor count for N-bit is (N-1)\*20+6+6+4. The idea is to provide new way of Circuit Designing in Transistor level by without even forming the equations. CMOS logic style which is being dominant in Industry is being considered for designing the Circuit which has the Prime Disadvantage of occupying more Area and this corresponds to number of Transistors at the Circuit level. Total number of cells required for the Design are also very less such that it will be helpful for the Layout, though a manual or Automated Layout. Circuit which we have designed also has uniform structure. Circuit was designed by using S-EDIT tool for Schematic entry and T-SPICE for Simulation of TANNER EDA tool.

KEYWORDS: 10T BlockEven, 10T BlockOdd, Comparator, CMOS.

## I. Introduction

Low density parity check (Ldpc) was designed by gallager in 1962[1]. Implementation of ldpc decoder has efficient Speed constraint but other constraints of VLSI. comparator is important module in decoder.C-H HUANG developed priority encoder based on logic and module which has efficient Speed and power but at expense of Area[2]. S-W CHENG employed Mux based Design and their design is designed at gate level and total number of levels are less which will improve the Performance [3]. J-Y KIM and H-J YOO proposed a design used dynamic logic which can lead to lack of full-output voltage swing and this might be inefficient when the Technology is scaled down[4].

Add-Compare-Select block will be performing three different operations like Addition, Comparison and Multiplexing, here asynchronous logic is being employed without under the control of the clock[5]. Static Cmos will be having power rails and thus they have good noise immunity when compared to Dynamic logic[6]. If we want to design High performance circuit there should be more Parallelism[7].

Any expression can be directly translated into equivalent transistor level CMOS Circuit [8]. Geetanjali Sharma comparator is based on gate level circuit designing which might not give the maximum [9]. Saleh Abdel Hafeez proposed high speed comparator at expense of Area but used transmission gates logic which does not have any power rails and leads to a less noise immunity[10].

VLSI has a trade-off among the design constraints like Area, Power and Speed so any two constraints in general will be kept in mind and making sure that low priority constraint is not that neglected. Here we are not interested in universal gate based design instead we want to propose design which can be extendable to N-bit.

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 9, September 2016

#### II. RELATED WORK

Comparator with High Speed as well as less Power consumption but More Area was being proposed they have less number of levels lead to high Speed and when Output is known, portion of the Circuit which is not needed to calculate the output will be deactivated leading to less Switching activity which in turn less Power consumption their design is Static and they have used basic CMOS cells and their Maximum Fan-in is 5, Maximum Fan-out is 4 and Maximum Transistor count is 20 and we can identify whether A>B or A<B or A=B and total Active number of Transistors for 64-bit is 944 [10].

Comparator with High Speed as well as less Area was being proposed they have less number of levels lead to high Speed, design required basic logic gates and Multiplexers and their Maximum Fan-in is 3, Maximum Fan-out is 2 and Maximum Transistor count is 12 and we can identify whether A>=B or A<B and total Active number of Transistors for 64-bit is 778 [03].

Proposed Comparator has Low Area and design is Static and we have used our defined CMOS cells and their Maximum Fan-in is 4, Maximum Fan-out is 2 and Maximum Transistor count is 10 and we can identify whether A>B or A=B and total Active number of Transistors for 64-bit is 638, Obviously less number of Active Transistors means less will be the Power Consumption .

#### III. MAGNITUDE COMPARATOR

Comparator is going to compare 8 bits of A(A7 to A0) and 8 bits of B(B7 to B0) and decides whether ALTB(A<B) or AGTB(A>B) or AEB(A=B). Conventional Digital CMOS cells are not utilized in the Design .we need to know what are all the conditions for ALTB(A<B) to become true, if (A7<B7) then ALTB(A<B) should be true and 6T Block which has one not gate and one two input nand gate has been designed and nand gate has one output.

Now let us see the second condition that is if (A6<B6) and if (A7>B7) is false then ALTB(A<B) should be true, so we have designed another 6T Block for knowing the status of (A7>B7) and 10T BlockEven for (A<B) and this block has one output. Now the first condition for (A>B) which is (A7>B7) already available and the second condition that is if (A6>B6) and if (A7<B7) is false and we have this status from 6T Block then AGTB(A>B) should be true, and 10T BlockEven for (A>B) has been designed and this block has one output.

Now let us see the third condition for ALTB(A<B) that is if (A5<B5) and if 2-bit Greater then output is false then ALTB(A<B should be true and for this 10T BlockOdd is designed. Now let us see the third condition for AGTB(A>B) that is if (A5>B5) and if 2-bit less then output is false then AGTB(A>B) should be true and for this 10T BlockOdd is designed.

Now let us see the fourth condition that is if (A4 < B4) and if 3-bit greater then output is false—then ALTB(A<B) should be true, so we have designed another 10T BlockEven for this requirement. Now let us see the fourth condition that is if (A4 > B4) and if 3-bit less then output is false—then AGTB(A>B) should be true, so we have designed another 10T BlockEven for this requirement

Now let us see the fifth condition that is if (A3<B3) and if 4-bit greater then output is false then ALTB(A<B) should be true, so we have designed another 10T BlockOdd for this requirement. Now let us see the fifth condition that is if (A3>B3) and if 4-bit less then output is false then AGTB(A>B) should be true, so we have designed another 10T BlockOdd for this requirement

Now let us see the sixth condition that is if (A2<B2) and if 5-bit greater then output is false then ALTB(A<B) should be true, so we have designed another 10T BlockEven for this requirement. Now let us see the sixth condition that is if

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 9, September 2016

(A2>B2) and if 5-bit less then output is false then AGTB(A>B) should be true, so we have designed another 10T BlockEven for this requirement

Now let us see the seventh condition that is if (A1 < B1) and if 6-bit greater then output is false—then ALTB(A<B) should be true, so we have designed another 10T BlockOdd for this requirement. Now let us see the seventh condition that is if (A1 > B1) and if 6-bit less then output is false—then AGTB(A>B) should be true, so we have designed another 10T BlockOdd for this requirement

Now let us see the last condition that is if (A0 < B0) and if 7-bit greater then output is false then ALTB(A<B) should be true, so we have designed another 10T BlockEven for this requirement. Now let us see the last condition that is if (A0 > B0) and if 7-bit less then output is false then AGTB(A>B) should be true, so we have designed another 10T BlockEven for this requirement.

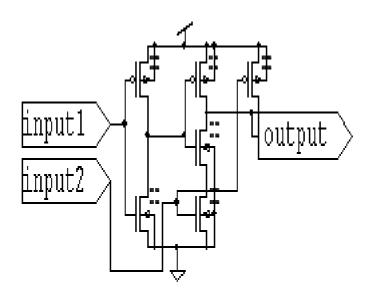

Fig.1 6TBlock

Fig1 is an 6Transistor Block Circuit which is required to know the less then(<) and greater then(>) Status at MSB stage, this Status is required at MSB-1 Stage of ALB(A<B) and AGB(A>B) and it requires 6 number of Transistors and this is one of the conditions and in fact the first condition which implies that when A7>B7 no need to know the values of remaining inputs AGB(A>B) Output will be True and same is the case for A7<B7.

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 9, September 2016

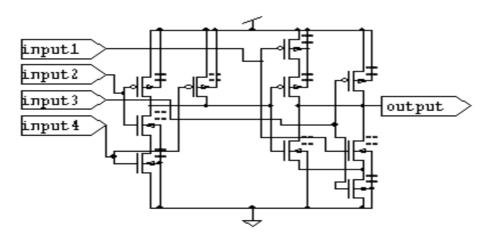

Fig.2 10TBlock(Even) Circuit

Fig2 is an 10Transistor BlockEven Circuit which is needed to get the Output of ALB(A<B) and AGB(A>B) at every EVEN bit position of the Primary inputs and it needs 10 number of Transistors.Input1 and Input2 corresponds to present bit positions and input3 and input4 corresponds to previous Status of ALB(A<B) and AGB(A>B) when used for ALB(A<B) and AGB(A>B) and ALB(A<B) when used for AGB(A>B) and this Block gives True output.

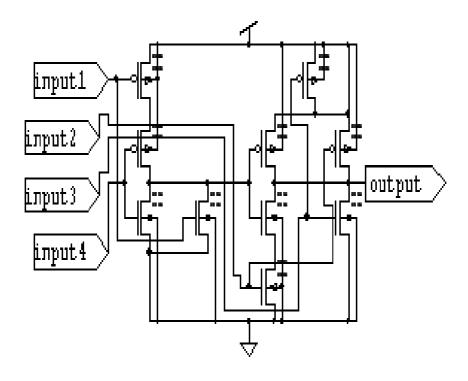

Fig.3 10TBlock(Odd )Circuit

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 9, September 2016

Fig3 is an 10T BlockOdd Circuit which is needed to get the output of ALB(A<B) and AGB(A>B) at every odd bit position of the Primary inputs and it takes 10 number of Transistors. Input1 and Input2 corresponds to present bit positions and input3 and input4 corresponds to previous Status of ALB(A<B) and AGB(A>B) when used for ALB(A<B) and AGB(A>B) and ALB(A<B) when used for AGB(A>B) and this Block gives False output.

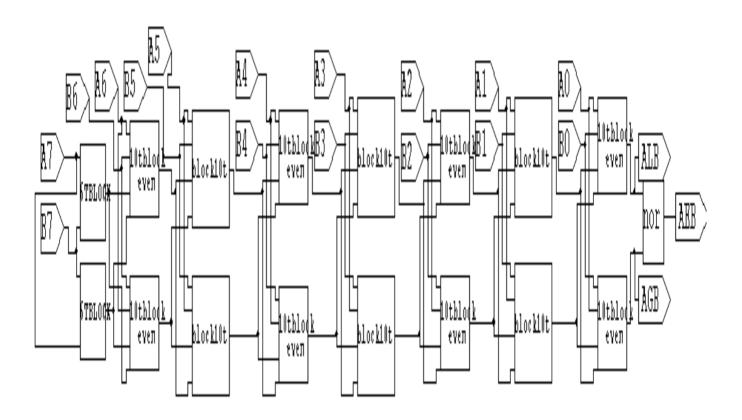

Fig. 4 Schematic of 156 transistor Comparator cell

Fig4 is schematic for 8-bit comparator Circuit which needs Two 6T Blocks, eight 10T Block evens, and six 10T Block Odds and one Nor gate, total Transistor count is ((2\*6)+(8\*10)+(6\*10)+(1\*4)) equals to 156. This Schematic has Transition of 01010101 and the last one corresponds to final output, if Designed for Odd(7) bit Comparator then 1010101 Transition has to be maintained to save many number of inverters.

### IV. STATIC CMOS

STATIC CMOS has the advantage of having very less Static power dissipation and static refers to for every input applied there will be possible path to activate the output, which is unlike in DYNAMIC logic which needs pre-charging and then only Evaluation phase can begin. Floor planning is very much essential as it will affect the chip Area required and we might need to go for Standard cell based Design in which the height of every cell is fixed and how much that can be depends on the cell which needed maximum height and this will be beneficial when the cells have to be merged. Since we have designed the circuit by only STATIC CMOS we can merge the cells more comfortably as it has Pull-up and Pull-down networks and these have equal number of Transistors. Transistors placed in series are going to increase the delay we can enhance speed by transistor sizing or by introducing buffer in which we need to sacrifice Area.

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 9, September 2016

#### V. PERFORMANCE ANALYSIS

8-bit magnitude comparator has been designed by using STATIC CMOS logic style. The comparator which we designed using STATIC CMOS logic style has less number of transistor count. Our design is extendable to N-bit, from MSB-{1,3,5,7} and so on 10T Blockeven is used and from MSB-{2,4,6} and so on 10T Blockodd is used. Total number of transistor count for N-bit is (N-1)\*20+6+6+4.

#### TABLE1 COMPARISON OF AREA IN THREE DESIGNS

| 64-bit                  | Design in  | Design in   | Design in  |

|-------------------------|------------|-------------|------------|

|                         | Reference3 | reference10 | this paper |

|                         |            |             |            |

|                         |            |             |            |

| (number of transistors) | 1556       | 2976        | 1276       |

|                         |            |             |            |

|                         |            |             |            |

Table 1 shows the comparison between S.W Cheng, Saleh Abdel Hafeez and the proposed Comparator. 1700 transistors were reduced when compared to Saleh Abdel Hafeez for 64-bit, almost in a equal proportion transistor count reduction will be there for N-bit and 280 transistors were reduced in comparison with S.W.Cheng, and count was less due to their logic can only identify '<' and '=' conditions which in contrast '<', '>' and '=' can be identified in others mentioned in Table.

### VI. CONCLUSION

Area is one of the important design constraint as it is proportional to the cost of the design. Since our design has less number of transistors total number of active transistors will be less and it is like only 50% of total transistors will be active, so only 638 transistors will be active for 64-bit. In Saleh Abdel Hafeez comparator only 32% of the total transistors are active but 944 are the active transistors for 64-bit. In equal proportion active transistor count will be there for our proposed design as well as in Saleh Abdel Hafeez design for N-bit.

we are able to design the comparator by using less number of transistors even though Static CMOS needs more number of transistors. It shows an 64-bit comparator of the proposed technique only needs 1276 transistors, the technique which we presented can be easily extendable up to N-bit and some Design Techniques to be implemented to ensure that Delay is better

#### REFERENCES

- [1] R G Gallager, "low-density parity-check code," IEEE Transaction Theory, 1962,8(1), pp. 21-28.

- [2] Chung-Hsun Huang and Jinn-Shyan Wang,"High-Performance and Power-efficient CMOS Comparators,"Solid-State Circuits, IEEE Journal of,vol.38,no.2,pp. 254-262, Feb 2003.

- [3] S.W Cheng, "High-Speed magnitude comparator with Small transistor count," Electronics, Circuits and Systems, 2003. ICECS 2003. Proceedings of the 2003 10<sup>th</sup> IEEE International Conference on, vol.3,no.,pp.1168-1171, 14-17 Dec. 2003.

- [4] Joo-Young Kim and Hoi-Jun Yoo, "Bitwise Competition Logic for compact digital comparator, "Solid-State Circuits Conference, 2007.ASSCC '07. IEEE Asian, vol.,no.,pp.59-62,12-14 Nov. 2007.

- [5] B. Zhao, Y.Hei, and Y.L. Qiu, "An asynchronous add-compare-select design in CMOS VLSI," ASIC,2003. Proceedings. 5<sup>th</sup> International Conference on, vol2, pp. 1277-1280, 21-24 oct. 2003.

- [6] Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic, "Digital Integrated Circuits A Design Perspective," Second Edition, Pearson Education, 2003.

## International Journal of Innovative Research in Science, Engineering and Technology

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 9, September 2016

- [7] M.M. Mano, Digital Design. Englewood CLIFFS,NJ: Prentice-Hall, 1991,ch.5.

- [8] N. West and K. Eshraghian, Principles of CMOS VLSI Design. Reading, MA: Addison-Wesley, 1993,ch.8.

- [9] Geetanjali Sharma, Uma Nirmal, Yogesh Mishra, "A Low Power 8-bit Magnitude Comparator With Small Transistor Count using Hybrid PTL/CMOS Logic" in IJCEM International Journal of Computational Engineering & Management Vol 12, April 2011, pp.110-115 ISSN(Online): 2230-7893.

- [10] Saleh Abdel-Hafeez, Ann Gordon-Ross, Behrooz Parhami Scalable Digital CMOS Comparator Using a Parallel Prefix Tree In IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION(VLSI)SYSTEMS, VOL. 21, NO. 11, NOVEMBER 2013.