(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijirset.com</u> Vol. 6, Issue 9, September 2017

# FPGA based Implementation of MAC in Parallel Filter

Nusratjabeen M. Anees<sup>1</sup>, Ashish B. Kharate<sup>2</sup>

PG Student, Department of Electronics and Telecommunication Engineering, Sant Gadge Baba Amravati University,

Maharashtra, India<sup>1</sup>

Assistant Professor, Department of Electronics and Telecommunication Engineering, H.V.P.M'S College of

Engineering, Maharashtra, India<sup>2</sup>

**ABSTRACT**: Due to the explosive growth of multimedia application, the demand for high performance and low power DSP is getting higher and higher. Most widely used fundamental device performed in DSP system is FIR digital filter. Being the critical part of the theoretical advancement and implementation, FIR filter design continues to be a critical area of on-going research activities.For better performance it is good direction to optimize power consumption , reduction in computational complexity as well as area optimization of FIR digital filter.

**KEYWORDS**:, FIR filter, Area optimization , MAC, FPGA.

#### I. INTRODUCTION

The speed of developments in electronic technology is taking place tremendously. Now a days, Digital Signal Processing (DSP) is used in various applications such as speech processing, digital versatile disk, portable video systems/computers, digital audio, multimedia and wireless communications, video compression, digital set-top box, cable modems, digital radio, transmission systems, radar imaging, acoustic beam formers, global positioning systems, and biomedical signal processing. The field of DSP has always been driven by the advances in DSP applications and in scaled very-large-scale integrated (VLSI) technologies. Therefore, at any given time, several challenges are imposed on the implementations of the DSP systems. These implementations must satisfy the enforced sampling rate constraints of the real-time DSP applications and must require less space and power consumption. DSP computation is different from general-purpose computation in the sense that the DSP programs are non terminating programs. In DSP computation, the same program is executed repetitively on an infinite time series. The non terminating nature can be exploited to design more proficient DSP systems by exploiting the dependency of tasks both within iteration and among multiple iterations. in addition, long critical paths in DSP algorithms limit the performance of DSP systems. Digital filters are essential elements of DSP systems. Digital filters are classified into two categories as: Finite Impulse Response (FIR) filter and Infinite Impulse Response (IIR) filter. Though FIR filters have linear phase property, low coefficient sensitivity and stability compare to IIR filter they have power consumption more than IIR filter. In many applications it is often advantageous to employ finite impulse response (FIR) filters, since they can be designed with exact linear phase and reveal no stability problems (Mitra, 2006). However FIR filters have a computationally more intensive complexity compared to infinite impulse response (IIR) filters with correspondent magnitude responses. During the past several years, many design methods have been proposed to reduce the complexity of the FIR filters.

### **II. DIGITAL FILTER**

The output of a FIR filter is described by the following equation:

$$y[n] = a_0 x[n] + a_1 x[n-1] + \dots + a_{N-1} x[n-N]$$

(An ISO 3297: 2007 Certified Organization)

Website: <u>www.ijirset.com</u>

Vol. 6, Issue 9, September 2017

Where x[n] is the input signal, y[n] is the output signal.  $a_i$  are the filter coefficients, also known as tap weights, that make up the impulse response. The output y of a FIR system is determined by convolving its input signal x with its impulse response.

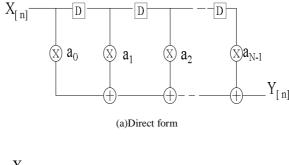

Fig.1 Various Realizations of FIR Filters

In general, there are two popular forms to realize FIR filters: direct and transposed shown in Fig. 1. In the direct form, there are delay units between multipliers. At a time, the present filter input, x(n), and N-1 previous samples of the input are fed to each multiplier input, and the filter output y(n) is the sum of product of every multiplier. In the transposed form, however, delay units are placed between adders so that the multipliers can be fed simultaneously. For the computation of FIR filter, we have to convolve the input data with filter coefficient, convolution process contains number of multiplication and addition.

#### **III. LITERATURE REVIEW**

Computational complexity of Digital Filter structures is given by total number of multipliers and total number of two input adders required for its implementation, which indicates cost of implementation. For the applications demanding low power and high speed Digital Filters, various approaches developed so far to reduce the number of multiplications and additions are discussed below.

Strength reduction at algorithmic level can be used to reduce the number of additions and multiplications. Applications involving multiplication by constant are common in digital signal processing. A first solution proposed to optimize multiplication by constant was the use of constant recoding, such as Booth's. This solution just avoids long strings of consecutive ones in the binary representation of the constant. Another solution proposed designing a digit-serialMCM operation with minimal area at gate-level and presents the exact formalization of the area optimization problem as a0-1 Integer Linear Programming (ILP) problem[3].

In the paper titled "Low-Complexity Constant Coefficient Matrix Multiplication Using a Minimum Spanning Tree Approach", proposed an algorithm for low complexity constant coefficient matrix multiplication based on differences. It uses a minimum spanning tree (MST) to select the coefficients, which warrants low execution time as an MST can be found in polynomial time[14]In general, optimization techniques usually used for multiplier less filter design are complex, can require long run times, and provide no performance guarantees (Koter at al., 2003). GordanaJovanovicDolecek and Sanjit K. Mitra in their paper titled "Computationally Efficient Multiplier-Free Fir Filter Design", proposed simple efficient method for the design of multiplier-free.FIR filters without optimization. The method uses the rounding to the nearest integer of the coefficients of the equiripple filter which satisfies the desired

(An ISO 3297: 2007 Certified Organization)

Website: www.ijirset.com

#### Vol. 6, Issue 9, September 2017

specification. Considering that the integer coefficient multiplications can be accomplished with only shift-and-add operations, the rounded impulse response filter is multiplier-free[2].

In a FIR context, a MAC is the operation of multiplying a coefficient by the corresponding delayed data sample and accumulating the result. FIR usually requires one MAC per tap. High speed and high throughput Multiplier-Accumulator(MAC) unit that consumes low power, which is always a key to achieve a high performancedigital signal Processing system. A low power MAC unit can be designed and implementedusing block enabling technique to save power. In any MAC unit, data flows from the input register to the output register through multiple stages such as, multiplier stage, adder stage and the accumulator stage. Within the multiplier stage, further, there are multiple stages of addition. During each operation of multiplication and addition, the blocks in the pipeline may not be required to be on or enabled until the actual data gets in from the previous stage. In block enabling technique, the delay of each stage is obtained. Every block gets enabled only after the expected delay. For the entire duration until the inputs are available, the successive blocks are disabled, thus saving power[8].

### IV. PROPOSED METHODOLOGY

In many applications it is often advantageous to employ finite impulse response (FIR) filters, since they can be designed with exact linear phase and exhibit no stability problems (Mitra, 2006). However FIR filters have a computationally more intensive complexity compared to infinite impulse response (IIR) filters with equivalent magnitude responses. This paper aims to design an area efficient digital filter on FPGA .which has following steps described below.

## 1. Filter specification

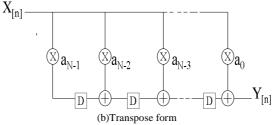

The first step in designing digital filters is to obtain the filter specification. The specification is developed based on the technical requirements to the filter and the possibility of hardware realization. A filter specification is a technical specification that determines the pass-band and stop-band frequency ranges and acceptable attenuations in those ranges. There are four basic types of filter specifications, one for each of the four basic filter types: low-pass, high-pass, band-pass and band-stop. Generally, filter specifications determine pass band and stop band frequency ranges, desirable signal attenuations (gains) at those ranges, approximation methods for the filter design, and hardware implementation requirements. FDA tool is used to design and analyse the filter for specification as shown in figure 2. Order N=17

PassbandFrequency Fpass = 9000Hz Stopband Frequency Fstop = 11000Hz Sampling Frequency Fs = 48000Hz

Fig.2 Filter specification in FDA tool

(An ISO 3297: 2007 Certified Organization)

Website: <u>www.ijirset.com</u>

### Vol. 6, Issue 9, September 2017

### 2. Filter coefficient generation

This design is exported to MATLAB workspace for generation of coefficient since coefficients are decimals, among them some are negative therefore binary representation of coefficient requires more bits as compared to integer. so coefficients are rounded to nearest integer value that can be represented in 8 bits only. This method reduces complexity of MAC unit considerably by avoiding design of two scompliment circuit further area requirement of multiplier is also reduced. Following table shows actual coefficient and rounded coefficient.

| coefficients | actual  | After rounding | off |

|--------------|---------|----------------|-----|

| h o          | -0.0602 | 5              |     |

| h 1          | -0.0240 | 2              |     |

| h 2          | 0.0432  | 3              |     |

| h 3          | 0.0348  | 3              |     |

| h 4          | -0.0196 | 2              |     |

| h 5          | -0.0916 | 7              |     |

| h 6          | -0.0130 | 1              |     |

| h 7          | 0.1928  | 1              | 5   |

| h 8          | 0.3879  | 3              | 0   |

| h 9          | 0.3879  | 3              | 0   |

| h 1 0        | 0.1928  | 1              | 5   |

| h 1 1        | -0.0130 | 1              |     |

| h 1 2        | -0.0916 | 7              |     |

| h 1 3        | -0.0196 | 2              |     |

| h 1 4        | 0.0348  | 3              |     |

| h 1 5        | 0.0432  | 3              |     |

| h 1 6        | -0.0240 | 2              |     |

| h 1 7        | -0.0602 | 5              |     |

Table.1Coefficient optimization by rounding to nearest integer.

## 3. Design of FIR filter using single MAC unit

In digital signal processing, the multiply–accumulate operation is a common step thatcomputes the product of two numbers and adds that product to an accumulator. The hardware unit that performs the operation is known as a multiplier accumulator (MAC or MAC unit). The operation itself is often called as a MAC or a MAC operation. The MAC operation modifies an accumulatoras:

$a \leftarrow a + (b \times c)$

This paper proposed an area efficient FIR filter by using a single MAC unit. Following block diagram shows construction of MAC based FIR filter.

#### Fig.3 Proposed Architecture of FIR filter using MAC

The architecture of MAC based FIR filter involvesdesign of following elements

- a. **Shift register:**This is serial in parallel out shift register. The effect of each clock pulse is to shift the data contents (x) of each stage one place to the right.

- b. **Multiplexer:** multiplexer or mux is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. Proposed architecture involves design of two mux one is to select data(x) and another to select filter coefficients (h). Selected input is depending upon the logic on selector pins.

- c. **Multiplier:**The output of two multiplexer is fed to multiplier.this multiplier takes 8 bit input and produces 16 bit output.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijirset.com

### Vol. 6, Issue 9, September 2017

- d. Adder: It adds multiplier output with previous result stored in accumulator. Output of adder is taken as filter output for current sample and also fed to the accumulator for next input sample.

- e. Accumulator: It is 32 bit D flip flop used to hold the result. with each clock existing value in accumulator is replaced by new one.

- f. **Controlunit:** This unit is of great importance as it controls all clock, reset signal associated with various elements as shown in fig 3 as well as logic on selector pins.

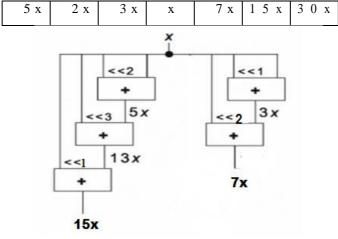

### 4.Design of FIR filter using MCM operation

From the above table it is cleared that filter coefficients satisfy following relation.

h(n) = h(N-n)

among two structures discussed above ,transposed form (parallel) filter is advantageous over direct form because it involves addition followed by multiplication and the multipliers can be fed simultaneously. Multiplication of a variable with a set of constants, known also as the MCM operation

In hardware, the multiplication operation is considered to be expensive, as it occupies significant area.

Constant multiplications are generally realized using only addition, subtraction, and shift operations. In our design following MCM operation has to be implemented.

Fig.4.Implementation of MCM operation

# V. IMPLEMENTATION

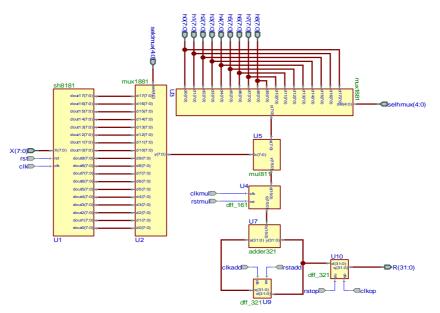

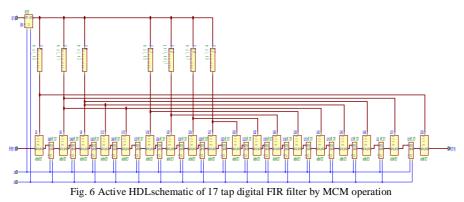

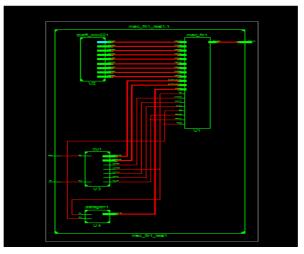

Each element described above is coded in active hdl and verified by their waveform separately, generated blocks are then unified to make proposed architecture shown in figure 5 and 6. All codes associated with design are exported in Xilinx for implementation on FPGA and corresponding device utilisation summary is generated for analysis.

(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijirset.com</u> Vol. 6, Issue 9, September 2017

Fig.5Active HDLschematic of17 tap digital FIR filter using MAC

Fig.7.RTLschematic view of 17 tap digital FIR filter using MAC

(An ISO 3297: 2007 Certified Organization)

Website: <u>www.ijirset.com</u>

Vol. 6, Issue 9, September 2017

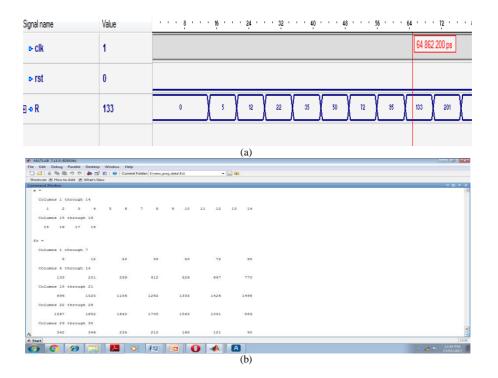

### VI. EXPERIMENTAL RESULTS AND ANALYSIS

Fig. 8.Filter output (a) simulation result in Active HDL (b) result in MATLAB for verification

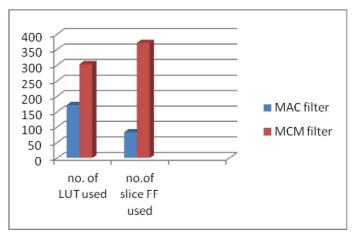

Fig.9.Area analysis graph

Area analysis graph shown above gives comparison between MAC based and MCM filter of same tap in terms of area requirement .It indicates that area requirement in implementation of FIR filter using MAC unit needs near about 50% as that of MCM filter.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijirset.com

#### Vol. 6, Issue 9, September 2017

#### VII. CONCLUSION

The FIR filters are widely used in signal processing and can be implemented using Programmable digital processors. But in the realization of large order filters the speed, cost, and flexibility is affected because of complex computations. This paper mainly describes the design and simulation of 17 tap low pass digital FIR filter using single Mac unit and transposed form (parallel) structure using MCM operation. FIR filter coefficients design has been performed by using MATLAB. VHDL has been used to enter hardware description. To test the correctness of the design the observed output is compared with the calculated output results from MATLAB that confirms the effectiveness of the design. VHDL codes have been written, synthesized, mapped then successfully configured and prototyped. FIR filter designed fully complies with design requirements.

#### REFERENCES

- [1] Ahmed Shahein, , Qiang Zhang, NiklasLotze, and YiannosManoli," A Novel Hybrid Monotonic Local Search Algorithm for FIR Filter Coefficients Optimization" IEEE Transactions on circuits and systems—I: regular papers, vol. 59, no. 3, march 2012.

- GordanaJovanovicDolecek, and Sanjit K. Mitra "Computationally Efficient Multiplier-Free Fir Filter Design", Computation y Sistemas Vol. 10 No. 3, 2007, pp 251-267 ISSN 1405-5546.

- [3] LeventAksoy and CristianoLazzari, Eduardo Costa, Paulo Flores and Jose Monteiro" Optimization of Area in Digit-Serial Multiple Constant Multiplications at Gate-Level" 978-1-4244-9474-3/11/ ©2011 IEEE

- [4] ShahnamMirzaei, AnupHosangadi, Ryan Kastner "FPGA Implementation of High Speed FIR FiltersUsing Add and Shift Method"1-4244-9707-X/06/©2006 IEEE

- [5] Keshab K. Parhi, , "Approaches to Low-Power Implementations of DSP Systems," IEEE Transactions on circuits and systems—I: Fundamental Theory and applications, Vol. 48, No. 10, October 2001, pp.1214-1224.

- [6] A. G. Dempster and M. D. Macleod, "Use of minimum-adder multiplier blocks in FIRdigital filters," IEEE Trans. Circuits Syst.-II, vol. 42, no. 9, pp. 569–577, Sep. 1995.

- [7] K.K.Parhi, "VLSI Digital Signal Processing systems-Design and Implementation", Wiley Student Edition.

- [8] Y. Voronenko and M. Piischel, "Multiplierless Multiple Constant Multiplication," ACM Transactions on Algorithms, vol. 3, no. 2, 2007.

- [9] Shanthala and Y.V.Kulkarni, "VLSI Design and Implementation of Low Power MAC Unit with Block Enabling Technique", in European Journal of Scientific Research, (2009), pp. 19-28.

- [10] Mitra S.K. Digital Signal Processing (PHI).

- [11] Shraddha S. Borkar "Optimization of FIR digital filter using low power MAC "IJCSET |April 2012| Vol 2, Issue 4,1150-1154.

- [12] J. Bhasker "VHDL Primer", Prentice-Hall, Inc, 1999.

- [13] Volnei A Pedroni "Circuit Design with VHDL", MIT Press, 2004.

- [14] O. Gustafsson, H. Johansson, and L. Wanhammar, "An MILP approach for the design of linear-phase FIR filterswith minimum number of signed-power-of-two terms," in Proc. Eur. Conf. Circuit Theory Design.