(A High Impact Factor & UGC Approved Journal) Website: <u>www.ijirset.com</u> Vol. 6, Issue 9, September 2017

# Supporting Dynamic Inode Allocation and Save Significant Storage Space in Mobile Computing System

V.Uma Rani<sup>1</sup>, Dr. B.Sateesh Kumar<sup>2</sup>, J.Shireesha<sup>3</sup>

Associate Professor, School of Information Technology (JNTUH), Kukatpally, District Medchal, Telangana, India<sup>1</sup>

Associate Professor, JNTUH College of Engineering, Jagitial, District Karimnagar, Telangana, India<sup>2</sup>

M.Tech Scholar, School of Information Technology (JNTUH), Kukatpally, District Medchal, Telangana, India<sup>3</sup>

**ABSTRACT:** PCM is rapidly evolved as a promising candidate for subsequent-technology storage class reminiscence (SCM) because of its non-volatility, byte-addressability, and high get admission to overall performance. In recent years, researchers have studied the way to use PCM as primary memory or hybrid fundamental reminiscence to improve the gadget overall performance and power efficiency. Although some research has explored the read/write asymmetry of PCM to further optimize the performance of PCM, the use of PCM as important memory suffers from the write endurance issue. As for the gap usage of record machine designs, some of previous research proposed different control designs to enhance the space utilization of file systems over block-primarily based garage devices. However, to the high-quality of our knowledge, little research has been executed trying to optimize the gap utilization of record systems through taking gain of the best features of PCM. In this paper we suggest a multi-grained block management approach to improve the space usage of report structures over PCM-based storage systems with minimized space and control overheads.

### I. INTRODUCTION

Solid State Storage (Storage Class Memory) is right here to stay. Today, a widely recognized Solid State Storage generation is NAND flash. Another technology on the horizon is Phase Change Memory (PCM). Both may be used in chip shape, for instance, as a small storage element in a portable tool. The study and write latencies of PCM cells are very low, already inside the identical ballpark as DRAM. For large scale storage, many chips may be packaged right into a single tool that gives the same capability as disk drives, supporting the same basic APIs. SSDs can provide a lot quicker random I/O than magnetic disks because there is no mechanical latency among requests. We recognition right here on database programs that call for business enterprise stage garage on this form aspect. NAND flash era is notably mature and represents the state-of-the art within the marketplace. Companies were constructing storage gadgets out of flash chips for 2 a long time, and one could discover a big variety of flash-primarily based devices from customer to corporation garage. PCM is a relative newcomer, and till now there has been little possibility to assess the performance characteristics of big scale PCM devices. The reason of this paper is to provide insights on in which stable country devices can offer a huge gain over traditional storage and to focus on viable variations between two consultant technologies, flash and PCM. Flash devices have superior random study performance compared to magnetic difficultdrives but be afflicted by numerous obstacles. First, there is a sizeable asymmetry in read and write performance. Second, most effective a confined range of updates may be carried out on a flash tool earlier than it will become unusable; this range is decreasing with more recent generations of flash. Third, writing on flash no longer best is a great deal slower than studying and adverse of the device, but it has validated to intrude with the redirection software layers, known as Flash Translation Layers (FTL). PCM addresses a number of these challenges. The staying power of PCM cells is notably better than NAND flash, although still now not close to that of DRAM. Unlike NAND flash, PCM does no longer require the bulk erasure of huge reminiscence units earlier than it is able to be rewritten. Moreover, whilst value is still uncertain, for our functions, we expect normal mobile size competitiveness and widespread quantity economics will apply to this generation because it ramps into high extent. The most mentioned gain of solid country

(A High Impact Factor & UGC Approved Journal)

Website: <u>www.ijirset.com</u>

#### Vol. 6, Issue 9, September 2017

storage over hard disks is the difference in response time for random accesses. Hence, we perceive dependent reads as a get entry to sample that has the ability for tremendous performance gains. Latency-bound programs like route processing in the context of graph processing, or RDF-statistics processing are usual examples of programs with such get right of entry to styles. The Resource Description Framework (RDF) information model is widely adopted for several on line, clinical or information-based totally datasets because of its simplicity in modeling and the sort of facts it may represent. We locate that PCM-primarily based storage is an essential step in the direction of higher latency ensures and not using a bandwidth penalties and we pick out a trade-off among maximizing bandwidth and minimizing latency. In order to measure the headroom of performance advantage (lower of reaction time) in long course queries we put into effect a easy benchmark and we evaluate the reaction times while using flash and PCM. We take a look at that PCM can yield 1.5x to two.5x smaller reaction instances for any bandwidth utilization with none graph conscious optimizations1 some of which we leave for destiny paintings. We take this observation one step similarly and we layout a new facts layout appropriate for RDF information and optimized for a strong nation garage layer. The proposed format will increase the locality of related records and reduces the price of graph traversals by storing more linkage records (i.e., metadata approximately the way to navigate faster while a graph is traversed). In this paper we show the benefits of course processing programs over data that is resident in solid country storage. First, we gift a custom graph benchmark this is used to highlight the differences among two solid nation technologies via representative gadgets: a ultra-modern flash tool and an business enterprise-stage PCM prototype furnished to us through Micron. Second, we increase a prototype RDF repository to expose the advantages that RDF processing will have if it adopts PCM storage.

#### II. RELATED WORK

Memory scaling is in jeopardy as rate storage and sensing mechanisms grow to be much less dependable for conventional reminiscence technology, such as DRAM. In evaluation, segment trade reminiscence (PCM) garage relies on scalable cutting-edge and thermal mechanisms. To take advantage of PCM's scalability as a DRAM alternative, PCM should be architected to deal with pretty lengthy latencies, excessive energy writes, and finite endurance. We advocate, made from a fundamental knowledge of PCM era parameters, vicinity-neutral architectural improvements that deal with these barriers and make PCM competitive with DRAM. A baseline PCM machine is 1.6x slower and requires 2.2x extra energy than a DRAM machine. Buffer reorganizations reduce this delay and power hole to at least one.2x and 1.0x, the usage of slender rows to mitigate write electricity and more than one row to enhance locality and write coalescing. Partial writes decorate reminiscence staying power, imparting 5-6 years of lifetime. Process scaling will further reduce PCM energy prices and enhance patience. We offer a rigorous survey and derivation of segment exchange reminiscence houses to force architectural research and enhancements. Architecturally relevant parameters are expressed inside a DDR framework to facilitate a DRAM contrast. This comparison located that PCM's lengthy latencies, excessive energy, and finite patience can be correctly mitigated. Effective buffer agencies and partial writes make PCM aggressive with DRAM at modern generation nodes. Moreover, these complexity powerful solutions are location impartial, an important constraint in reminiscence production.

Mobile devices are critically limited in reminiscence, which influences critical person-enjoy metrics which include software service time. Emerging non-risky reminiscence (NVM) technology such as STT-RAM and PCM are ideal applicants to provide better memory capability with negligible power overhead. However, current reminiscence control systems neglect cell customer's utility utilization which gives crucial cues for improving person experience. In this paper, we suggest CAUSE, a singular memory machine based totally on DRAM-NVM hybrid reminiscence architecture. CAUSE takes express account of the application utilization styles to differentiate records criticality and become aware of suitable switch candidates. We additionally devise NVM hardware layout optimized for the get admission to characteristics of the swapped pages. We compare CAUSE on a actual android smartphone and NVSIM simulator the usage of person application utilization logs. Our experimental effects display that the proposed technique achieves 32% faster launch time for cell applications even as reducing electricity fee with the aid of 90% and forty four% on average over non-optimized STT-RAM and PCM, respectively. In this paper, we proposed singular memory systems for smart devices, known as CAUSE, which leverages NVMs for the swap capability. By thinking about utility usage sample of users, CAUSE intelligently manages page migration between major reminiscence and switch reminiscence, to be able to provide better user enjoy with respect to utility release time. In addition, the CAUSE device carefully optimizes NVM hardware to contain distinctive requirements of migrated pages. We evaluated the CAUSE

(A High Impact Factor & UGC Approved Journal)

Website: <u>www.ijirset.com</u>

#### Vol. 6, Issue 9, September 2017

machine over extraordinary memory technologies using real person lines on a real Android smart phone device. The CAUSE approach can be prolonged and improved in diverse ways. From a software perspective, we accept as true with that accurate application launching prediction strategies primarily based on the consumer context can help to make higher decisions about which pages are migrated.

### **III. FRAME WORK**

By making use of the byte-addressability of PCM, the proposed approach can control blocks with a couple of granularities to lessen the internal fragmentation of blocks that shop small documents or the tail statistics of files; in different words, smaller blocks are used for smaller files and larger blocks are allocated for large documents. Note that PCM is normally designed to be written in a cache line length, e.g., sixty four bytes, due to the fact processors normally include internal/on-chip (SRAM) cache and get right of entry to byte-addressable off-chip DRAM or PCM within the unit of a cache line length as a batch; despite the fact that byte updates to PCM are possible, they will be an awful lot much less green than being up to date inside the cache line length. Thus, on these paintings, the taken into consideration block sizes of record systems are multiples of the cache line length of PCM. In addition, the proposed strategy dynamically allocates space for inodes with the aid of inode indirection to reclaim space of inodes efficiently, such that the gap of inodes (or inode tables) and records blocks can be interchanged adaptively to remedy the outside fragmentation caused by unused inodes or data blocks.

### 3.1 Phase Change Memory (PCM)

Phase change reminiscence may be exploited via the memory system and by means of the convergence of purchaser, computer and conversation digital structures. The caching of the existing reminiscence technology, decreasing the general device charge and device complexity might be the compelling motivation for PCM adoption. Bandwidths will energy the sustaining facet of PCM in code and data switch packages and at the same time as reduction in power dissipation will represent a similarly added price of this technology. PCM is today's reminiscence leap forward. Like flash, PCM is a nonvolatile memory that would hold bits even without nergy supply.

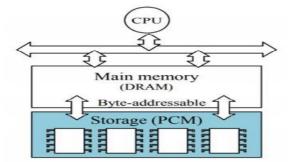

Fig1. Architecture for PCM based Storage system

But now not like flash, data may be written to cells a superb deal quicker, at costs corresponding to the dynamic and static random-get entry to memory (DRAM and SRAM) utilized in all laptop systems and cellular phones in recent times. Quite truly, PCM blends together the terrific attributes of NOR flash, NAND flash, EEpROM and RAM turning in a new class of reminiscence for emblem spanking new utilization fashions.

### 3.2 Space Utilization

In a report machine, we can also have some of small and huge documents as well as metadata that need to be stored. The space usage performance could be very critical especially for SCM devices considering their steeply-priced price. We need to utilize high-quality pages for storing data which might also probably reduce the pressure on TLB and improve file device performance. However, allocating the complete record gadget statistics with splendid web page will generate lots of internal fragmentation, especially for small files and metadata. In this kind of case, we may have low area usage efficiency on the SCM device.

(A High Impact Factor & UGC Approved Journal)

Website: <u>www.ijirset.com</u> Vol. 6, Issue 9, September 2017

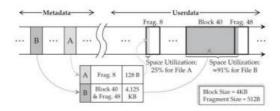

Fig2. Storage system for UNIX File System

The space usage of inode-based document structures is strongly stimulated by using the range of used blocks and block sizes to keep documents. An inode based report machine allocates information blocks for user information and indirect blocks for oblique hints to keep document contents. When a file length is massive enough, inode-primarily based document structures allocate oblique blocks to save the indirect suggestions that (1) point to different indirect blocks or (2) point to the (facts) blocks that shop the content of the report. Hence, in inode-primarily based file systems, the allocated garage space salloc for a record is depending on the variety of allotted/used data blocks and the range of allotted/used oblique blocks which include single, double, and triple indirect blocks.

### **IV. EXPERIMENTAL RESULTS**

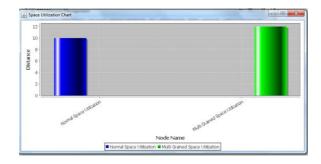

The purpose of this section is to evaluate the capability of the proposed multi-grained block management strategy, in terms of space utilization, access performance and energy consumption. After uploading dataset we can run the normal fragmentation. In normal fragmentation, it left the free block space. Hence, we can say normal fragmentation provide resource wastage.

In PCM fragmentation, it will verify the previous block if any free. By doing this, we can avoid the resource wastage problem.

Space utilization chart as shown below in both normal space utilization and multigrained space utilization

(A High Impact Factor & UGC Approved Journal) Website: <u>www.ijirset.com</u> Vol. 6, Issue 9, September 2017

#### V. CONCLUSION

In this paper we proposed multi-grained block control approach to optimize the distance usage of record systems over PCM-based totally storage systems. By using this proposed method, we can reduce the space usage inside the file machine. The proposed multigrained block management strategy is allocating the proper block sizes in PCM to decrease the inner fragmentation difficulty.

#### REFRENCES

[1] Y.-H. Chang, T.-Y.Chen, Y.-J.Chen, H.-W.Wei, W.-K.Shih, and Z.-R. Lai, "Optimizing space utilization of file systems on PCMbased storage devices," in Proc. IEEE Nonvolatile Memory Syst. Appl. Symp., 2014, pp. 1–6.

[2] B. C. Lee, E. Ipek, O. Mutlu, and D. Burger, "Architecting phase change memory as a scalable DRAM alternative," in Proc. IEEE/ ACM 36th Annu. Int. Symp. Comput. Archit., 2009, pp. 2–13.

[3] M. K. Qureshi, V. Srinivasan, and J. A. Rivers, "Scalable high performance main memory system using phase-change memory technology," in Proc. 36th Annu. Int. Symp. Comput. Archit., 2009, pp. 24–33.

[4] L. E. Ramos, E. Gorbatov, and R. Bianchini, "Page placement in hybrid memory systems," in Proc. Int. Conf. Supercomput., 2011, pp. 85-95.

[5] M. K. Qureshi, M. Franceschini, A. Jagmohan, and L. Lastras, "PreSET: Improving read write performance of phase change memories by exploiting asymmetry in write times," in Proc. 39th IEEE/ ACM Annu. Int. Symp. Comput. Archit., 2012, pp. 380–391.

[6] J. Yue and Y. Zhu, "Accelerating write by exploiting PCM asymmetries," in Proc. IEEE 19th Int. Symp. High Perform. Comput. Archit., 2013, pp. 282–293.

[7] J. Yue and Y. Zhu, "Exploiting subarrays inside a bank to improve phase change memory performance," in Proc. Des., Autom. Test Eur. Conf. Exhib., 2013, pp. 386–391.

[8] S. Cho and H. Lee, "Flip-n-write: A simple deterministic technique to improve pram write performance, energy and endurance," in Proc. 42nd Ann. IEEE/ACM Int. Symp. Microarchit, 2009, pp. 347–357.

[9] J. Hu, C. Xue, W.-C. Tseng, Y. He, M. Qiu, and E.-M.Sha, "Reducing write activities on non-volatile memories in embedded cmps via data migration and recomputation," in Proc. 47th ACM/ IEEE Des.Autom. Conf., 2010, pp. 350–355.

[10] Y. Park and K. H. Park, "High-performance scalable flash file system using virtual metadata storage with phase-change RAM," IEEE Trans. Comput., vol. 60, no. 3, pp. 321–334, Mar. 2011.