(A High Impact Factor, Monthly, Peer Reviewed Journal) Visit: <u>www.ijirset.com</u> Vol. 7, Issue 6, June 2018

# VLSI Architecture for Complex Vedic Multiplier using Hybrid Square Kogge Stone Adder Technique

Vivek Gupta, Prof. Vaibhav Jindal

M. Tech. Scholar, Department of Electronics and Communication, SISTech. Gandhinagar, Bhopal, India Assistant Professor, Department of Electronics and Communication, SISTech. Gandhinagar, Bhopal, India

**ABSTRACT**: The main objective of this research paper is to design architecture for complex Vedic multiplier by rectifying the problems in the existing method and to improve the speed by using the kogge stone adder with the help of hybrid square technique. The Vedicmultiplier algorithm is normally used for higher bit length applications and ordinarymultiplier is good for lower order bits. These two methods are combined to produce the high speed multiplier for higher bit length applications. The problem of existing architecture is reduced by removing bits from the remainders. The proposed algorithm is implementation Xilinx software with Vertex-7 device family.

KEYWORDS: Vedic Multiplier, Complex Multiplier, Hybrid Square Kogge Stone Adder, Xilinx Software

### I. INTRODUCTION

Arithmetic is the oldest and most elementary branch of Mathematics. The name Arithmetic is derived from the Greek word "arithmos". Arithmetic is used by almost everyone, for tasks ranging from simple day to day work. As a result, the need for a faster and efficient Arithmetic unit in computers is the interesting topic over decades. The four basic operations in elementary arithmetic are addition, subtraction, multiplication and division. Multiplication is the basic mathematical operation of scaling one number by another. Multiplication is used in today's engineering field covering many Digital Signal Processing (DSP) applications such as convolution, Fast Fourier Transform (FFT), filtering and in Arithmetic Logic units of a microprocessor, microcontroller and most of the Embedded controllers. The demand for high speed processing has been increasing as a result of expanding computer and signal processing applications. Higher throughput arithmetic operations are essential to achieve the desired performance in many real-time signal and image processing applications. One of the key arithmetic operations in such applications is multiplication and the development of faster multiplier circuit has been a subject of interest over decades. Reducing the time delay and power consumption are very essential requirements for many applications.

Parallel multiplication is used to meet out the current requirement. Two types of parallel multiplications are array multiplication and tree multiplication. The basic multiplier is a simple array multiplier and it is designed based on shiftand – add operation. One of the examples for array multiplication is the Braun multiplier and is designed for unsigned binary numbers. For tree structure Wallace multiplier is designed and it is also for an unsigned binary numbers. In the array multiplication, for signed numbers Baugh – Wooley, Booth Multiplier and Modified Booth Algorithm (MBA) are used. Dadda is another type of multiplier based on tree structure and is used for the multiplication of the signed numbers. These conventional binary multipliers for unsigned numbers are considered for comparison. Vedic mathematics is the system of mathematics followed in ancient India and mainly deals with Vedic mathematical formulae and their applications to various branches of mathematics. The word 'Vedic' is derived from the word 'Veda' which means the storehouse of all knowledge.

Vedic mathematics was reconstructed from the ancient Indian scriptures (Vedas) by Sri Bharati Krishna Tirthaji (1884-1960), after his eight years of research on Vedas. According to his research, Vedic mathematics is mainly based on sixteen principles or word-formulae and thirteen sub-corollaries which are termed as Sutras. This is a very interesting

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

### Vol. 7, Issue 6, June 2018

field and presents some effective algorithms which can be applied to various branches of Engineering such as Computing and Digital Signal Processing. Vedic mathematics reduces the complexity in calculations that exist in conventional mathematics. Generally there are sixteen sutras available in Vedic mathematics.

Among them only two sutras are applicable for multiplication operation. They are UrdhavaTriyakbhyam sutra (literally means vertically and crosswise) and Nikhilam Sutra (literally means All from 9 and last from 10). Urdhava-Triyakbhyam is a generic method for multiplication. The logic behind UrdhavaTriyakbhyam sutra is very much similar to the ordinary array multiplier. Here the binary implementation of this algorithm is derived based on the same logic used for decimal numbers. The binary implementation of Nikhilam Sutra is not yet successful.

This is a special case in multiplication. Another algorithm used to simplify the multiplication process is Karatsuba algorithm. This Karatsuba algorithm uses a divide-and-conquer approach where it breaks down the inputs into Most Significant half and Least Significant half and this process continue until the operands are of 8-bits wide. Karatsuba algorithm is best suited for operands of higher bit length. But at lower bit lengths, it is not as efficient as it is at higher bit lengths. This method was discovered by Anatoli Karatsuba in 1962. It reduces the number of multipliers required, by replacing the multiplication operations by addition operations. Addition operations are faster than multiplications and hence the speed of the multiplier is increased. As the amount of bits increase, the efficiency of the multiplier will also increase.

In this research paper, a novel architecture of complex multiplier is designed using hybrid square kogge stone adder.

#### II. TYPES OF MULTIPLIER

Multipliers play an important role in today's digital signal processing and various other applications. Essential design targets of multiplier include high speed, low power consumption, regularity of layout and hence less area or even combination of them in one multiplier are required thereby making them suitable for various VLSI implementations. Most multiplication techniques can be classified as Array multipliers and Tree multipliers. A detailed discussion on the different types of multipliers is done in the following sections.

#### (i) Array Multipliers

Array multipliers can be implemented by directly mapping the manual multiplication into hardware. The partial products are accumulated by an array of adder circuits. An n x n array multiplier requires n (n-1) adders and  $n^2$  AND gates.

### (ii) Carry Save Array Multiplier

The carry-save array multiplier uses an array of carry-save adders for the accumulation of partial product. It uses a carry-propagate adder for the generation of the final product. This reduces the critical path delay of the multiplier since the carry-save adders pass the carry to the next level of adders rather than the adjacent ones.

#### (iii) Wallace Tree Multiplier

C. S. Wallace (1964) propounded a fast technique to perform multiplication. A Wallace tree multiplier offers faster performance for large operands. Unlike an array multiplier the partial product matrix for a treemultiplier is rearranged in a tree-like format, reducing both the critical path and the number of adder cells needed.

#### (iv) Dadda Multiplier

Dadda multiplier is a hardware multiplier designed similar to Wallace multiplier. Unlike Wallace multipliers that perform reductions as much as possible on each layer, Dadda multipliers do as few reductions as possible. Due to this, Dadda multipliers have less expensive reduction phase, but the numbers may be a few bit longer, thus requiring slightly bigger adders. This implies that fewer columns are compressed in the initial stages of the column compression tree, and more columns in the later levels of the multiplier.

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

### Vol. 7, Issue 6, June 2018

#### (v) Booth Wallace Tree Multipliers

The use of Booth's algorithm, in multiplication presents an efficient solution that suits the demands of high-speed multipliers, which also need to be efficient in terms of hardware design/area complexity.

In this multiplier, the partial products are generated using the Booth method, while their summation is done using Wallace tree structure. This compresses the addition process. The adder is used in adder accumulator configuration, where the multiplication result is added every time to the partial product register.

| Table 1: Comparison of Multiplier |             |            |      |       |  |

|-----------------------------------|-------------|------------|------|-------|--|

| Types of                          | Delay/      | Structure/ | Area | Speed |  |

| Multiplier                        | Increase in | Complexity |      |       |  |

|                                   | bit size    |            |      |       |  |

| Array                             | Linear      | Regular/   | High | Low   |  |

|                                   |             | Low        |      |       |  |

| Wallace                           | Logarithmic | Irregular/ | High | High  |  |

|                                   |             | High       |      |       |  |

| Dadda                             | Logarithmic | Irregular/ | High | High  |  |

| Tree                              |             | High       |      |       |  |

| Booth                             | Non-linear  | Regular/   | Low  | Mediu |  |

|                                   |             | Medium     |      | m     |  |

#### **III. VEDIC MULTIPLIER**

Vedic multiplier and hybrid square KoggeStone adder can compare with conventional method which is computed by Vedic multiplier, full adder and half adder. Proposed technique provides less path delay and less area. Input sequence of Conventional method is much more than to proposed method, however proposed method has less propagation delay. Area and propagation delay can be reduced by the aid of hybrid square Kogge Stone adder. This adder will be designed like as ripple carry adder.

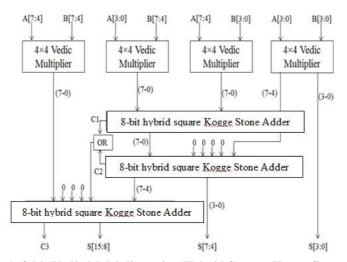

Logic Diagram of Vedic Multiplier using Kogge Stone Adderis shown in figure 1. Eventually, all the designing levels of digital system or IC's Packages depend on number of gates in a single chip that is also called bottom up approach. Modified KS adder can be reduced regarding the area or number of gates. If we remove the first XOR gate from modified KS adder nothing will be changed for result but area and propagation delay will be reduced.

Figure 1: 8-bit Vedic Multiplier using Hybrid Square Kogge Stone Adder

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

### Vol. 7, Issue 6, June 2018

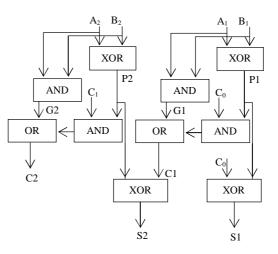

#### (i) Hybrid Square Kogge Stone Adder

The complete functioning of KSA can be easily comprehended by analyzing it in terms of three distinct parts:

(a) Preprocessing: - This step involves computation of generate and propagate signals corresponding too each pair of bits in A and B. These signals are given by the logic equations below:

| $P_i = A_i xor B_i$ | (1) |

|---------------------|-----|

| $G_i = A_i and B_i$ | (2) |

(b) Carry look ahead network: - This block differentiates KSA from other adders and is the main force behind its high performance. This step involves computation of carries corresponding to each bit.

$$C_i = G_i \, or \left( P_i \, and \, C_{i-1} \right) \tag{3}$$

(c) Post processing: - This is the final step and is common to all adders of this family (carry look ahead). It involves computation of sum bits. Sum bits are computed by the logic given below:

$$S_i = P_i xor C_{i-1} \tag{4}$$

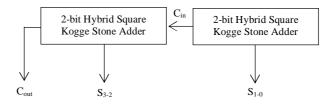

Figure 2: 2-bit Hybrid Square Kogge Stone Adder

Figure 3: 4-bit Hybrid Square Kogge Stone Adder

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u> Vol. 7, Issue 6, June 2018

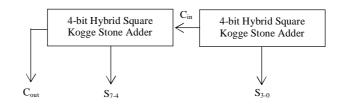

Figure 4: 8-bit Hybrid Square Kogge Stone Adder

### **IV. COMPLEX MULTIPLIER**

Suppose two numbers are complex then

$$A = A_r + jA_i$$

$$B = B_r + jB_i$$

The product of A and B then

$$P = A \times B$$

$$P = A_r \times B_r - A_i \times B_i + j(A_r \times B_i + A_i \times B_r)$$

$$P_r = A_r \times B_r - A_i \times B_i$$

$P_i = A_r \times B_i + A_i \times B_r$

Where

$$P_r$$

and  $P_i$  is represents the real and imaginary part of the output of the complex multiplier.  $A_r$  and  $A_i$  is represents the real and imaginary part of the first input of the complex multiplier.  $B_r$  and  $B_i$  is represents the real and imaginary part of the second input of the complex multiplier.

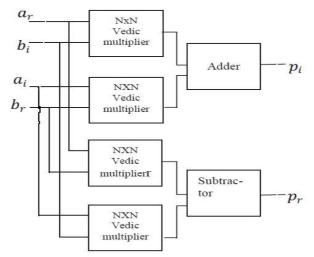

Figure 5: Block Diagram of Complex Multiplier for four Vedic Multiplier

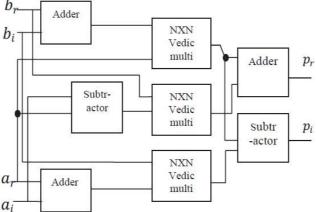

Complex multiplier for four Vedic multipliers is shown in figure 5. In this block diagram reduce four Vedic multipliers to three Vedic multipliers is shown in below:

(A High Impact Factor, Monthly, Peer Reviewed Journal) Visit: <u>www.ijirset.com</u>

Vol. 7, Issue 6, June 2018

$$P_r = A_r \times B_r - A_i \times B_i = A_r (B_r + B_i) - B_i (A_r + A_i)$$

$$P_i = A_r \times B_i + A_i \times B_r = A_r(B_r + B_i) + B_r(A_i - A_r)$$

### V. SIMULATION ANALYSIS

Simulation of these experiments can be done by using Xilinx 14.2 i VHDL tool. In this paper we are focusing on propagation delay. Propagation delay must be less for better performance of digital circuit.

As shown in table II the number of LUTs, delays are obtained for the complex Vedic multiplier using hybrid square kogge stone adder and previous algorithm. From the analysis of the results, it is found that the complex Vedic multiplier using hybrid square kogge stone adder gives a superior performance as compared with previous algorithm for Vertex-7 device family. The output waveform of the 32-bit complex multiplier using hybrid square KoggeStone adder is shown in figure 7 and figure 8 respectively.

| Name         | Value   | 0 ns       | 200 ns                                  | 400 ns                                  | 600 ns                                  |

|--------------|---------|------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| 🕨 🥳 ar[31:0] | 0000000 | 000000000  |                                         | 000000000000000000000000000000000000000 | 00001100                                |

| ▶ 🏹 ai[31:0] | 0000000 | 000000000X |                                         | 000000000000000000000000000000000000000 | 00000101                                |

| ▶ 🏹 br[31:0] | 0000000 | 000000000X |                                         | 000000000000000000000000000000000000000 | 00000010                                |

| 🕨 🏹 bi(31:0) | 0000000 | 000000000X |                                         | 000000000000000000000000000000000000000 | 00000100                                |

| ▶ 📑 pi[63:0] | 0000000 | 000000000X | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |

| ▶ 😽 pr[63:0] | 0000000 | 000000000X | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |

Figure 7: Output Binary Waveformof 32-bit Complex Multiplier using HS-KSA

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

Vol. 7, Issue 6, June 2018

| Name         | Value | 0 ns | 200 ns | 400 ns |

|--------------|-------|------|--------|--------|

| 🕨 😽 ar[31:0] | 12    |      |        | 12     |

| 🕨 😽 ai[31:0] | 5     | ○ X  |        | 5      |

| 🕨 😽 br[31:0] | 2     | ○ X  |        | 2      |

| 🕨 📑 bi[31:0] | 4     |      |        | 4      |

| 🕨 😽 pi[63:0] | 58    |      |        | 58     |

| 🕨 😽 pr[63:0] | 4     |      |        | 4      |

Figure 8: Output Decimal Waveformof 32-bit Complex Multiplier using HS-KSA

| Table II: Comparison Result for 32     | 2-bit Complex Vedic           | Multiplier for four                   | Vedic Multiplier                      |

|----------------------------------------|-------------------------------|---------------------------------------|---------------------------------------|

| ···· · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |

| Design                       | Number  | Number  | Delay     |

|------------------------------|---------|---------|-----------|

|                              | of LUTs | of IOBs |           |

| Complex Vedic Multiplier [2] | 10416   | 256     | 25.979 ns |

| Complex Vedic Multiplier     | 10642   | 256     | 26.927 ns |

| using Ripple Carry Adder     |         |         |           |

| Complex Vedic Multiplier     | 10222   | 256     | 25.204 ns |

| using Hybrid Square Kogge    |         |         |           |

| Stone Adder                  |         |         |           |

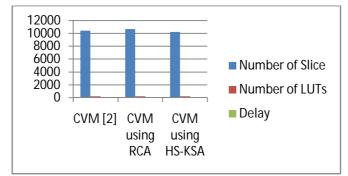

Figure 9: Bar graph of the 32-bit Complex Vedic multiplier

Figure10 shows the graphical illustration of the performance of CVM using KSA algorithm discussed in this research work in term of number of slice, number of LUTs and delay. From the above graphical representation it can be inferred that the CVM using KSA algorithm gives the best performance as compared with previous algorithm.

### VI. CONCLUSION

In this paper design of hybrid square Kogge Stone adder, Vedic multiplier and complex Vedic multiplier is presented. From implementation results it is observed that the hybrid based Vedic Multiplier and complex Vedic multiplier consumes less delay compare to previous design.

### REFRENCES

K. Deergha Rao, Ch. Gangadhar and Praveen K Korrai, "FPGA Implementation of Complex Multiplier Using Minimum Delay Vedic Real Multiplier Architecture", 2016 IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering (UPCON), IEEE 2016.

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: www.ijirset.com

#### Vol. 7, Issue 6, June 2018

- [2] Soma BhanuTej, "Vedic Algorithms to develop green chips for future", International Journal of Systems, Algorithms & Applications, Volume 2, Issue ICAEM12, February 2012, ISSN Online: 2277-2677.

- [3] Youngjoon Kim and Lee-Sup Kim, "A low power carry select adder with reduced area", IEEE International Symposium on Circuits and Systems, vol.4, pp.218-221, May 2001.

- [4] Y. Choi, "Parallel Prefix Adder Design," Proc. 17th IEEE Symposium on Computer Arithmetic, pp 90-98, 27th June 2005.

- [5] Kogge P and Stone H (1973), "A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Relations", IEEE Transactions on Computers, Vol. C-22, No. 8, pp. 786-793.

- [6] Madhu Thakur and Javed Ashraf (2012), "Design of Braun Multiplier with Kogge-Stone Adder & It's Implementation on FPGA", International Journal of Scientific & Engineering Research, Vol. 3, No. 10, pp. 03-06, ISSN 2229-5518.

- [7] PakkiraiahChakali and Madhu Kumar Patnala (2013), "Design of High Speed Kogge-Stone Based Carry Select Adder", International Journal of Emerging Science and Engineering (IJESE), Vol. 1, No. 4, ISSN: 2319-6378.

- [8] SomayehBabazadeh and Majid Haghparast, "Design of a Nanometric Fault Tolerant Reversible Multiplier Circuit" Journal of Basic and Applied Scientific Research, 2012.