# International Journal of Innovative Research in Science, Engineering and Technology

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

Vol. 8, Issue 2, February 2019

# Design of Memory Circuits Using Reversible Logic

P.Sangeetha, M.Santhosh, A.Suji,

Dept. of ECE, Builders Engineering College, Tirupur, Tamilnadu, India

**ABSTRACT:** With the advancement of nanotechonology, transistors are getting smaller and growing in number according to Moore's Law. Hence issues of heat dissipation is becoming a greater concern to researchers as the transistor heat dissipation reaches the Landauer limit. Reversible logic is predicted to be an alternative to conventional computing due to lesser energy dissipation. The main factor to apply reversible logic in VLSI circuit is low heat dissipation and low power consumption. Reversible logic will operate in backward direction. This ability allows us to reproduce the inputs from the outputs of the system. In this design RAM memory is proposed using reversible logic in LT-SPICE software. The objective is to reduce area and power consumption in RAM memory. The power relation table shows that reversible logic consumes less power when compared to CMOS logic. By using reversible logic, the transistor count also gets reduced.

KEYWORDS: RAM memory, Reversible logic gates, less power consumption, Fredkin gate, Toffoli gate.

### I. INTRODUCTION

In the past decade, reversible logic has become popularity among researchers in the VLSI domain. Power dissipation is one of the most important criteria in VLSI design. It plays a vital role in numerous technologies such as quantum computing, nanotechnology, optical information processing, low power CMOS design, DNA computing and bioinformatics. Energy dissipation is one of the major issues in present day technology and is due to the information loss in high technology circuits. Whenever there is information loss, KT\*ln2 joules of energy is dissipated for every bit and this was asserted by R. Landauer in 1960, where T is absolute temperature and K is Boltzmann's constant. Since there is no information loss in reversible logic, the amount of power dissipated is considerably less when compared to conventional logic.

A circuit is said to be reversible if the input vector can be uniquely recovered from the output vector and there is a one-one correspondence between its input and output assignments, i.e. not only the outputs can be uniquely determined from the inputs, but also the inputs can be recovered from the outputs. Energy dissipation can be reduced or even eliminated if computation becomes information-lossless.

Reversibility in computing implies that no information about the computational states can ever be lost, so we can recover any earlier stage by computing backwards or un-computing the results. This is termed as logical reversibility. The benefits of logical reversibility can be gained only after employing physical reversibility. Physical reversibility is a process that dissipates no energy to heat. Absolutely perfect physical reversibility is practically unachievable. Computing systems give off heat when voltage levels change from positive bits from zero to one. Most of the energy needed to make that change is given off in the form of heat. Rather than changing voltages to new levels, reversible circuit elements will gradually move charge from one node to the next node.

## International Journal of Innovative Research in Science, Engineering and Technology

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

#### Vol. 8, Issue 2, February 2019

### **II. CMOS LOGIC**

Complementary Metal-Oxide Semiconductor is a technology for constructing integrating circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM and other digital logic circuits. Two important characteristics of CMOS device are high noise immunity and low static power consumption. For the design of any circuit using CMOS technique, the more number of transistors are needed for the circuit design. Due to the usage of more transistors, the power consumption also becomes high.

#### **III. REVERSIBLE LOGIC**

High performance chips releasing large amounts of heat. Reversible computing will also leads to improvement in energy efficiency. Energy efficiency will fundamentally affect the speed of circuits such as nano circuits and therefore the speed of most computing applications. To increase the portability of devices again reversible computing is required. It will let circuit elements sizes to reduce to atomic size limits and hence devices will become more portable. Reversible logic circuits have minimum quantum cost. It requires less number of transistors. Comparing with CMOS technique, the reversible logic technique consumes less power and less transistors needed for the design process.

#### **IV. MEMORY CELL**

The Memory cell is the fundamental building block of computer memory. The memory cell is an electronic circuit that stores one bit of information and it must be set to store a logic '1' and reset to store a logic '0'. The value in the memory cell can be accessed by reading it.

#### V. RAM MEMORY-CMOS LOGIC

A memory unit is a collection of storage cells together with associated circuits needed to transform information in and out of the device. Memory cells can be accessed for information transfer to or from any desired random location is called RAM. The internal construction of a RAM of m words with n bits per word consists of m\*n binary storage cells and associated decoding circuits for selecting individual words. A basic Random Access Memory cell has been provided here as a component which can be used to design larger memory units. An IC memory consisting of 4 words each having 3 bits has been also provided. In this project, 3\*3 RAM are designed using both CMOS logic and reversible logic.

# International Journal of Innovative Research in Science, Engineering and Technology

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

Vol. 8, Issue 2, February 2019

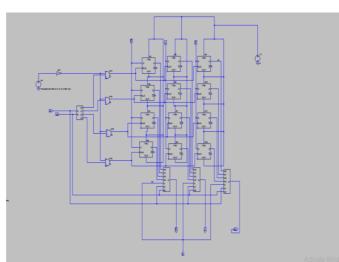

The above diagram shows that 3\*3 RAM memory designed using CMOS logic. The inputs are v(d0), v(d1), v(d2). The inverter is an electronic device or circuitry that changes direct current(DC) to alternating current (AC).

Copyright to IJIRSET

# International Journal of Innovative Research in Science, Engineering and Technology

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

### Vol. 8, Issue 2, February 2019

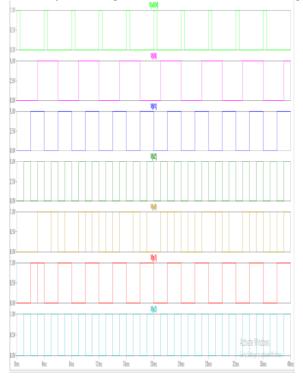

The first waveform shows the clock pulse. It stores the inputs state and output state only in response to clock signal. The input waveforms are v(d0), v(d1), v(d2). The same date can be retained at the output as named as v(q0), v(q2), v(q3). The RAM memory is designed using flip flop. Flip flop is an one bit storage device. The transistor count for RAM memory using CMOS logic is about 207.

#### VI. RAM MEMORY- REVERSIBLE LOGIC

Reversible circuit connects reversible gates without fanouts and loops. The reversible logic can't erase information and dissipates zero heat. There are many reversible logic gates such as Feynman gate, Fredkin gate, Toffoli gate, UPG gate, BVPPG gate, peres gate etc..which are used to design low power circuits. The D-flip flop can be replaced using Fredkin gate.

#### A. FREDKIN GATE:

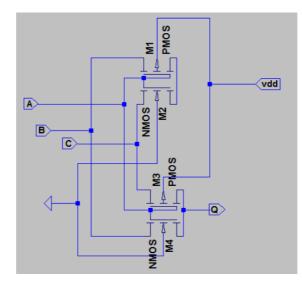

Fredkin gate is the 3\*3 reversible gate with three inputs and three outputs. The inputs (A, B, C) mapped to outputs (P, Q, R). It implements the function: P=A, Q=A'B XOR AC and R=A'C XOR AB.

The above diagram shows the Fredkin gate, which is one of the reversible logic gates. It is the equivalent gate for D-flip flop. The existing method contains more transistors because of the usage of CMOS logic whereas in case of using reversible logic the transistor count can be reduced.

# International Journal of Innovative Research in Science, Engineering and Technology

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

Vol. 8, Issue 2, February 2019

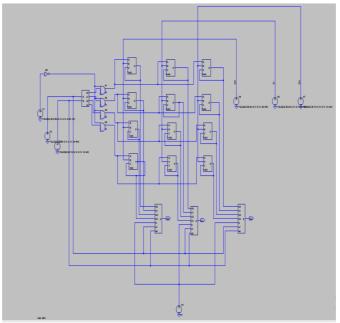

The above diagram shows that the RAM memory is designed using reversible logic. By using this technique, the D-flip flop can be replaced by fredkin gate.

Copyright to IJIRSET

# International Journal of Innovative Research in Science, Engineering and Technology

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

### Vol. 8, Issue 2, February 2019

The first, second and third waveform shows that the inputs to the RAM memory and it is named as v(d0), v(d1), v(d2) and the output are named as v(q0), v(q1) and v(q2). These waveform shows that the data stored in memory can be retained without loss of information.

#### **VII.POWER RELATION TABLE**

The power relation table shows that by using reversible logic the power consumption and the transistor count can be reduced when compared to CMOS logic.

|         | Transistor Count |                     | Power Consumption |                     |

|---------|------------------|---------------------|-------------------|---------------------|

|         | CMOS<br>logic    | Reversible<br>logic | CMOS<br>logic     | Reversible<br>Logic |

| 3*3 RAM | 207              | 134                 | 7.883E-<br>08     | 5.0047E-06          |

### **VIII. CONCLUSION**

In this paper, RAM memory is designed using CMOS logic, the circuit consumes more power and also transistor count becomes high. In case of using reversible logic, the transistor count can be reduced automatically the power consumption also reduced.

### IX. ACKNOWLEDGEMENT

Mr. A.S.Prabhu, Assistant Professor, Department of ECE, Builders Engineering College, Tirupur.

#### REFERENCES

- 1. S.M.R Taha, Reversible Logic Synthesis Methodologies with Application to Quantum Computing, Studies in Systems, Decision and Control 37, DOI 10.1007/978-3-319-23479-3\_2,2018

- M. Perkowski, P. Kerntopf, A. Buller, M. Chrzanowska-Jeske, A. Mishchenko, X. Song, A. Al-Rabadi, L. Jozwiak, A. Coppola and B. Massey, Regular realization of symmetric functions using reversible logic, in Proceedings of EUROMICRO Symposium on Digital Systems Design (Euro-Micro'01), Warsaw, Poland, pp. 245–252, September 2015

- D. Maslov, G.W. Dueck, Garbage in reversible designs of multiple output functions, in Proceedings of the 6th International Symposium on Representations and Methodology of Future Computing Technologies (RM 2003), Trier, Germany, pp. 162–170, March 2013

Matthew Morrison, Matthew Lewandowski, Richard Means in proceedings of 11<sup>th</sup> International conference on Nanotechnology, portland, Oregon, USA(august 15-18,

- Matthew Morrison, Matthew Lewandowski, Richard Means in proceedings of 11<sup>th</sup> International conference on Nanotechnology, portland, Oregon, USA(august 15-18, 2011)

- Shefali Mamataj, Dibiya Saha, Nahida Banu, A review on reversible gates and its applications in logic design in the american journal of Engineering research, Poland, august 2014

Copyright to IJIRSET