(A High Impact Factor, Monthly, Peer Reviewed Journal) Visit: <u>www.ijirset.com</u>

Vol. 8, Issue 6, June 2019

# **Power Efficient Radix-2 DIT FFT using Folding Technique and DKG Reversible Gate**

Jainendra Dwivedi<sup>1</sup>, Prof. Anshuj Jain<sup>2</sup>

M. Tech. Scholar, Department of Electronics and Communication, Scope College of Engineering, Bhopal, India<sup>1</sup>

Assistant Professor, Department of Electronics and Communication, Scope College of Engineering, Bhopal, India<sup>2</sup>

**ABSTRACT:** FFT is normally utilized in computerized flag preparing algorithms. 4G correspondence and different remote framework based correspondence are directly hotly debated issues of innovative work in the remote correspondence and organizing field. FFT is a calculation that speeds up the count of DFT. In the main stage, low multifaceted nature Radix-2 Multi-way Delay Commutator (R2MDC) FFT recurrence change method is created through Exceptionally Large Scale Integration System structure condition. Low power utilization, less zone and rapid are the VLSI primary parameters. Customary R2MDC FFT structure has more equipment multifaceted nature because of its escalated computational components. Two strategies are utilized to plan radix-2 FFT calculation. In firest strategy is plan radix-2 FFT with the help of reversible Peres gate and TR gate. Second method is design radix-2 FFT with the help of reversible DKG Gate. The all structure are usage vertex-4 device family Xilinx programming and looked at past calculation.

KEYWORDS: Reversible Gates, Adder/ Sub tractor, Fast Fourier Transform, DKG Gate, Peres Gate, TR Gate

### I. INTRODUCTION

The Fourier Transform is an inevitable approach in signal processing [1], the Discrete Fourier Transform decomposes a set of values into different components of frequency. The Fast Fourier transform (FFT) is an appropriate technique to do manipulation of DFT. The algorithm of FFT was devised by Cooley and Tukey in order to decrease the amount of complexity with respect to time and computations [2].

The hardware of FFT can be implemented by two types of classifications- memory architecture and pipeline architecture. The memory architecture comprises a single processing element and various units of memory [3]. The merits of memory architecture include low power and low cost when compared to that of other styles. The specific demerits are greater latency and lower throughput. The above demerits of the memory architecture are totally eliminated by pipeline architecture at the expense of extra hardware in an acceptable way. The various types of pipeline architecture include Single delay feedback (SDF), Single delay commutator (SDC) and multiple delay commutators (MDC). The pipeline architecture is a regular structure which can be adopted by using hardware description language in an easy manner.

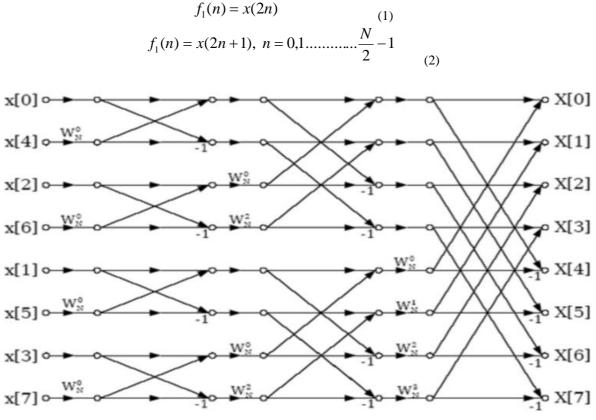

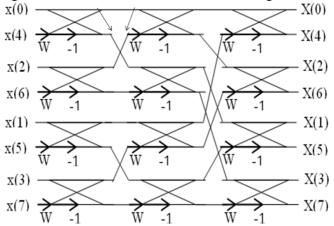

The algorithms of FFT can be grouped into fixed-radix, mixed-radix and split radix algorithms in a rough manner [5]. The basic categories of algorithms of FFT include - Decimation in-frequency (DIF) and the Decimation-in-time (DIT) as shown in Figure 1. Both of these algorithms depend on disintegration of transformation of an N-point sequence into many subsequences in a successive manner. There is no major difference between them as far as complexity of computation is concerned. Generally DIT deals with the input and output in reverse sequence and normal sequence respectively, while DIF deals with input and output in normal sequence and reverse sequence respectively. Only Decimation-in-Time (DIT) algorithm is taken into consideration. In this paper for implementation & result comparison, however DIT algorithm can also be use the proposed methodology.

The FFT is a run of the mill computation where the memory get to seriously and the high parallelism is required. FFT calculation ought to have pipelined design and parallel design, be ordinary and measured. At calculation level, it should come to the multiplicative multifaceted nature as low as practical. At the structural dimension, utilize the deferral –

(A High Impact Factor, Monthly, Peer Reviewed Journal)

## Visit: <u>www.ijirset.com</u>

#### Vol. 8, Issue 6, June 2019

criticism buffering methodology to lessen the memory measure. It ought to have measured and ordinary modules, neighborhood directing and low control intricacy [5]. FFT is used to change over time space flag to recurrence area flag. It is utilized to figure the DFT adequately. To meet the superior, high speed and ongoing prerequisites of present day applications, equipment fashioners have continuously attempted to perform proficient structures for the estimation of the FFT. The pipelined equipment models are generally utilized, in light of the fact that they give high throughputs and low latencies appropriate for continuous, just as a sensibly low region what's more, control utilization.

Hence it is not possible to determine a unique input that resulted in the output zero. In order to make a gate reversible additional input and output lines are added so that a one to one mapping exists between the input and output. This prevents the loss of information that is main cause of power dissipation in irreversible circuits. The input that is added to an m x n function to make it reversible is known as constant input (CI). All the outputs of a reversible circuit need not be used in the circuit. Those outputs that are not used in the circuit is called as garbage output (GO). The number of garbage output for a particular reversible gate is not fixed.

#### **II. FAST FOURIER TRANSFORM**

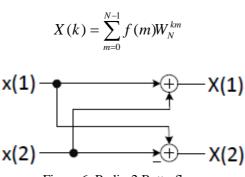

There are two sorts concerning FFT calculation formulated by Cooley and Tukey - Decimation-in-Time calculation (DIT) and Decimation-in-Frequency calculation (DIF). The calculation of an arrangement of N-point can be acquired by methods for a double methodology. The info succession x(n) of size 'N' is disintegrated into tests of odd and even and the comparing sub-groupings fl(n) and f2(n) are given by:

Figure 1: 8-point DIT-FFT Radix-2 Butterfly

(A High Impact Factor, Monthly, Peer Reviewed Journal) Visit: <u>www.ijirset.com</u>

## Vol. 8, Issue 6, June 2019

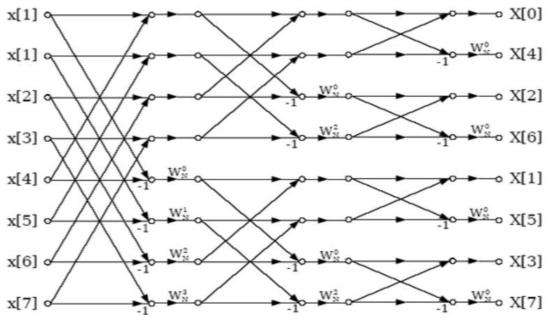

In represent figure 1, demonstrate the termite of radix-2 DIT FFT calculation. In this figure we utilized eight sources of info and eight yields. If there should be an occurrence of DIT the info test is utilized piece inversion arrange while the yield of DIT FFT coadjuvant is produced in normal request. In represent Figure 2, demonstrate the termite of radix-2 DIF-FFT calculation. In the event of DIF the information test is utilized in common request while the yield of DIF FFT coadjuvant is produced in bit turned around request.

Figure 2: 8-point DIF-FFT Radix-2 Butterfly

#### **III. REVERSIBLE GATES**

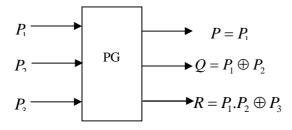

Several reversible logic gate (RLG) are utilized in past structure. Figure 3 demonstrates the Peres door (PG). A bit of the 3x3 entryways are planned for executing some basic combinational limits despite the basic limits.

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u> Vol. 8, Issue 6, June 2019

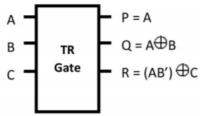

Figure 4: Block Diagram of TRG

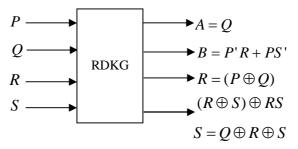

Figure 4, shows the TRG with  $3\times3$  system. TRG gate as working of half sub-tractor, when third input assume '0'. The RDKG is presented by figure 5. RDKG is  $4\times4$  system representation. RDKG is working on full adder and full sub-tractor when first input assume '0' and '1'.

#### **IV. PROPOSED METHODOLOGY**

DFT is a most important transform among the transforms that are widely used. The DFT is used to perform the Fourier transform efficiently. The FFT algorithm is the most efficient and most preferred algorithm that is used in DFT computation. The FFT algorithm is preferred the most for DFT computation because of the need of less arithmetic resources when compared to that of the conventional method of DFT computation.

Figure 6: Radix-2 Butterfly

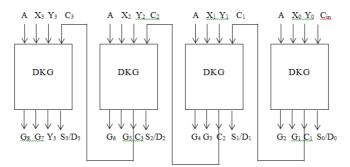

The expense and defer figurings are indistinguishable to the 4-bitb snake/sub tractor in figure 7. We have design 4-bit full sub-tractor/adder with the help of DKG Gate. If the fourth input of the DKG Gate is '0' then output of the DKG Gate as a adder and fourth input of the DKG Gate is '1' then output of the DKG Gate as a sub-tractor.

(A High Impact Factor, Monthly, Peer Reviewed Journal)

# Visit: <u>www.<mark>ijir</mark>set.com</u>

Vol. 8, Issue 6, June 2019

Figure 7: Reversible 4-bit Adder/ Sub tractor using DKG Gate

Figure 8: Flow Diagram of FFT using Folding Technique

#### V. SIMULATION RESULT

All the designing and experiment regarding algorithm that we have mentioned in this paper is being developed on Xilinx 6.2i updated version. Xilinx 6.2i has couple of the striking features such as low memory requirement, fast debugging, and low cost. The latest release of  $ISE^{TM}$  (Integrated Software Environment) design tool provides the low memory requirement approximate 27 percentage low. ISE 6.2i that provides advanced tools like smart compile technology with better usage of their computing hardware provides faster timing closure and higher quality of results for a better time to designing solution.

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

Vol. 8, Issue 6, June 2019

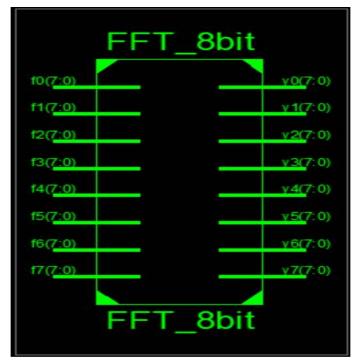

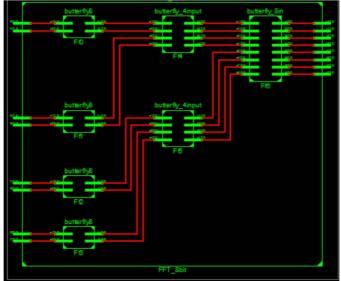

Figure 9: View Technology Schematicof 8-point DIT-FFT algorithm

Figure 10: RTL View of DIT 8-point DIT-FFT algorithm

(A High Impact Factor, Monthly, Peer Reviewed Journal)

#### Visit: <u>www.ijirset.com</u>

Vol. 8, Issue 6, June 2019

| Name                | Value    | 0 ns     | 200 ns | 400 ns   | 600 ns   |

|---------------------|----------|----------|--------|----------|----------|

| 🕨 📑 f0[7:0]         | 01000000 | 00000000 |        | 01000000 |          |

| 🕨 📑 f1[7:0]         | 00100000 | 00000000 |        | 00100000 |          |

| 🕨 📑 f2[7:0]         | 00010000 | 00000000 |        | 00010000 |          |

| 🕨 📑 f3[7:0]         | 00001000 | 00000000 |        | 00001000 |          |

| 🕨 📑 f4[7:0]         | 00000100 | 00000000 |        | 00000100 |          |

| 🕨 📑 f5[7:0]         | 00000010 | 00000000 |        | 00000010 |          |

| 🕨 📑 f6[7:0]         | 00000001 | 00000000 |        | 00000001 |          |

| 🕨 📑 f7[7:0]         | 0000000  |          |        | 00000000 |          |

| 🕨 📑 y0[7:0]         | 01111111 |          |        | 01111111 |          |

| 🕨 📑 y1[7:0]         | 01110000 |          |        | 01110000 |          |

| ▶ 📑 y2[7:0]         | 01001101 |          |        | 01001101 |          |

| ▶ 📑 y3[7:0]         | 01000011 |          |        | 01000011 |          |

| ▶ 📑 y4[7:0]         | 00101011 |          |        | 00101011 |          |

| ▶ 📑 y5[7:0]         | 00100101 |          |        | 00100101 |          |

| <b>y6</b> [7:0]     | 00011001 |          |        | 00011001 |          |

| ▶ <b>26 y7[7:0]</b> | 00010    | 111      |        |          | 00010111 |

Figure 11: OutputWaveform of DIT 8-point FFT using DKG Gate

#### **VI. CONCLUSION**

There are three types of reversible gate is used for radix-2 butterfly i.e. Peres gate, TR Gate and DKG Gate. Peres gate is used for addition of two numbers, TR gate is used for sub-tractor of two numbers and DKG gate is used for addition/ sub-tractor of two numbers. DKG gate is depend on first input i.e. the first input is '0' then DKG is working of addition otherwise sub-tractor.

#### REFERENCES

- [1] Shashidhara. K. S and H.C. Srinivasaiah, "Low Power and Area efficient FFT architecture through decomposition technique", International Conference on Computer Communication and Informatics, pp. 01-06, 2017.

- [2] Fahad Qureshi, JarmoTakala, Anastasia Volkova, Thibault Hilaire, "Multiplierless Unified Architecture for Mixed Radix-2/3/4 FFTs", 25th European Signal Processing Conference (EUSIPCO), IEEE 2017.

- [3] Fahad Qureshi, Muazam Ali, and JarmoTakala, "Multiplierless Reconfigurable Processing Element for Mixed Radix-2/3/4/5 FFTs", International Conference on 2017 IEEE.

- [4] Ms. A. Anjana and Mrs. A.V Ananthalakshmi, "Design of Reversible 32-Bit BCD Add-Subtract Unit using Parallel Pipelined Method", International Conference on Advances in Electrical, Electronics, Information, Communication and Bio-Informatics (AEEICB16), 2016 IEEE.

- [5] Matthew Morrison and NagarajanRanganathan, "Design of a Reversible ALU based on Novel Programmable Reversible Logic Gate Structures", 2015 IEEE Computer Society Annual Symposium on VLSI.

- [6] Mr. Abhishek Gupta, Mr. UtsavMalviya and Prof. VinodKapse, "Design of Speed, Energy and Power Efficient Reversible Logic Based Vedic ALU for Digital Processors", Computer Society Annual Symposium on VLSI, IEEE 2012.

- [7] H. Thapliyal and N. Ranganathan, "Design of Efficient Reversible Binary Subtractors Based on A New Reversible Gate," Proc. of the ComputerSociety Annual Symposium on VLSI, IEEE 2009.

- [8] M. Morrison and N. Ranganathan, "Design of a Reversible ALU Based on Novel Programmable Reversible Logic Gate Structures," IEEE International Symposium on VLSI, pp. 126-131, IEEE 2011.