(A High Impact Factor, Monthly, Peer Reviewed Journal)

*Visit: <u>www.ijirset.com</u>* Vol. 8, Issue 3, March 2019

# Review Paper on Multi-level DWT using Scaling Accumulator based on Distributed Arithmetic Technique

Swati Singhai<sup>1</sup>, Hemant Kumar Verma<sup>2</sup>

M. Tech. Scholar, Department of Electronics and Communication, TIT Bhopal, India<sup>1</sup>

Assistant Professor, Department of Electronics and Communication, TIT Bhopal, India<sup>2</sup>

**ABSTRACT**: Discrete Wavelet Transform (DWT) is a mathematical technique that provides a new method for signal processing. Due to various useful features like adaptive time-frequency window, lower aliasing distortion and efficient computational complexity, it is widely used in many signal and image processing applications. The DWT is highly computation intensive and many of its application need real-time processing to deliver better performance. In this paper the studied of 9/7 filter coefficient based DWT. The DWT is consisting of distributive arithmetic (DA) technique. DA technique is a multiplier-less technique to provide less time and area compared to multiplier based technique. The mathematical calculation of DA technique is present in this paper.

KEYWORDS: - 1-D Discrete Wavelet Transform (DWT), DA, Low Pass Filter, High Pass Filter, Xilinx Simulation.

### I. INTRODUCTION

The Wavelet Transform (WT) provides the time-frequency representation of the signal or image. To overcome the shortcoming of the Fourier Transform (FT) on constant resolution at all frequencies, the multiresolution based wavelet transform is used [1]. Here different frequencies are analyzed with different resolutions. Similar to FT, the signal is multiplied with a wavelet function which is a short oscillating function and the transform is computed for each segment. In the WT, time information is obtained by shifting the wavelet over the signal, while the frequencies are changed by contraction and dilation of the wavelet function. Continuous Wavelet Transform (CWT) retrieves the time-frequency content of the signal, DWT decomposes a discrete signal in the time domain by using dilated / contracted and translated version of a single basis function is named as wavelet. The one dimensional (1-D) and two dimensional (2-D) are applied in various application such as signal analysis, image coding.

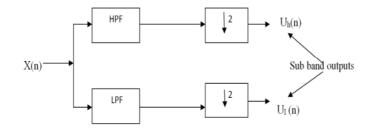

The computation in DWT is carried out using low pass and high pass filters. The sub bands are obtained by decomposing the input signal through low pass and high pass filters. The low pass and high pass filter pair forms a Quadrature Mirror Filter (QMF) for perfect signal reconstruction. They are short length Finite Impulse Response (FIR) filter. The computation block diagram of 1-D DWT is shown in Figure 1.

Figure 1: Computation block diagram of 1-D DWT

(A High Impact Factor, Monthly, Peer Reviewed Journal)

### Visit: <u>www.ijirset.com</u>

### Vol. 8, Issue 3, March 2019

Filtering unit consists of low pass and high pass filters and down sampling units. The low pass filter output is down sampled to obtained the low pass sub band output ul(n). Similarly, the high pass filter output is down sampled to obtained the high pass sub band output u h(n). This is equivalent to a two channel down sampled FIR filter computation. So, the computational unit comprises the Low Pass Filter (LPF), High Pass Filter (HPF) and a pair of down samplers. Multi resolution representations are very effective for analyzing the information content of the images. It is based on the wavelets theory which provides the details of signal between successive levels of scale or resolution.

#### **II. LITERATURE REVIEW**

**Maurizio Martina et al.** [1], presented a novel memory efficient high throughput scalable architecture for multi-level 2-D DWT. The authors propose a novel parallel stripe-based scanning method based on the analysis of the dependency graph of the lifting scheme. With the new scanning method for multi-level 2-D DWT, a memory efficient scalable parallel pipelined architecture is developed. The proposed architecture requires no frame memory and temporal memory, only for the 3-level DWT decomposition with an image size of 32 pixels processed concurrently. The elimination of frame memory and the small temporal memory lead to significant reduction in overall size. The presented architecture has a regular structure and achieves 100% hardware utilization.

**R. Praisline Jasmi et al. [2],** proposed a pipeline based architecture to perform 1-D DWT. The design focuses on the reduction of number of clock cycles. The intra and inter stage parallelism is enhanced by optimizing the computation overload at different decomposition level. The reported work mainly focuses on reducing the number and period of clock cycles for the DWT computation with little or no overhead on the hardware resources by maximizing the intrainter stage parallelisms of the pipeline. The inter stage parallelism is enhanced by optimally mapping the computational load as associated with the various DWT decomposition levels to the stages of the pipeline and by synchronizing their operations. The intra stage parallelism is enhanced by decomposing the filtering operation equally into two subtasks that can be performed independently in parallel and by optimally organizing the bitwise operations for performing each subtask so that the delay of the critical data path from a partial-product bit to a bit of the output sample for the filtering operation is minimized. It is shown that an architecture designed based on the presented scheme requires a smaller number of clock cycles compared to that of the architectures employing comparable hardware resources.

**Ms. Rashmi Patil et al. [3],** this paper provides an implementation of 1-DDiscrete wavelet transform DWT the usage of systolic array structure. It plays calculations of low skip and excessive pass coefficients by the use of best one multiplier. This architecture has been carried out and simulated using VLSI. The systolic nature of this architecture corresponds to a clock velocity of 19.27MHz for Coiflets1 wavelet and occasional electricity of 88.9mW for Haar wavelet. It has advantage for optimizing region and time. The structure is modular and cascadable for one or multi-dimensional DWT.

**S.G. Mallat et al. [4],** developed a methodology generic, scalable architectures for biorthogonal wavelet transform systems. The presented architectures offer efficient hardware utilization, significant reduction in area and better performance by combining the linear phase property of biorthogonal filters with decimation and interpolation. Wavelet, word lengths for data and coefficients are parameterized in this design. The method used to design the orthonormal, biorthogonal wavelet. It has the advantage that it reduces the partitioning and more flexible too. Significant reduction in terms of area requirements and increased throughput performance are achieved when compared to other filter banks based on DA, convolution or the lifting scheme. The improvement in speed was achieved by rearranging the matrix element into a two-dimensional array of processing elements interconnected as a mesh. The edges of each row and column were interconnected in torus structure, facilitating simultaneous implementation of several multiplications. The reported methodology ensures substantial reduction in propagation delay compared with the conventional algorithm, systolic array and Pseudo Number Theoretic Transformation (PNTT)-based implementation

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u> Vol. 8, Issue 3, March 2019

### III. DISTRIBUTED ARITHMETRIC (DA)

Let us consider the following sum of products [4]:

$$R = \sum_{k=1}^{L} X_{k} \times Y_{k} \tag{1}$$

Where  $X_k$  are fixed coefficients and they  $Y_k$  are the input data words. Equation (1) can be expressed in the form of a matrix product as:

$$R = \begin{bmatrix} X_{1} & X_{2} & \dots & X_{L} \end{bmatrix} \begin{bmatrix} Y_{1} \\ Y_{2} \\ \vdots \\ \vdots \\ Y_{L} \end{bmatrix}$$

(2)

Both  $X_k$  and  $Y_k$  are in two's complement format. The two's complement representation of  $X_k$  may be expressed as

$$X_{k} = -X_{k}^{M} 2^{M} + \sum_{i=N}^{M-1} X_{k}^{i} 2^{i}$$

(3)

Where  $X_k^i = 0$  or 1, and i = N, N+1... M and  $X_k^M$  is the sign bit and  $X_k^N$  is the least significant bit (LSB). Equation (3) can be expressed in matrix form as:

$$X_{k} = \begin{bmatrix} 2^{N} & 2^{N+1} & \dots & 2^{M} \end{bmatrix} \begin{bmatrix} X_{k}^{N} \\ X_{k}^{N+1} \\ \vdots \\ -X_{k}^{M} \end{bmatrix}$$

(4)

Similarly  $Y_k$  can be represented in two's complemented format as:

$$Y_{k} = -Y_{k}^{X} 2^{X} + \sum_{i=W}^{X-1} Y_{k}^{i} 2^{i}$$

(5)

Where  $Y_k^i = 0$  or 1, and i = W, W+1, ..., X and  $Y_k^M$  is the sign bit and  $Y_k^N$  is the least significant bit (LSB). Now on combining equations (1) and (3), we get-

$$R = -(R^{M}.2^{M}) + \sum_{i=N}^{M-1} (R^{i}.2^{i})$$

(6)

Where

$$R^{i} = \sum_{k=1}^{L} X_{k}^{i} Y_{k}$$

,  $i =$ N, N+1... M

Copyright to IJIRSET

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

### Vol. 8, Issue 3, March 2019

### **IV. PROPOSED ARCHITECTURE**

In this paper, we have proposed a high speed area efficient multiplier-less 1-D 9/7 wavelet filters based DA technique. 9/7 wavelet filters coefficient i.e. 9 low-pass and 7 high-pass wavelet filters coefficient are given in table1. We multiply the filter coefficients by 128 for simplification. The mathematical calculation for 1-D high pass filter output is explained by an example.

|       | Wavelet filters | Multiplied | 7 bit binary   |

|-------|-----------------|------------|----------------|

|       | coefficients    | by 128     | representation |

| $h_0$ | 0.60294901823   | 77         | 1001101        |

| $h_1$ | 0.26686441184   | 34         | 0100010        |

| $h_2$ | 0.07822326652   | 10         | 0001010        |

| $h_3$ | 0.01686411844   | 2          | 0000010        |

| $h_4$ | 0.026748757410  | 3          | 0000011        |

| $g_0$ | 0.55754352622   | 71         | 1000111        |

| $g_1$ | 0.29563588155   | 38         | 0100110        |

| $g_2$ | 0.02877176311   | 4          | 0000100        |

| $g_3$ | 0.045635881557  | 6          | 0000110        |

Table 1: Show high-pass and low-pass wavelet filters coefficient.

Where  $h_0$ ,  $h_1$ ,  $h_2$ ,  $h_3$ ,  $h_4$  are the Low pass filter coefficients and  $g_0$ ,  $g_1$ ,  $g_2$ ,  $g_3$  are the High pass filter coefficients. If we take the high pass coefficients  $g_0$ ,  $g_1$ ,  $g_2$  and  $g_3$  multiply by  $r_1$ ,  $r_2$ ,  $r_3$  and  $r_4$  then we get the High pass output  $Y_{_{H}}$  of the 9/7 filter as [6]:

$$Y_{H} = \begin{bmatrix} g_{0} & g_{1} & g_{2} & g_{3} \end{bmatrix} \begin{bmatrix} r_{1} \\ r_{2} \\ r_{3} \\ r_{4} \end{bmatrix}$$

(7)

Where  $r_1 = Y(n) + Y(n-6)$   $r_2 = Y(n-1) + Y(n-5)$   $r_3 = Y(n-2) + Y(n-4)$   $r_4 = Y(n-3)$ Let  $r_1=3$ ,  $r_2=4$ ,  $r_3=5$ ,  $r_4=6$  then

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: <u>www.ijirset.com</u>

Vol. 8, Issue 3, March 2019

$$Y_{H} = \begin{bmatrix} 71 & 38 & 4 & 6 \end{bmatrix} \begin{bmatrix} 3 \\ 4 \\ 5 \\ 6 \end{bmatrix} = 421$$

(8)

Now if we implement this with DA then

$$Y_{H} = \begin{bmatrix} 1000111 & 0100110 & 0000100 & 0000110 \end{bmatrix} \\ \begin{bmatrix} r_{1} \\ r_{2} \\ r_{3} \\ r_{4} \end{bmatrix}$$

(9)

Now we can make the DA matrix by the filter coefficients as

$$\begin{bmatrix} B_k \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 1 \\ 1 & 1 & 1 & 1 \\ 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 1 \\ 1 & 1 & 1 & 1 \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ \end{bmatrix}^{r_1}_{r_2} \begin{bmatrix} r_1 \\ r_1 + r_2 + r_4 \\ r_1 + r_2 + r_3 + r_4 \\ 0 \\ r_5 \\ r_2 \\ r_1 \end{bmatrix}$$

(10) (11)

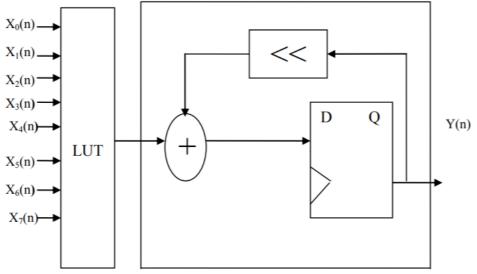

All the DA matrix output is shift and add, get the final output. The filter coefficients are pre stored in the LUT. The value thus accessed by the incoming address shall be added with the previous values to find the product of input and the coefficient values. The scaling accumulator is used for creating the delay in the product generation. The added values of the successive inputs are stored in D-flip-flop before the final product is obtained at Y(n).

(A High Impact Factor, Monthly, Peer Reviewed Journal)

Visit: www.ijirset.com Vol. 8, Issue 3, March 2019

#### Figure 2: Scaling Accumulator

#### V. CONCLUSION

The processor core architecture is used to achieve high degree of parallelism, capable of handling multiple blocks of inputs to implement the convolution based DWT. The implemented results show that the architecture achieves a high speed with a lower accessing time and reaches a speed performance suitable for real time low power embedded multimedia applications. The DA based DWT architecture will implemented Xilinx software and compared to previous paper shown in final paper.

#### REFERENCES

- Maurizio Martina, Guido Masera, Massimo Ruo Roch, and Gianluca Piccinini, -Result-Biased Distributed-Arithmetic-Based Filter Architectures for [1] Approximately Computing the DWTI, IEEE Transactions on Circuits and Systems-I: Regular Papers, Vol.62, No.8, August 2015.

- [2] R. Praisline Jasmi and Mr. B. Perumal, -Comparison of Image Compression Techniques using Huffman Coding, DWT and Fractal Algorithml, 2015 International Conference on Computer Communication and Informatics (ICCCI -2015), Jan. 08 - 10, 2015, Coimbatore, INDIA.

- [3] Ms. Rashmi Patil and kaumar "Low Power High Speed VLSI Architecture for 1-D Discrete Wavelet Transform", 978-1-4799-7678- 2/15/\$31.00 ©2015 IEEE.

- S.G. Mallat, "A Theory for Multiresolution Signal Decomposition: The Wavelet Representation", IEEE Trans. on Pattern Analysis on Machine [4] Intelligence, 110. July1989, pp. 674-693.

- [5] M. Alam, C. A. Rahman, and G. Jullian, "Efficient distributed arithmetic based DWT architectures for multimedia applications," in Proc. IEEE Workshop on SoC for real-time applications, pp. 333 336, 2003.

- [6] X. Cao, Q. Xie, C. Peng, Q. Wang and D. Yu, "An efficient VLSI implementation of distributed architecture for DWT," in Proc. IEEE Workshop on Multimedia and Signal Process., pp. 364-367, 2006. Archana Chidanandan and Magdy Bayoumi, "Area-Efficient Neda Architecture For The 1-D DCT/IDCT," ICASSP 2006.

- [7]

- M. Martina, and G. Masera, "Low-complexity, efficient 9/7 wavelet filters VLSI implementation," IEEE Trans. on Circuits and Syst. II, Express Brief [8] vol. 53, no. 11, pp. 1289-1293, Nov. 2006.

- [9] M. Martina, and G. Masera, "Multiplierless, folded 9/7-5/3 wavelet VLSI architecture," IEEE Trans. on Circuits and syst. II, Express Brief vol. 54, no. 9, pp. 770-774, Sep. 2007.

- [10] Gaurav Tewari, Santu Sardar, K. A. Babu, "High-Speed & Memory Efficient 2-D DWT on Xilinx Spartan3A DSP using scalable Polyphase Structure with DA for JPEG2000 Standard," 978-1-4244-8679-3/11/\$26.00 ©2011 IEEE.

- [11] B. K. Mohanty and P. K. Meher, "Memory Efficient Modular VLSI Architecture for Highthroughput and Low-Latency Implementation of Multilevel Lifting 2-D DWT", IEEE TRANSACTIONS ON SIGNAL PROCESSING, VOL. 59, NO. 5, MAY 2011.

- [12] B. K. Mohanty and P. K. Meher, "Memory-Efficient High-Speed Convolution-based Generic Structure for Multilevel 2-D DWT", IEEE Transactions On Circuits Systems For Video Technology.

- [13] B. K. Mohanty and P. K. Meher, "Efficient Multiplierless Designs for 1-D DWT using 9/7 Filters Based on Distributed Arithmetic", ISIC 2009.