| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.089| ||Volume 9, Issue 4, April 2020||

# Neuromorphic Computing: Implementation of Hardware Equivalent Structure of Neuron to Mimic the Neurobiological Architectures in Human Brain

Prof. Vrushali Sakharkar<sup>1</sup>, Mayur Chilamwar<sup>2</sup>, Abhay Lode<sup>3</sup>

Assistant Professor, Department of Computer Science and Engineering, Prof.Ram Meghe Institute of Technology &

Research , Amravati, Maharashtra, India<sup>1</sup>

U.G Student, Department of Computer Science and Engineering, Prof.Ram Meghe Institute of Technology & Research

,Amravati,Maharashtra,India<sup>2,3</sup>

**ABSTRACT:** Neuromorphic computing utilizes associate engineering approach or methodology supported by the activity of the biological brain. this sort of approach will build technologies a lot of versatile and pliable, and promote a lot of correct results than different varieties of ancient architectures, for example, the von Neumann design that's thus helpful in ancient hardware style. Neuromorphic computing is additionally called neuromorphic engineering. Neuromorphic computing has been around for a jiffy, however it's currently getting down to be applied in new and other ways. associated example is that the proposal to form neuromorphic chips that are a lot of complicated in nature than ancient microprocessors. Neuromorphic chips would have architectures a lot of just like the neurons of the human brain, permitting them to method data in additional specialised ways in which. specialists make a case for that the von Neumann chips, that were created use of in previous decades as Moore's law accelerated, were primitive compared to new styles. The heritage microchip performance styles were created a lot of for crunching numbers and handling the types of high-level work that today's machine learning and computing systems need. the thought is that new neuromorphic chips may be created to a lot of simply accomplish these new varieties of technological goals.

KEYWORDS: Neuromorphic, Neuron, Synapses, Neural Network, Spikes.

## I. INTRODUCTION

The phrase Neuromorphic Computing incorporates a long history, geological dating back a minimum of to the Nineteen Eighties, once legendary Caltech investigator Carver Mead projected planning ICs to mimic the organization of living somatic cell cells. However recently the term has taken on a far a lot of specific which means to denote a branch of neural network analysis that has diverged considerably from the orthodoxy of convolutional deep-learning because the name implies—if you are Greek, anyway—neuromorphic networks model themselves closely on biological nerve cells, or neurons. This can be quite not like trendy deep-learning networks, thus it's worthy to require a fast verifying biological neurons

In the cell body square measure structures that rework the various pulse trains inbound over the dendrites into associate degree output pulse train. A minimum of twenty totally different rework sorts are known in nature, starting from straightforward logic-like functions to some rather subtle transforms. one among the foremost attention-grabbing for researchers—and the foremost wide employed in neuromorphic computing—is the leaky integrator: a operate that adds up pulses as they arrive, whereas perpetually decrementing the total at a set rate. If the total exceeds a threshold, the cell body outputs a pulse.

Neuromorphic computers use subject structures shapely on neurons. However there square measure many alternative implementation approaches, starting from pure software system simulations to dedicated ICs. The most effective thanks to outline the sector because it exists these days could also be to distinction it against ancient neural networks. Each square measure networks within which comparatively straightforward computations occurs at the nodes.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.089| ||Volume 9, Issue 4, April 2020||

# II. PROPOSED WORK

Hardware Equivalent Structure of Neurons:-

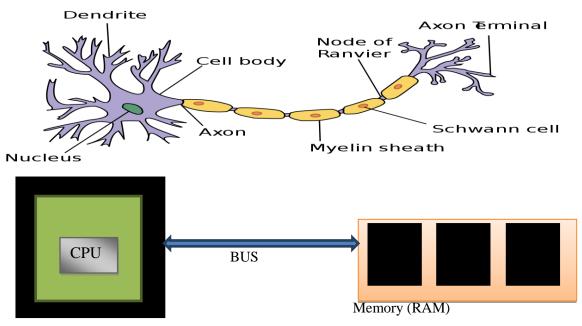

Fig1.1: Hardware Equivalent Structure of Neuron

In Hardware approach the cell body are thought of as associate degree Processor Core associate degree nerve-fiber as a BUS and synapses as a Memory.

In the cell body square measure structures that rework the various pulse trains inbound over the dendrites into associate degree output pulse train. a minimum of twenty totally different rework sorts are known in nature, starting from straightforward logic-like functions to some rather subtle transforms. one among the foremost attention-grabbing for researchers—and the foremost wide employed in neuromorphic computing—is the leaky integrator: a operate that adds up pulses as they arrive, whereas perpetually decrementing the total at a set rate. If the total exceeds a threshold, the cell body outputs a pulse.

Synapses, dendrites and cell bodies square measure 3 of the four elements. The fourth one is that the axon: the tree-like fiber that conducts output pulses from the cell body into the animal tissue, ending at synapses on alternative cells' dendrites or on muscle or organ synapses. The neuromorphic computers use subject structures shapely on neurons. However there square measure many alternative implementation approaches, starting from pure software system simulations to dedicated ICs. The most effective thanks to outline the sector because it exists these days could also be to distinction it against ancient neural networks. Each square measure networks within which comparatively straightforward computations occur at the nodes. However on the far side that generalization there square measure several vital variations.

Perhaps the foremost basic distinction is in signal. The nodes in ancient neural networks communicate by causing numbers across the network, sometimes diagrammatic as either floating-point or whole number digital quantities. Neuromorphic nodes send pulses, or generally strings of pulses, within which temporal order and frequency carry the information— in alternative words, styles of pulse code modulation. this can be almost like what we tend to observe in biological nervous systems.

A second vital distinction is within theoperation performed in every node. Standard network nodes do arithmetic: they multiply the numbers inbound on every of their inputs by present weights and add up the product. Mathematicians see this as a straightforward inner product of the input vector and therefore the weight vector. The ensuing total could then be subjected to some non-linear operate like social control, min or Georgia home boy setting, or no matter alternative artistic impulse moves the network designer. The quantity is then sent on to consecutive layer within

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.089| ||Volume 9, Issue 4, April 2020||

## the network.

In distinction, neuromorphic nodes, like somatic cell bodies, will perform an oversized array of pulse-oriented functions. Most typically used, as we've got mentioned, is that the leaky integrate and spike operate, however varied designers have enforced several others. Like real neurons, neuromorphic nodes sometimes have several input connections feeding in, however sometimes only one output. In regard to living cells, neuromorphic inputs square measure typically known as synapses or dendrites, the node could also be known as a somatic cell, and therefore the output tree associate degree nerve fiber.

## Need of New Computational Techniques:-

## > Moore's-Law:

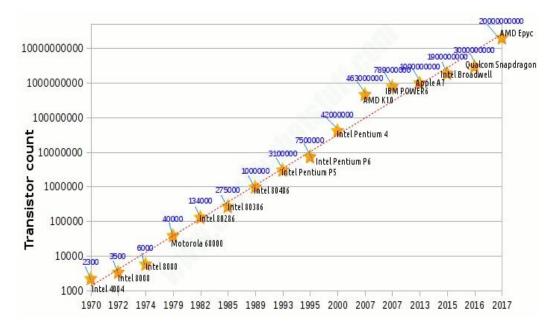

Moore's Law is that the observation created in 1965 by Gordon Moore, co-founder of Intel, that the quantity of transistors per square measure on computer circuits had doubled each year since the integrated circuit was madeup. Moore foretold that this trend would continue for the predictable future. In resultant years, the pace stalled a small amount, however information density has doubled around each eighteen months, and this is often this definition of Moore's Law, that Moore himself has blessed. Most consultants, as well as Moore himself, expect Moore's Law to carry true till 2020-2025.

## Fig 2.1: Statistics of Moore's Law

## How Moore's Law going to End?

For many years, as transistors got smaller, they became a lot of energy economical. Now, however, they need gotten therefore little, as little as 10 nano-meters, that the channel that carries the electrical current through the junction transistor cannot continuously contain it. This generates heat which might wear out the transistors a lot of quickly, creating them even a lot of vulnerable to outflow. Heat isn't simply restricted to at least one junction transistor. Billions of transistors leak will seriously threaten the integrity of the complete chip, that the processor should scale back the quantity of voltage it takes in or throttle the quantity of transistors in use to forestall heating, limiting the process power of the chip.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.089| ||Volume 9, Issue 4, April 2020||

> Traditional Architecture of Processors(Von Neumann Architecture):-

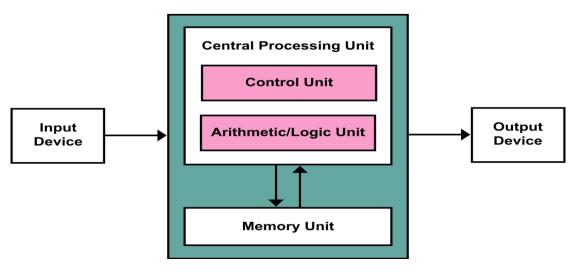

Fig2.2: Von Neumann Architecture

The von Neumann design—also called the von Neumann model or Princeton architecture—is a laptop architecture supported a 1945 description by the scientist and scientist John von Neumann et al within the first Draft of a Report on the EDVAC. That document describes a style design for associate electronic computing device with these components:

- A process unit that contains associate arithmetic logic unit and processor registers

- A management unit that contains associate instruction register and program counter

- Memory that stores information and directions

- External mass storage

- Input and output mechanisms

The term "von Neumann architecture" has evolved to mean associate stored-program laptop during which an instruction fetch and an information operation cannot occur at an equivalent time as a result of they share a typical bus. This is often observed because the von Neumann bottleneck and infrequently limits the performance of the system which also leads to need of new computational techniques.

## **III. IMPLEMENTATION OF NEUROMORPHIC ARCHITECTURE**

Carver Mead (An yank somebody, CIT, Chicago) might have dreamt of implementing the structure of a nerve cell in atomic number 14, however developers of today's deep-learning networks have abandoned that concept for a way easier approach. Modern, standard neural networks square measure in impact package simulations—computer programs that perform the matrix arithmetic outlined by the neural spec. The network is simply a graphic illustration of an outsized algebra computation.

Given the inefficiencies of simulation, developers are fast to adopt optimizations to scale back the computing load, and hardware accelerators to hurry execution. Information compression, use of shorter variety formats for the weights and outputs, and use of sparse-matrix algorithms have all been applied. GPUs, clever arrangements of multiply-accumulator arrays, and FPGAs are used as accelerators. A stimulating recent trend has been to explore FPGAs or ASICs organized as data-flow engines with embedded RAM, in an endeavour to scale back the huge memory traffic masses that may type round the accelerators—in impact, extracting a data-flow graph from the network and coding it in atomic number 14.

In distinction, atomic number 14 implementations of neuromorphic processors tend to gibe architecturally the biological neurons they consciously mimic, with recognizable hardware blocks similar to synapses, dendrites, cell bodies, and axons. The implementations square measure sometimes, however not continuously, digital, permitting them to run a lot

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.089| ||Volume 9, Issue 4, April 2020||

of quicker than organic neurons or analogue emulations, however they maintain the periodic operation of the biological cells and square measure usually event-driven, giving the chance for immense energy savings compared to package or to synchronous arithmetic circuits.

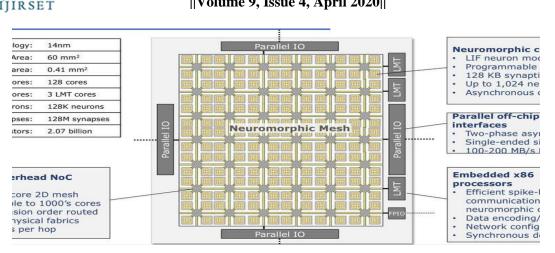

## Neuromorphic Architecture:-

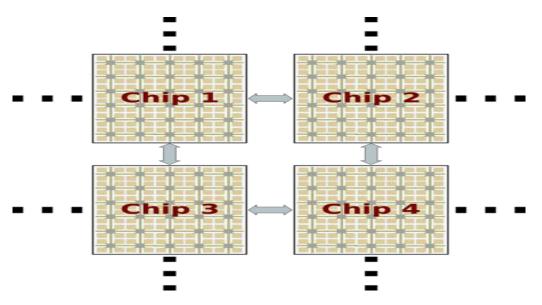

Fig.3.1: Neuromorphic Architecture

• Implementation Example (Intel-Loihi Architecture):-

The chip consists of a many-core mesh of 128 neuromorphic cores, 3 Lakemont x86 cores (Quark), associated an off-chip communication interface that enables the chip to scale bent on several different chips within the four planar directions (as shown on the right). The enforced mesh protocol supports up to four,096 on-chip cores and up to sixteen,384 chips.

The chip itself implements a completely asynchronous many-core mesh of 128 neuromorphic cores. It implements a spiking neural network (SNN) whereby at associate given time one or a lot of the enforced neurons could channelize an impulse (i.e., spike) to its neighbours through the directed links (synapses). All neurons have a neighbourhood state with their own set of rules that affects their evolution and therefore the temporal arrangement of spike generation. Interaction is entirely asynchronous, sporadic, and freelance of the other vegetative cell on the network. A novel feature of Loihi'sneuromorphic learning cores is their integrated engine that permits full on-chip learning via programmable code learning rules.

Core-to-core communication is finished in mistreatment packetized messages with write, browse request, and skim response messages for core management and x86-to-x86 electronic messaging, spike messages, and barrier messages (for synchronization).

Loihi implements 128 neuromorphic cores, every containing one, 24 primitive spiking neural units sorted into tree-like structures so as to modify the implementation. Every of these teams share an equivalent fan-in and fan-out connections, configuration, and state variables in 10 study reminiscences.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.089| T ||Volume 9, Issue 4, April 2020||

#### Fig3.2-Intel Loihi Architechture

## **IV.CONCLUSION**

Neuromorphic design can facilitate in betterment of existing computation technology and additionally act as confirmatory 0.5 for the classic systems, as already it's serving to beat the top of Moore's law in most of the classic system.

The classic design that is mathematician design square measure, they're doing the logical and analytical calculation all right and that they are like one and half brain thus integrating them with Neuromorphic design that are higher in pattern recognition, machine learning, creativeness that is just like the spouse of brain will cause development of higher operating and a lot of economical future machine which might be ready to replicate the Human Brain in term of process and potency.

## V.FUTURE APPROACH

- 1) Neuromorphic Computers will simulate advanced brain simulation which might be useful in detection of assorted diseases associated with brain and additionally helps in understanding the operating a lot of effectively.

- Coming up with a ADP system that produces logical selections is comparatively simple. AN example is IBMs antipersonnel bomb beating the globe chess champion. However solely biological entities will have a brain which will develop its own consciousness and sub-consciousness.

- 3) Advanced AI (Artificial Intelligence) systems can facilitate in creating of Advanced War Robots, Intelligent Drones, Self Driving automobile, etc.

- 4) Designing a computing system that makes logical decisions is relatively easy. An example is IBMs Big Blue beating the world chess champion. But only biological entities can have a brain that can develop its own consciousness and sub-consciousness.

- 5) Simulating Advance Structures of Genetics which will help in advancement of Genetic Engineering field.

## **References**

- 1. Mead, Carver (1990). "Neuromorphic electronic systems" . Proceedings of the IEEE. **78** (10): 1629–1636. doi:10.1109/5.58356

- 2. Monroe, D. (2014). "Neuromorphic computing gets ready for the (really) big time". Communications of the ACM. **57** (6): 13–15. doi:10.1145/2601069

- Davies, Mike; et al. (January 16, 2018). "Loihi: A NeuromorphicManycore Processor with On-Chip Learning". IEEE Micro. 38

- 4. Maan, A. K.; Jayadevi, D. A.; James, A. P. (January 1, 2016). "A Survey of Memristive Threshold Logic Circuits". IEEE Transactions on Neural Networks and Learning Systems. **PP** (99): 1734–1746.

- 5. Zhou, You; Ramanathan, S. (August 1, 2015). "Mott Memory and Neuromorphic Devices". Proceedings of the IEEE. 103