e-ISSN: 2319-8753 | p-ISSN: 2320-6710

DIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 9, Issue 12, December 2020

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

### Impact Factor: 7.512

9940 572 462

6381 907 438

$\bigcirc$

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

||Volume 9, Issue 12, December 2020||

## IOT Application development on Artix 7 FPGA and Thingspeak IOT Cloud

A. Neha Rao, Pradeep Singh Yadav,

M. Tech, VLSI Design, Electronic & Telecommunication, Shri Shankaracharya Technical Campus(SSGI), Bhilai,

C.G., India

Assistant Professor, Electronic & Telecommunication, Shri Shankaracharya Technical Campus (SSGI), Bhilai,

C.G., India

**ABSTRACT:** FPGA with Internet of Things is a latest technology, and this technique has been used to introduce many smart devices with wonderful applications in our day today life. One more challenge for IOT is to handle vast amount of sensing the data generated from smart devices that are resource limited and subject to missing data due to link failures. In this paper mainly going to focus on FPGA with IOT platform, i.e., the use of low-cost FPGA implementation of entire IOT subset including TCP/IP protocol, Control System and Data Acquisition etc. In the past few years, we have enormous improvement in the field of IOT applications on FPGA platform. This technique has been updated with low cost, efficient power usage with real time observing and remote recognizing system. The main objective of this research is to focus how the FPGA based hardware resources can be accessed from anywhere. The maintenance cost of servers can be reduced by building a cloud-based monitoring system. The data losses are avoided with the help of this technique. To make the communication with various internets coupled devices (computer, tablet, mobile phone) at the same time anywhere in the world. There are various business spaces it needs you to observe temperature, light and update the status to the cloud. The temperature, light must be maintained at the moderate level in food preservation process. IOT based temperature, light monitoring system help us to monitor the food preservation system and update the data to the cloud at the regular interval. Artix-7 is latest series of FPGA for complex VHDL design with new VIVADO platform.

KEYWORDS: IOT, Thingspeak, Temperature and Light Monitoring System, Artix-7 FPGA, Vivado 2018.

#### I. INTRODUCTION

Web services with FPGA based hardware have already been realized and defined. Their embedded nature permits the developers to simply adjust those services to energetically interrelate with their surroundings, e.g., to attain real-world measurement data or control various actuators. Such entities can be called environmentaware web services in difference to classical web services that work on remote physical or virtual machines. The IOT applications can be developed by implementing IP address with the particular VHDL code in order to make Internet of Things.

IOT is implemented on various FPGA devices to project diverse devices for various applications. As the number of IOT devices are increasing fast, results the need to build a smart world of devices with less human stimuli [7]. General idea of IOT is to assign an IP address to a relative device to be pinged out from inaccessible distance, broadly used for real time data collection [14].

#### **Internet of Things**

The internet has enabled an unpredictable growth of information sharing with the introduction of embedded and sensing technology, the number of smart devices including sensors, mobile phones, RFIDs, and smart grids has grown quickly in recent years. Ericsson and Cisco predicted that fifty billion small, embedded sensors and actuators will be associated with the internet by 2020 [15].

#### Artix-7 FPGA

The Field Programmable Gate Array (FPGA) is a family of reconfigurable hardware, where Field Programmable means the operation changing capability in the field, and Gate Array means the construction of basic internal architecture of the device. Digital computing tasks can be developed in software and compiled into a bit stream

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

#### ||Volume 9, Issue 12, December 2020||

file. This bit stream file contains information about how the components should be wired together. FPGAs combine the best parts of ASICs and processor-based systems, in fact FPGAs are parallel in nature. Advantage of using a software programmed processor is that software is very flexible to change while a disadvantage is that performance can suffer if the clock is not fast. The advantage of an ASIC is that it can provide very high performance because of its dedicated type of operation and its disadvantages are:

- 1) High cost to volume ratio.

- 2) Extended delay between designs to end product.

- 3) Incapability to include new changes after the system is fabricated and

- 4) Difficulties in debugging errors.

FPGAs fill the gap between hardware and software and offer numerous advantages such as:

- 1) Flexibility,

- 2) Reliability,

- 3) Low cost,

- 4) Fast time-to-market and

- 5) Long term maintenance.

After observing this, we conclude that an FPGA is the best reconfigurable hardware platform for the implementation of IoT applications.

#### II. METHODOLOGY

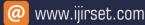

We are using7<sup>th</sup> series FPGA, which is Artix7. We areimplementing our proposed model inVivado 18 for simulation and bit file generation. Below diagram describes about internal architecture of Artix 7 FPGA.

Artix7 devices provide the highest performance-per-watt fabric, transceiver line rates, DSP processing, and AMS integration in a cost-optimized FPGA. Featuring the MicroBlaze soft processor and 1,066Mb/s DDR3 support, the family is the best value for a variety of cost and power-sensitive applications including software-defined radio, machine vision cameras, and low-end wireless backhaul.

The general FPGA architecture is shown in Fig. 1 consists of three types of modules. They are I/O blocks, Configurable logic blocks (CLB) and Switch Matrix/Interconnection Wires. The FPGA has two dimensional arrays oflogic blocks which is used to arrange the interconnection between the logicblocks.

FPGAs have gained rapid growth over the past decade because they are useful for a wide range of applications. Some of the applications are cryptography, filtering and communication encoding and many more.

Figure 1: Block diagram of FPGA.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

#### ||Volume 9, Issue 12, December 2020||

Vivado Design Suite is a software suite produced by Xilinx for synthesis and analysis of HDL designs, superseding Xilinx ISE with additional features for system on a chip development and high-level synthesis. Vivado represents a ground-up rewrite and re-thinking of the entire design flow (compared to ISE). Like the later versions of ISE, Vivado includes the in-built logic simulator ISIM. Vivado also introduces high-level synthesis, with a toolchain that converts C code into programmable logic.

| <u>E</u> ile <u>E</u> dit Flow <u>T</u> ools Rep    | orts Window Layout View                 | Help Q          | <ul> <li>Quick Access</li> </ul> |            |                   |                    |          |          |                          |                  |     |     | Implem   | entation C | omplete |     |

|-----------------------------------------------------|-----------------------------------------|-----------------|----------------------------------|------------|-------------------|--------------------|----------|----------|--------------------------|------------------|-----|-----|----------|------------|---------|-----|

| 🖕 🔸 🔺 🖬 🐘 🗙 🗎                                       | ▶ III I I I I I I I I I I I I I I I I I | ×               |                                  |            |                   |                    |          |          |                          |                  |     |     | III Defa | ault Layou |         | ~   |

| low Navigator — — — — — — — — — — — — — — — — — — — | PROJECT MANAGER - xadc_new              |                 |                                  |            |                   |                    |          |          |                          |                  |     |     |          |            | 1       | ?)  |

| PROJECT MANAGER                                     | Sources                                 |                 | 2 _ D Ľ X                        | Project Su | mmarv             | ×                  | OT.vhd   | ×        |                          |                  |     |     |          |            | ? 🗆     | C5  |

| Settings                                            |                                         |                 |                                  |            |                   |                    |          |          |                          |                  |     |     |          |            |         |     |

| Add Sources                                         | Q 素 ≑ + 2                               | 0               | ٥                                | C:/Users/  | Neha/D            | esktop/W           | /IFI_XAD | C/xadc_r | new.srcs/source          | es_1/new/IOT.vho | 1   |     |          |            |         | ×   |

| Language Templates                                  | V Design Sources (1)                    |                 | Â                                | Q, 🔛       | *                 | *                  | X   E    |          | × // [                   |                  |     |     |          |            |         | ٥   |

| IP Catalog                                          | IOT(Behavioral) (IC A1 : ADC_C(Beh      |                 |                                  |            |                   |                    |          | ith.all; |                          |                  |     |     |          |            |         | ^   |

| + I building                                        | L1:LCD(Behavi                           |                 |                                  |            | : ieee<br>:ity I( |                    | gic_uns  | signed.a | all;                     |                  |     |     |          |            |         |     |

| IP INTEGRATOR                                       | U1 : UART(Beha                          |                 |                                  | 16 ;       | Port              |                    |          |          |                          |                  |     |     |          |            |         |     |

|                                                     | Constraints (1)                         | noral) (OART.VI |                                  | 17         |                   | clk                |          |          | STD_LOGIC;               |                  |     |     |          |            |         | U   |

| Create Block Design                                 | ✓ □ constrs 1(1)                        |                 |                                  | 18<br>19   |                   | vauxp6<br>vauxn6   |          |          | STD_LOGIC;<br>STD_LOGIC; |                  |     | -   | - Auxili | ary Char   | nel 6   |     |

| Open Block Design                                   | adcxdc                                  |                 |                                  | 20         |                   | vauxp7             |          |          | STD_LOGIC;               |                  |     | -   | - Auxili | ary Chan   | nel 7   |     |

| Generate Block Design                               | Simulation Sources (1)                  |                 |                                  | 21         |                   | vauxn7             |          |          | STD_LOGIC;               |                  |     |     |          |            |         |     |

|                                                     | > □ sim_1(1)                            |                 |                                  | 22<br>23   |                   | vauxp14<br>vauxn14 |          |          | STD_LOGIC;<br>STD_LOGIC; |                  |     | -   | - Auxili | ary Char   | nel 14  |     |

| SIMULATION                                          | V 📭 IOT(Behavioral                      | ) (IOT.vhd) (3) |                                  | 24         |                   | vauxp15            |          |          | STD_LOGIC;               |                  |     |     | - Auxili | ary Char   | nel 15  |     |

| Run Simulation                                      | > A1 : ADC_C                            | Behavioral) (AD |                                  | 25         |                   | vauxn15            |          |          | STD_LOGIC;               |                  |     |     |          |            |         |     |

| rtan olmalaton                                      |                                         |                 |                                  | 26         |                   | txd<br>lcd e       |          |          | t STD_LOGIC;             | ;                |     |     | enabl    | e contro   |         | ~   |

| RTL ANALYSIS                                        | Hierarchy IP Sources L                  | ibraries Co     | mpile Order                      | <          |                   |                    |          |          | c stu ioqic,             |                  |     |     | CHUDA    | C CONCLO   | >       |     |

| > Open Elaborated Design                            | Tcl Console Messages                    | Log Reports     | s Desian Runs ×                  |            |                   |                    |          |          |                          |                  |     |     |          | -          | _ 0     |     |

| > Open Elaborated Design                            |                                         | Log Reports     | s Design Kuns X                  |            |                   |                    |          |          |                          |                  |     |     |          | 1          |         |     |

| SYNTHESIS                                           | Q, I ★   ♦   I €   ≪                    | $  \rangle   $  | + %                              |            |                   |                    |          |          |                          |                  |     |     |          |            |         |     |

|                                                     | Name                                    | Constraints     | Status                           | WNS        | TNS               | WHS                | THS      | TPWS     | Total Power              | Failed Routes    | LUT | FF  | BRAMs    | URAM       | DSP     | Sta |

| Run Synthesis                                       | ✓ ✓ synth_1 (active)                    | constrs_1       | synth_design Complete!           |            |                   |                    |          |          |                          |                  | 632 | 273 | 0.00     | 0          | 1       | 9/  |

| > Open Synthesized Design                           | ✓ impl_1                                | constrs_1       | route_design Complete!           | NA         | NA                | NA                 | NA       | NA       | 10.932                   | 0                | 631 | 273 | 0.00     | 0          | 1       | 9/  |

|                                                     | 🗸 🚍 Out-of-Context Module Ru            | ns              |                                  |            |                   |                    |          |          |                          |                  |     |     |          |            |         |     |

| IMPLEMENTATION                                      | ✓ xadc_wiz_0_synth_1                    | xadc_wiz_0      | synth_design Complete!           |            |                   |                    |          |          |                          |                  | 0   | 0   | 0.00     | 0          | 0       | 1   |

| Run Implementation                                  | × <                                     |                 |                                  |            | _                 |                    |          |          |                          |                  |     |     |          |            |         |     |

Figure 2: Proposed system implementation in Vivado 18.1

The Vivado Design Suite 2013.1 release includes the IP Integrator (IPI) feature, a new IP-centric design flow for accelerating the time-to-system integration. IPI increases programmable design productivity by 4X, lowering design costs and accelerating development of smarter systems.

| Nizard (3.3)                                                                                        |                                                 |                                                             |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------|

| mentation 🖀 IP Location C Switch to Defaults                                                        |                                                 |                                                             |

| ow disabled ports                                                                                   | Component Name xadc_wiz_0                       |                                                             |

| - s_axi_ite                                                                                         | Basic ADC Setup Alarms Channel Sequencer Summar | У                                                           |

| + s_drp<br>   + Vp_M<br>   + Vaux0                                                                  | Interface Options                               | Timing Mode                                                 |

|                                                                                                     | ◯ AXI4Lite ● DRP ◯ None                         | Continuous Mode      Event Mode                             |

| + Vaux4     vooint_alarm_out       + Vaux5     vooaux_alarm_out       + Vaux6     vcopint_alarm_out | Startup Channel Selection                       | DRP Timing Options                                          |

| + Vaux? vecpaux_alarm_out -<br>+ Vaux8 vecddro_alarm_out -<br>+ Vaux9 et_out -                      | Simultaneous Selection                          | Z Enable DCLK                                               |

| + Vaux10 channel_out[4:0] =<br>+ Vaux11 muxaddr_out[4:0] =                                          | Independent ADC                                 | DCLK Frequency(MHz) 50 (8.0 - 250.0)                        |

| + Vaux12 eoo_out -                                                                                  | Single Channel                                  | ADC Conversion Rate(KSPS) 962 (39.0 - 962.0]                |

| + Vaux14 alarm_out -<br>+ Vaux15 eos_out -                                                          | <ul> <li>Channel Sequencer</li> </ul>           | Acquisition Time (CLK) 4                                    |

| m_axis_aolk buzy_out<br>s_axis_aolk jtaglooked_out<br>m_axis_resetn jtagmodified_out -              | AXI4 STREAM Options                             | Clock divider value = 2<br>ADC Clock Frequency(MHz) = 25.00 |

| s_axi_aolk jtagbusy_out<br>s_axi_aresetn temp_out[11:0]<br>dok_jin                                  | Enable AXI4Stream                               |                                                             |

| reset_in<br>convist_in<br>convist_ik in                                                             | FIFO Depth 7 [7 - 1020]                         |                                                             |

|                                                                                                     |                                                 |                                                             |

Figure 3: IPI of ADC for analog temperature and light sensor

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512| ||Volume 9, Issue 12, December 2020||

The **Vivado** IDE allows you to use one or many **constraint files**. While using a single **constraint file** for the entire compilation flow might seem more convenient, it can be a challenge to maintain all the **constraints** as the design becomes more complex.

Finally, we have to generate bitstream file for flash of the FPGA. We can select bitstream option in Vivado.

| Q                                                                                                                                                                                          | Bitstream                                                                                    |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Project Settings                                                                                                                                                                           | Specify various settings related to writing bitstream                                        |  |  |  |  |  |  |

| General<br>Simulation<br>Elaboration                                                                                                                                                       | ⑦ Note: Additional bitstream settings will be available once you open an implemented design. |  |  |  |  |  |  |

| Synthesis                                                                                                                                                                                  | Write Bitstream (write_bitstream)                                                            |  |  |  |  |  |  |

| Implementation                                                                                                                                                                             | tcl.pre                                                                                      |  |  |  |  |  |  |

| Bitstream                                                                                                                                                                                  | tcl.post                                                                                     |  |  |  |  |  |  |

| > IP                                                                                                                                                                                       | -raw_bitfile                                                                                 |  |  |  |  |  |  |

| T 1 C                                                                                                                                                                                      | -mask_file                                                                                   |  |  |  |  |  |  |

| Tool Settings                                                                                                                                                                              | -no_binary_bitfile                                                                           |  |  |  |  |  |  |

| Project<br>IP Defaults                                                                                                                                                                     | -bin_file                                                                                    |  |  |  |  |  |  |

| Source File                                                                                                                                                                                | -readback_file                                                                               |  |  |  |  |  |  |

| Display<br>WebTalk                                                                                                                                                                         | -logic_location_file                                                                         |  |  |  |  |  |  |

|                                                                                                                                                                                            | -verbose                                                                                     |  |  |  |  |  |  |

| Help                                                                                                                                                                                       | More Options                                                                                 |  |  |  |  |  |  |

| <ul> <li>&gt; Text Editor</li> <li>3rd Party Simulators</li> <li>&gt; Colors</li> <li>Selection Rules</li> <li>Shortcuts</li> <li>&gt; Strategies</li> <li>&gt; Window Behavior</li> </ul> |                                                                                              |  |  |  |  |  |  |

|                                                                                                                                                                                            | Select an option above to see a description of it                                            |  |  |  |  |  |  |

|                                                                                                                                                                                            |                                                                                              |  |  |  |  |  |  |

Figure 4: Bitstream file generation.

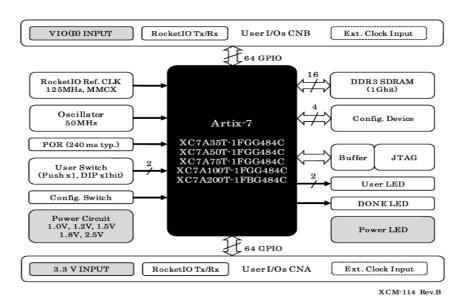

Fig. 5 is a proposed model of our complete system. A temperature sensor is a thermocouple or a resistance temperature detector (RTD) that gathers the temperature from a specific source and alters the collected information into understandable type foran apparatus or an observer. Here we are using LM35 as a temperature sensor. Temperature sensors are used in several application namely HV (high voltage) system and AC (alternating current) system environmental controls, medical devices, food processing units, chemical handling, controlling systems, automotive under the hood monitoring andetc.

Figure 5: Block diagram of our proposed model.

LDR and resistor connected in series to form a light sensor. It gives the input to ADC using IP Integrator and further connected with FPGA.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

#### ||Volume 9, Issue 12, December 2020||

Artix 7 FPGA starter kit consists of on board 8 channels ADC with channel connected with LM35 temperature and LDR sensor. VHDL code is used to perform conversion of analog to digital and read the LM35 output as a digital data and 2\*16 LCD is used to display theoutput.

ESP8266 Wi-Fi Module is used to transmit the temperature data wirelessly to the Wi- Fi Modem at the other end with internet connection. ESP826 Wi-Fi Module can be initialized using set of AT Commands. After the initialization process, we have to program for configuring the Wi-Fi module as a TCP/IP client. We are using Thingspeak as a IOT server for logging the data.

#### **III. RESULT AND DISCUSSION**

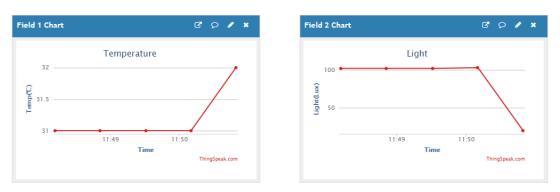

ThingSpeak is an open-source Internet of Things (IoT) application and API to store and retrieve data from things using the HTTP and MQTT protocol over the Internet or via a Local Area Network. ThingSpeak enables the creation of sensor logging applications, location tracking applications, and a social network of things with status updates".

We provide the power supply to our development board and test in differentcases. LM35 and LDR give temperature and light analog values, respectively. IPI of ADC convert it into digital value and further scale into decimal values. UART send values to ESP8266 via serial communication. LCD display same value in development board.

Channel Stats Created: <u>3.months.ago</u> Last entry: <u>2.months.ago</u> Entries: 62

Figure 6: Temperature and Light values are logging into ThingSpeak server.

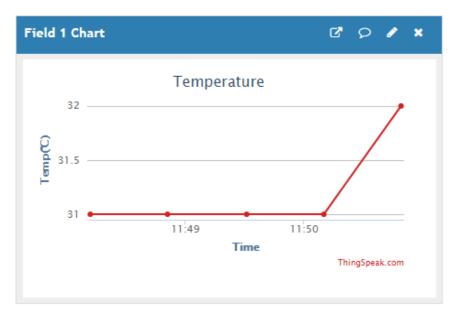

Figure 7: Temperature values in different time intervals.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

||Volume 9, Issue 12, December 2020||

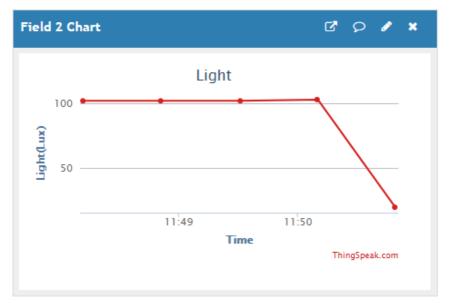

Figure 8: Light values in different time intervals.

#### IV. CONCLUSION AND FUTURE WORK

The IOT based embedded system has facing many challenges in difficult IOT applications. The Field Programmable Gate array structure is the alternate arrangement to overcome the problem which is facing in ARM processor. In this paper, we have introduced the study of technology paradigm for IOTs on FPGA Platform. The IOT based FPGA includes communication protocols, Data Acquisition and controlling systems. The temperature, Light has been monitored with the combination of IOT and FPGA architecture and for every second time period the temperature, light has been updated in the particular IP address. There are various business spaces it needs you to observe temperature, light and update the status to the cloud. The temperature must be maintained at the lowest level in food preservation process. IOT based temperature monitoring system help us to monitor the food preservation system temperature, light and update the data to the cloud at the regular interval.

#### REFERENCES

- 1. Ajay Rupani, Gajendra Sujediya (2016), "A Review of FPGA implementation of Internet of Things", *International Journal of Innovative Research in Computer and Communication Engineering*, Volume 4, Issue 9.

- Ajay Rupani, Deepa Saini, Gajendra Sujediya, Pawan Whig (2016), "A Review of Technology Paradigm for IOT' on FPGA", *International Journal of Advanced Research inComputerand Communication Engineering*, Volume 5, Issue 9, ISO 3297:2007 Certified.

- 3. AndreaCaputo, Giacomo Marzi, MassimilianoMatteo Pellegrini (2016), "The Internet of Things in manufacturing innovation processes: Developmentand applicationofaconceptual framework", *BusinessProcess ManagementJournal*, Volume22, Issue 2, pp. 383–402, Available fromhttps://doi.org/10.1108/BPMJ-05-2015-0072.

- A. Ruta, R. Brzoza-Woch, and K. Zieli 'nski, "On fast developmentof FPGA-based SOA services—machine vision case study," DesignAutomation for Embedded Systems, vol. 16, no. 1, pp. 45–69, 2012. DOI: 10.1007/s10617-012-9084-z. [Online]. Available: http://dx.doi.org/10.1007/s10617-012-9084-z.

- R. Brzoza-Woch, A. Ruta, and K. Zieli'nski, "Remotely reconfigurable hardware software platform with web service interface for automated video surveillance," Journal of Systems Architecture, vol. 59, no. 7, pp. 376 388, 2013. DOI: 10.1016/j.sysarc.2013.05.007. [Online].Available: http://www.sciencedirect.com/science/article/pii/S138376211300074X.

- 6. Robert Brzoza-Woch, PiotrNawrocki, "Reconfigurable FPGA-based embedded Web services as distributed computational nodes," Position Papers of the FEDCSIS. ŁO' DZ', Vol. 6, pp-159-164, 2015.

- 7. Tanesh Kumar, BishwajeetPandey, and Teerath Das, "LVCMOS 1/0 Standard and Drive Strength Based Green Design on Ultra ScaleFPGA", IEEE International conference on Green Computing, Communication.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

#### ||Volume 9, Issue 12, December 2020||

- M. Kiruba, Dr. M Jagadeeswari, "FPGA Implementation of Automatic Industrial Monitoring System", IJIRSET-International Journal of Innovative Research in Science, Engineering and Technology, Vol. 5, Issue 5, pp. – 8666-8673, May 2016.

- Liguo Qu, Xia Sun, Yourui Huang, Chaoli Tang and Liuyi Ling, "FPGA Implementation of QoS Multicast Routing Algorithm of Mine Internet of Things Perception Layer based on Ant Colony Algorithm", Advances in information Sciences and Service Sciences(AISS) Volume4, Number18, pp. – 124-131, Oct 2012. DOI: 10.4156/AISS.vol4.issue18.15.

- 10. K. Divya Krishna, Vivek Akkala, R. Bharath, P. Rajalakshmi and Abdul Mateen Mohammed, "FPGA based Preliminary CAD for Kidney on IoT Enabled Portable Ultrasound Imaging System", IEEE 16th International Conference on e-Health Networking, Applications and Services (Healthcom), pp. 257-261, 2014.

- 11. John A. Stankovic, "IEEE Research Directions for the Internet of Things", Vol. 1, No. 1, February 2014. Available: http://dx.doi.org/10.1109/JIOT.2014.2312291.

- 12. P. Nawrocki and A. Mamla, "Distributed web service repository," Computer Science, vol. 16, no. 1, pp. 55–73, 2015. doi: 10.7494/csci.2015.16.1.55. [Online]. Available: http://journals.agh.edu.pl/csci/article/view/1205.

- Ajay Rupani, Dikshant Pandey and Gajendra Sujediya, "Review and Study of FPGA Implementation of Internet of Things" IJSTE - International Journal of Science Technology & Engineering, vol. 3, issue 2, pp. - 104-107, August 2016.

- Ajay Rupani, Deepa Saini, Gajendra Sujediya, Pawan Whig, "A Review of Technology Paradigm for IOT on FPGA", IJARCCE- International Journal of Advanced Research in Computer and Communication Engineering, Vol. 5, Issue 9, pp.- 61-64, September 2016.

- 15. Cisco (2011) The Internet of Things. [Online]. Available: http://share.cisco.com/internet-of-things.html.

Impact Factor: 7.512

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com