e-ISSN: 2319-8753 | p-ISSN: 2320-6710

DIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

808

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 10, Issue 6, June 2021

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

### Impact Factor: 7.512

9940 572 462

6381 907 438

$\odot$

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

Volume 10, Issue 6, June 2021

DOI:10.15680/IJIRSET.2021.1006047

## FPGA Implementation of Complex Floating Point Vedic Multiplier with Minimum Path Delay

Aishwariya.V<sup>1</sup>, Aiswarya .AR<sup>2</sup>, Deepa.M<sup>3</sup>, Siji Sivanandan<sup>4</sup>

U.G. Student, Department of Electronics and Communication Engineering, Meenakshi Sundararajan Engineering

College, Kodambakkam, Chennai, India<sup>1,2,3</sup>

Head of the Department, Department of Electronics and Communication Engineering, Meenakshi Sundararajan

Engineering College, Kodambakkam, Chennai, India<sup>4</sup>

**ABSTRACT**: Digital media and signal processing applications are usually dominated by integer addition and multiplication. Hence, developing faster, smaller and power efficient Functional Units (FUs) is critical to implement efficient circuits. While partial carry-save adders are easily designed by splitting them into several fragments working in parallel, the design of partial carry-save multipliers is more challenging. Prior approaches have proposed several solutions based on the radix-4 recoding. This technique makes it possible to diminish the height of a multiplier by half, this being the most widespread option when designing multipliers, as only easy multiples are required. In the proposed system, design of low power 8 Bit VEDIC multiplier is being implemented using adjustable path selection routine that enable the Multiplier to save the carry path adjustable and finally combines both the result in the sum part. The proposed algorithm uses reconfigurable nature of VLSI systems. The proposed algorithm is executed in the Spartan-3E FPGA. The proposed structure utilizes low power and that would be compared in terms of power, path delay, efficiency. with array multiplier and existing multiplier.

**KEYWORDS**: Vedic mathematics, Path delay, Field Programmable Gate Array(FPGA)

#### I. INTRODUCTION

Very large-scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining millions of MOS transistors onto a single chip. The design hierarchy involves the principle of "Divide and Conquer." It is nothing but dividing the task into smaller tasks until it reaches to its simplest level. This process is most suitable because the last evolution of design has become so simple that its manufacturing becomes easier. Multipliers play an important role in today's digital signal processing and various other applications. In high performance systems such as microprocessor, DSP etc addition and multiplication of two binary numbers is fundamental and most often used arithmetic operations. Statics shows that more than 70% instructions in microprocessor and most of DSP algorithms perform addition and multiplication . So, these operation dominates the execution time. That's why, there is need of high speed multiplier. The demand of high speed processing has been increasing as a result of expanding computer and signal processing applications. Low power consumption is also an important issue in multiplier design. To reduce significant power consumption it is good to reduce the number of operation thereby reducing dynamic power which is a major part of total power consumption So the need of high speed and low power multiplier has increased.

Vedic mathematics is part of four Vedas (books of wisdom). It is part of Sthapatya- Veda (book on civil engineering and architecture), which is an upa-veda (supplement) of Atharva Veda. It covers explanation of several modern mathematical terms including arithmetic, geometry (plane, co-ordinate), trigonometry, quadratic equations, factorization and even calculus. The system is based on 16 Vedic sutras or aphorisms, which are actually word formulae describing natural ways of solving a whole range of mathematical problems. Urdhva – Triyakbhyam is the general formula applicable to all cases of multiplication and also in the division of a large number by another large number. It means vertically and crosswise.

#### II. RELATED WORK

[1] This paper presents an IEEE 754 format 32 X 32 bit complex floating point multiplier using four floating point real multipliers solution with minimum path delay. Each 32 bit real floating multiplier requires a 24 bit fixed point real multiplier for mantissa multiplication. [2] Synthesis results show that a design with a 10-stage pipeline can achieve a

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

Volume 10, Issue 6, June 2021

DOI:10.15680/IJIRSET.2021.1006047

maximum clock rate of 224 MHz and 140 MHz for 16-bit and 32-bit designs, respectively. Both designs use the lowest amount of hardware in terms of gate equivalents as compared to a complex multiplier built with regular FPGA features.[3] Decimal number system multiplication technique based on such ancient mathematics is reported in this paper. Improvement in speed was achieved through stage reduction by "NikhilamNavatascaramamDasatah (NND)" which was adopted from Vedas, during multiplication. [4] In this paper, a detailed review is made on recent applications of Vedic Mathematics in the domain of VLSI to yield novel design, efficient architecture for Squarer, Multiplier, Arithmetic unit, Cubic and divider circuits along with their crucial performance criteria.[5] The main objective of this research paper is to design architecture for finite impulse response (FIR) filter based on complex Vedic multiplier by rectifying the problems in the existing method and to improve the speed by using the common Boolean logic (CBL).[6] A dual-channel multiplier (DCM) for energy efficient second-order piecewise-polynomial function evaluation for 3-D graphics applications is presented in this paper.

The proposed algorithm uses reconfigurable nature of VLSI systems. The proposed algorithm is executed in the Spartan-3E FPGA. The proposed structure utilizes low power and that would be compared in terms of power, path delay, efficiency. with array multiplier and existing multiplier.

#### **III.METHODOLOGY**

This technique makes it possible to diminish the height of a multiplier by half, this being the most widespread option when designing multipliers, as only easy multiples are required. In the proposed system, design of low power 8 Bit VEDIC multiplier is being implemented using adjustable path selection routine that enable the Multiplier to save the carry path adjustable and finally combines both the result in the sum part.

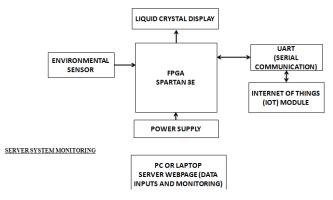

Figure 1: Block diagram for FPGA implementation of vedic multiplier

The description of each block is explained below:

- Environmental Sensor: The LM35 series are precision integrated-circuit temperature devices with an output voltage linearly-proportional to the Centigrade temperature. The LM35 device does not require any external calibration or trimming to provide typical accuracies of ±¼°C at room temperature and ±¾°C over a full -55°C to 150°C temperature range.

- 2. UART:UART board is used to receive the data from the wireless communication devices and transmit the data in to a serial format. It is provided with a DB9 female port along with a data driver. This board has a filtering unit to reduce the unwanted noise in data transmission.

- 3. IoT:Node MCU V3 is an open-source firmware and development kit that plays a vital role in designing an IoT product using a few script lines. Multiple GPIO pins on the board allow us to connect the board with other peripherals and are capable of generating PWM, I2C, SPI, and UART serial communications.

FPGA Spartan 3E: The Spartan®-3E family of Field-Programmable Gate Arrays (FPGAs) is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications. The Spartan-3E family is a superior alternative to mask

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

Volume 10, Issue 6, June 2021

DOI:10.15680/IJIRSET.2021.1006047

#### **IV. EXPERIMENTAL RESULTS**

The heat produced in the FPGA is overcome by using the heat sink component. Supplying the FPGA core voltage at the lower limit of the manufacturer's specification can save significant static power. Some FPGA vendors use a triple-oxide process technology for some transistors to reduce static power consumption of non-speed-critical configuration circuitry. Another innovation is a shift to a coarser-grained logicarchitectures employing lookup tables (LUTs) with six inputs rather than the previous standard of four. This enables tighter logic packing, reduces the number of switching transistors, and shortens routing lengths, reducing dynamic power consumption.

| Floating Point Multiplier | Jsing Minimum Path N      | lethod |     | ×                   | Floating Point Multiplie | er Using Minimum Path | Method                    | >                 |  |

|---------------------------|---------------------------|--------|-----|---------------------|--------------------------|-----------------------|---------------------------|-------------------|--|

|                           | Comm Port                 | 5      |     | Start               |                          | Comm Port             | 5                         | Start             |  |

| Temperature               | A031BA031BA031BA031BA031B |        |     | BA031BA031B         | Temperatu                | re 31                 | A031BA031BA030BA031BA031B |                   |  |

|                           |                           |        |     |                     |                          |                       |                           |                   |  |

| 83                        |                           |        |     |                     |                          |                       | 25                        |                   |  |

| Number 1                  | 24.25                     |        | i i | 94.75               | Number 1                 | 13.586                | i                         | -0.25997          |  |

| Number 2                  | 47.72                     |        | i   | 54.62               | Number 2                 | 1.5698                | i                         | 3.12546           |  |

|                           | Send                      |        |     |                     |                          | Send                  |                           |                   |  |

|                           | - <b>4018.035</b> i       |        | i   | 5846.005            |                          | 22.1398286            |                           | i 42.05439        |  |

|                           | Proposed Multiplier       | Алау   |     | Existing Multiplier |                          | Proposed Multiplier   | Алау                      | Existing Multiple |  |

| Path Delay                | 54                        | 165.04 |     | 79.51               | Path Delay               | 32                    | 165.04                    | 79.51             |  |

| Power Consumer            | d 0.455795186161:         | 0.5063 | 32  | 0.51064             | Power Consu              | ned 0.458144900202    | 0.50632                   | 0.51064           |  |

| Efficiency                | 83                        |        |     |                     | Efficiency               | 62                    |                           |                   |  |

|                           |                           |        |     |                     |                          |                       |                           |                   |  |

Figure 2: Obtained results

| Apps 🧮 SQL Commands 🧔 Cloud Comp  |              | II Readi                                                   | ing li    |             |  |

|-----------------------------------|--------------|------------------------------------------------------------|-----------|-------------|--|

| Wifi-IOTLogs 🔤                    | ₽ ≣ De       |                                                            | S Velcom  | e           |  |

| HOME                              | Show 10      | entries Si                                                 | arch      |             |  |

| 🔄 Data Log                        | LogID        | DATA                                                       | Logdate   | LogTime     |  |

| Analog Log                        | 2            | N1:1(plus)i2_N2:2(plus)i3_Out:-4(plus)i7                   | 04/05/202 | 21 19:19:18 |  |

| Digital Output                    | 66           | Num1:0.1(plus)i-0.1Num2:0.2(plus)i-0.2Output0(plus)i-0.04  | 04/05/202 | 21 19:32:47 |  |

| <ul> <li>Digital Input</li> </ul> | 124          | Num1:0.1(plus)i-0.1Num2:0.2(plus)i-0.2Output:0(plus)i-0.04 | 04/05/202 | 21 19:43:54 |  |

|                                   | 128          | Num1:1(plus)i-2Num2:3(plus)i-4Output:-5(plus)i-10          | 04/05/202 | 21 19:44:39 |  |

|                                   | 7            | Num1:1(plus)i2Num2:2(plus)i3Output:-4(plus)i7              | 04/05/202 | 21 19:20:10 |  |

|                                   | 12           | Num1:1(plus)i2Num2:3(plus)i4Output:-5(plus)i10             | 04/05/202 | 21 19:21:04 |  |

|                                   | 13           | Num1:1(plus)i2Num2:3(plus)i4Output:-5(plus)i10             | 04/05/202 | 21 19:21:17 |  |

|                                   | 113          | Num1:1(plus)i2Num2:3(plus)i4Output:-5(plus)i10             | 04/05/202 | 21 19:42:26 |  |

|                                   | 114          | Num1:1(plus)i2Num2:3(plus)i4Output:-5(plus)i10             | 04/05/202 | 21 19:42:34 |  |

|                                   | 116          | Num1:1(plus)i2Num2:3(plus)i4Output:-5(plus)i10             | 04/05/202 | 21 19:42:40 |  |

|                                   | Showing 1 to | 10 of 12 entries                                           | Previous  | 1 2 Next    |  |

Figure 3: Obtained result of IoT webpage

#### V. CONCLUSION

This project illustrates the design and implementation of the low power vedic multiplier with minimum path delay which is widely used digital signal processing applications. This project mainly focuses on the multiplier parameters such as efficiency, path delay, power consumption. It is used to determine the cost effective and efficient method which gives higher efficiency. By comparing the results, it is observed that it is more efficient than the existing multiplier. In future this multiplier can be used in many digital signal processing and wireless communication applications. Since IOT hardware is interfaced with the FPGA hardware , the multiplier will be accessible from anywhere.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 7.512|

#### Volume 10, Issue 6, June 2021

#### DOI:10.15680/IJIRSET.2021.1006047

#### REFERENCES

[1]. Akanksha Kant and Shobha Sharma (2015)," Applications of vedic multiplier designs - A review" IEEE Students' Technology Symposium, 2011, IIT Kharagpur.

[2]. Amina Naaz.S, Pradeep M.N, Satish Bhairannawar, Srinivas halvi (2014), "FPGA Implementation Of High Speed Vedic Multiplier Using CSLA For Parallel FIR Architecture", 2nd International Conference on Devices, Circuits and Systems (ICDCS).

[3]. Aravind E Vijayan, A. John and D. Sen (2014), "Efficient Implementation of 8-bit Vedic Multipliers for Image Processing Application", International Conference on Contemporary Computing and Informatics (IC3I).

[4].B. Lamba and A. Sharma (2018), "A review paper on different multipliers based on their different performance parameters," 2nd International Conference on Inventive Systems and Control (ICISC), Coimbatore, India.

[5]. Design and Implementation of 8-Bit Vedic Multiplier(2013), IJAREEIE.

[6].H.D.Tiwari, G.Gankhuyag, C.M. Kim and Y.B.Cho (2008),"Multiplier design based on ancient Indian Vedic Mathematics,"Proc. IEEE ISOCC'08, Vol.2, pp.6568.

[7].K.Deergha Rao, PP.V. Muralikrishna, Ch. Gangadhar (2018) IEEE "FPGA Implementation of 32 Bit Complex Floating Point MultiplierUsing Vedic Real Multipliers with Minimum Path Delay".5th IEEE Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON).

[8].K. Deergha Rao, Ch. Gangadhar and P. K. Korrai (2016), "FPGA implementation of complex multiplier using minimum delay Vedic real multiplier architecture," Proc.IEEEUPCON.

[9].K.Hwang,(1979) Computer Arithmetic: Principles, Architecture and Design.New York: John Wiley & Sons.

[10].M.Y. Kong., J.P Langlois, and D.Al-Khalili(2008), "Efficient FPGA implementation of complex multipliers using the logarithmic number system," Proc. IEEE ISCAS, pp. 3154-3157.

[11].Oscal T.-C. Chen, Sandy Wang, and Yi-Wen Wu (2011),"Minimization of Switching Activities of Partial Products for Designing Low-Power Multipliers" IEEE .

[12].P.Saha, A. Banerjee, P.Bhattacharyya, and A.Dandapat(2011), "High speed ASIC design of complex multiplier using vedic mathematics," Proc. IEEE Students' Technology Symposium (TechSym), pp.237-241.

Impact Factor: 7.512

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

🚺 9940 572 462 应 6381 907 438 🖂 ijirset@gmail.com

www.ijirset.com