e-ISSN: 2319-8753 | p-ISSN: 2347-6710

EDIA

#### International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 11, Issue 1, January 2022

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

## Impact Factor: 7.569

9940 572 462

$\bigcirc$

|| Volume 11, Issue 1, January 2022 ||

DOI:10.15680/IJIRSET.2022.1101117

## Survey on Distributed Arithmetic-Based LMS Adaptive Filter

Rajanikant<sup>1</sup>, Prof. Satyarth Tiwari<sup>2</sup>, Prof. Suresh. S. Gawande<sup>3</sup>

M. Tech. Scholar, Department of Electronics and Communication, Bhabha Engineering Research Institute,

Bhopal, India<sup>1</sup>

Guide, Department of Electronics and Communication, Bhabha Engineering Research Institute, Bhopal, India<sup>2</sup>

Co-guide, Department of Electronics and Communication, Bhabha Engineering Research Institute, Bhopal, India<sup>3</sup>

**ABSTRACT:-** Adaptive filters have proven to be an instrumental system component in the modern signal processing applications. Innumerable systems that we presently depend on in our daily life would not exist without the use of adaptive filters. There are two conflicting algorithms that are commonly used for implementation of adaptive filters; namely the narrow band based on multi rate approach. In addition, a computationally efficient distributed arithmetic (DA) approach may be used to implement the narrow band algorithm which may further reduce computational complexity. DA scheme employs bit-serial operations and look-up tables (LUTs) sharing and weight increment terms of multi-rate approach to implement high throughput filters. Therefore, a shared-LUT design is proposed to realize the DA computation. Instead of using separate registers to store the possible results of partial inner products for DA processing of different bit positions, registers are shared by the DA units for bit slices of different weightage.

KEYWORDS: - Finite Impulse Response (FIR), Look Up Table (LUT), Adaptive Filter, Narrow Band Filter

#### I. INTRODUCTION

Adaptive filters are extensively used in various digital signal processing applications, such as channel equalization, system identification, noise and echo cancellation, and beamforming [1]. Least-mean-square (LMS) algorithm based adaptive filters (ADFs) are usually preferred due to their computational simplicity and ease of implementation. Structurally, an LMS ADF is made up of a finite-impulse response (FIR) filter whose coefficients are updated from time to time. It basically involves several multipliers depending on the filter order [2]. The complexity of multipliers is further pronounced with an increase in the word length of coefficients and input samples. As a consequence, the implementation cost of such filters becomes significantly high. Another problem is that these filters possess longer critical paths. Pipelining is a fundamental approach to reduce the critical path, but it is difficult to pipeline the LMS ADF due to recursive loop. This has been addressed by the delayed LMS (DLMS) algorithm [3], [4]. Over the years, different DLMS ADFs have been developed [5]–[8] to reduce the number of adaptation delays and critical path. Van and Feng [5] proposed a systolic architecture with critical path of a single multiplier and adder. Yi et al. [6] suggested a fine-grained pipelined architecture for the LMS ADF. Meher and Park [7] presented three LMS ADF architectures to analyze their critical paths and hardware complexities. However, the complexity of such structures is limited by the multipliers.

The performance of digital signal processing and communication systems is generally limited by the precision of the digital input signal which is achieved at the interface between analog and digital information. Sigma-Delta modulation based analog-to digital (A/D) conversion technology is a cost effective alternative for high resolution converters which can be ultimately integrated on digital signal processor ICs. The sigma-delta modulator was first introduced in 1962; but it gained the importance in recent times after the development in digital VLSI technologies. The sigma delta A/D converters are based on digital filtering techniques; almost 90% of the die is implemented in digital circuitry which enhances the prospect of compatibility [1-3].

Conventional converters are often difficult to implement in fine line very large scale integration (VLSI) technology. By keeping these things in mind the people are going for over sampling converters, these converters make extensive use of digital signal processing. The main advantages of the sigma delta A/D converters are mentioned below.

- Higher reliability.

- Increased functionality.

- Reduced chip cost.

ijirset

| e-ISSN: 2319-8753, p-ISSN: 2347-6710| <u>www.ijirset.com</u> | Impact Factor: 7.569|

Volume 11, Issue 1, January 2022

| DOI:10.15680/IJIRSET.2022.1101117 |

Those characteristics are commonly required in the digital signal processing environment of today. Consequently, the development of digital signal processing technology in general has been an important force in the development of high precision A/D converters which can be integrated on the same die as the digital signal processor itself. Conventional high-resolution A/D converters, such as successive approximation and flash type inverters, operating at the Nyquist rate (sampling frequency approximately equal to twice the maximum frequency in the input signal); often do not make use of exceptionally high speeds achieved with a scaled VLSI technology. These Nyquist samplers require a complicated analog low pass filter (often called an anti-aliasing filter) to limit the maximum frequency input to the A/D, and sample-and hold circuitry. The high resolution can be achieved by the decimation process. Moreover, since precise component matching or laser trimming is not needed for the high-resolution sigma delta A/D converters, they are very attractive for the implementation of complex monolithic Systems that must incorporate both digital and analog functions [4].

#### **II. LITERATURE REVIEW**

**Ranendra Kumar Sarma et al.** [1], presents a novel time-shared and lookup table (LUT)-less pipelined architecture for a least-mean-square (LMS) adaptive filter (ADF). The proposed approach first employs a time-shared architecture for the pipelined LMS ADF to compute each filter partial product and coefficient increment term using a single multiplier. Critical path analysis of this architecture is carried out to determine the pipeline requirements. Next, a novel LUT-less multiplier is suggested by exploiting the symmetries between the odd-multiples. Due to the symmetries between the odd-multiples, offset terms are added using an adder tree. For higher wordlength coefficients, only a few adders are required to generate the odd-multiples, and only one offset adder tree is required. Finally, a novel super-latch is developed to pipeline the LUT-less multiplier with adaptation delays of the pipelined LMS ADF. From the implementation results, it is found that the proposed design for the 32nd-order filter occupies 60.32% less area, consumes 61.93% less power, and utilizes 58.83% less sliced LUTs and 63.28% fewer flip-flops over the best existing design.

**Subrahmanyam Mula et al. [2],** proposes robust adaptive filtering algorithms and their VLSI architectures for sparse system identification under impulsive noise. Several robust algorithms are derived by combining error nonlinear adaptive filtering algorithms with proportionate adaptation. We make a comparative study of the derived algorithms and their VLSI architectures in terms of convergence rate and hardware complexity to show that the hardware overhead is negligible for the achieved improvement in robustness.

**Shivashankar Reddy B et al. [3],** an efficient VLSI architecture for LMS adaptive filter using distributed arithmetic is presented. DA is serial bit computation. Here, two separate look up tables are used to store possible filter partial product of input sample and filter coefficients, this is followed by access and summation of entries, with the idea of the proposed design. Offset binary coding technique is used to reduce the area complexity. The multiplexed LUTs are used to access the contents to improve the performance. Using LMS algorithm all the content of memory locations of LUT are recalculated based on samples and the contents of LUTs are updated based on proposed strategy. The design is simulated in Xilinx ISE and synthesized with Spartan-6 FPGA, XC6SLX45-2CSG324.

**S. Gomathi et al. [4],** signals carry important information about the behaviour of system under study. Generally, background noises present in the environment corrupt the signal. Raw signals comprise of signal of interest with extraneous noises present in them. Thus, it is very important to remove the noises and retrieve the signal of interest. Adaptive filters play an important role in manipulation of the information present in the signal. This paper presents an effort to implement the associativity technique in the adaptive filter design. The proposed architecture is used to reduce the area of the structure. The designed architecture with RLS, Affine Projection (AP) and Kalman filters depicts improvement in SNR and VLSI implementation promises to be effective design in terms of area reduction.

**Mohd.** Tasleem Khan et al. [5], presents a new area and power efficient VLSI architecture for least-mean-square (LMS) adaptive filter using distributed arithmetic (DA). Conventionally, DA based LMS adaptive filter requires lookup tables (LUTs) for filtering and weight updating operations. The size of LUTs grows exponentially with filter order. The proposed scheme has reduced the LUT size to half by storing the offset-binary-coding (OBC) combinations of filter weights and input samples. To make the adaptive filter more area and power efficient, it is not necessary to decompose LUT into two smaller LUTs. Hence, by using the non-decomposed LUT the proposed design achieves significant savings in area and power over the best existing scheme. In addition, the proposed architecture involves comparatively lesser hardware complexity for the same LUT-size. From synthesis results, it is found that the proposed

#### International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET)

| e-ISSN: 2319-8753, p-ISSN: 2347-6710| <u>www.ijirset.com</u> | Impact Factor: 7.569|

|| Volume 11, Issue 1, January 2022 ||

#### | DOI:10.15680/IJIRSET.2022.1101117 |

design with 32nd order filter offers 19.83% less area and consumes 20.54 % less power; utilizes 16.67 % and 19.04 % less number of LUT and FF respectively over the best existing scheme.

**Basant Kumar Mohanty et al.** [6], break down the substance of query tables (LUTs) of circulated math (DA)- based square slightest mean square (BLMS) versatile channel (ADF) and in light of that we propose intra-emphasis LUT sharing to decrease its equipment assets, vitality utilization, and emphasis period. The proposed LUT streamlining plan offers a sparing of 60% LUT content for square size 8 and still higher putting something aside for bigger square sizes over the ordinary outline approach. We too introduce here the outline of an enroll based LUT grid for maximal sharing of LUT substance and full-parallel LUT-refresh task. In light of the proposed configuration approach, we have determined a DA-based design for the BLMS ADF, which is versatile for bigger piece sizes and also higher channel lengths. We find that the equipment many-sided quality of the proposed structure increments not exactly proportionately with input piece measure and channel length.

**Azadeh Safari et al. [7]**, discrete wavelet change (DWT) has demonstrated awesome execution in computerized picture pressure and denoising applications. It is the change utilized for source encoding as a part of JPEG2000 still picture pressure standard and FBI wavelet scalar quantization. DWT is fit for quick picture pressure at less region and low power utilization. This paper displays 4-tap orthogonal DWT in view of the buildup number framework. Equipment unpredictability lessening and configuration change are attained to by utilizing RNS for number-crunching operations and LUT offering between low pass and high pass channels. The RNS based DWT is reenacted and executed on the Xilinx FPGA to confirm the usefulness and effectiveness of the outline.

Yajun Zhou et al. [8], present examination paper portrays a system assessing the Field Programmable Gate Array (FPGA) assets usage for execution of computerized channels with distinctive requests. For a low pass Butterworth channel, barring its request, rest of the configuration parameters were kept steady. Channel outlining was done utilizing the numerical figuring environment programming, MATLAB. Its exceptional office producing Hardware Description Languages (HDLs) for a computerized channel item was conveyed. Diverse Very High Speed Integrated Circuit HDL (VHDL) source codes were created and executed in Xilinx FPGA gadget Spartan-3E by expanding channel request, until the gadget usage surpasses the accessible assets. Thusly, a most extreme 18th request channel was implementable in FPGA. The computerized channel reaction was shown on an Oscilloscope by method for a microcontroller, Advance RISC Machine (ARM) gadget LPC2148. The simple to advanced and computerized to simple transformation over advanced channel information was performed in a solitary ARM chip.

**V. Sudhakar et al. [9],** displays completely parallel and completely serial architectures for Band pass channel. The exhibitions of completely parallel and completely serial architectures are investigated for distinctive quantized adaptations of representation. Channels produced utilizing 8 bit settled point execution requires littler zone utilization when contrasted with 16 bit altered point usage at the expense of imprecision. The proposed executions are orchestrated with Xilinx ISE 13.2 rendition. Group of gadget was Spartan 3E and target gadget was xa3s250e-4vqgl00. The key execution measurements, to be specific number of Slices, Slice Flip Flops, LUTs, Maximum recurrence are analyzed.

Animesh Panda et al. [10], channel may be obliged to have a given recurrence reaction, or a particular reaction to a motivation, step, or incline, or recreate a simple framework. Contingent upon the reaction of the framework, computerized channels can be ordered into Finite Impulse Response (FIR) channels & Infinite Impulse Response (IIR) channels. FIR Filters can be composed utilizing recurrence examining or windowing routines. Yet these strategies have an issue in exact control of the basic frequencies. In the ideal outline system, the weighted estimate lapse between the real recurrence reaction and the sought channel reaction is spread over the pass-band and the stop-band and the greatest blunder is minimized, bringing about the pass-band and the stop-band having swells. The crest mistake can be processed utilizing a PC supported iterative methodology, known as the Remez Exchange Algorithm.

#### **III. DISTRIBUTIVE ARITHMETIC TECHNIQUE**

Distributed Arithmetic (DA) is a widely-used technique for implementing sum-of-products computations without the use of multipliers. Designers frequently use DA to build efficient Multiply-Accumulate Circuitry (MAC) for filters and other DSP applications. The main advantage of DA is its high computational efficiency. DA distributes multiply and accumulates operations across shifters; lookup tables (LUTs) and adders in such a way that conventional multipliers are not required.

Distributed arithmetic is an important algorithm for DSP applications. It is based on a bit level rearrangement of the multiply and accumulate operation to replace it with set of addition and shifting operations. The basic operations

Volume 11, Issue 1, January 2022

| DOI:10.15680/LJIRSET.2022.1101117 |

required are a sequence of table lookups, additions, subtractions and shifts of the input data sequence. The Look Up Table (LUT) stores all possible partial products over the filter coefficient space. Assuming coefficients c[n] is known constants, and then y[n] can be rewritten as follows:

$y[n] = \sum c[n] \cdot x[n] n = 0, 1, ..., N-1$ (1)  $x[n] = \sum x_{b} [n] \cdot 2^{b} \qquad b=0, 1, ..., B-1$   $x_{b}[n] \in [0, 1]$ (2)

$v = \sum c[n] \sum x_b [k] \cdot 2^b$

Where  $x_b$  [n] is the b<sup>th</sup> bit of x[n] and B is the input width. Finally, the inner product can be rewritten as follows:

(3)

$$= c[0] (x_{B-1} [0]2^{B-1} + x_{B-2} [0] 2^{B-2} + ... + x_0 [0] 2^0) + c[1] (x_{B-1} [1] 2^{B-1} + x_{B-2} [1] 2^{B-2} + ... + x_0 [1] 2^0) + ... + c[N-1] (x_{B-1}[N-1] 2^{B-1} + x_{B-2} [0] 2^{B-2} + ... + x_0 [N-1] 2^0)$$

(4)

[0] + c[1] = c\_{B-1} + c\_{B-1} = D(1) 2^{B-1} + (c\_{B-1} - c\_{B-1})

$$= (c[0] x_{B-1} [0] + c[1] x_{B-1} + ... + c[N-1] x_{B-1}[N-1]) 2^{B-1} + (c[0] x_{B-2}[0] + c[1] x_{B-2}[1] + ... + c[N-1] x_{B-2}[N-1]) 2^{B-2} + ... + (c[0] x_0[0] + c[1] x_0 [1] + ... + c[N-1] x_0[N-1]) 2^0$$

(5)

$= \Sigma 2^{b} \Sigma c[n] \cdot x_{b} [k]$

Where n=0, 1... N-1 and b=0, 1... B-1 The coefficients in most of DSP applications for the multiply accumulate operation are constants.

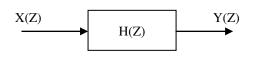

#### **IV. MULTIRATE APPROACH**

The process of converting a signal from a given rate to a different rate is called sampling rate conversion. The systems which employ multiple sampling rates in the processing of digital signal are called multi-rate signal processing [5]. Decimation is the processes of lowering the word rate of a digitally encoded signal, which is sampled at high frequencies much above the nyquist rate. It is usually carried out to increase the resolution of an oversampled signal and to remove the out-of-band noise. In a sigma-delta ADC, oversampling the analog input signal by the modulator alone does not lower the quantization noise; the ADC should employ an averaging filter, which works as a decimator to remove the noise and to achieve higher resolutions. A basic block diagrammatic representation of the decimator is shown in Figure 1. The decimator is a combination of a low pass filter and a down sampler. In Figure 1 the transfer function, H(z) is representative of performing both the operations. The output word rate of the decimator is down sampled by the factor M, where M is the oversampling ratio [6]. The function of low pass filtering and down sampling can be carried out using an averaging circuit. The transfer function of the averaging circuit is given by equation (1.1). It establishes a relation between the input and output functions (1.1)

Variable x[n] can be represented by:

|| Volume 11, Issue 1, January 2022 ||

#### | DOI:10.15680/IJIRSET.2022.1101117 |

Sampling After Decimator Frequency f<sub>s</sub> Sampling Frequency f<sub>s</sub>/M

Figure 1: Block Diagram of Decimator

$$H(Z) = \frac{X(Z)}{Y(Z)} = \frac{1}{M} \sum_{x=0}^{M-1} Z^{-x}$$

(6)

"**Up sampling**" is the process of inserting zero-valued samples between original samples to increase the sampling rate. (This is called "zero-stuffing".) Up sampling adds to the original signal undesired spectral images which are centered on multiples [7] of the original sampling rate.

"Interpolation", in the DSP sense, is the process of up-sampling followed by filtering. (The filtering removes the undesired spectral images.) As a linear process, the DSP sense of interpolation is somewhat different from the "math" sense of interpolation, but the result is conceptually similar: to create "in-between" samples from the original samples.

#### V. PROPOSED METHODOLOGY

It depends on the filter coefficients required to achieve the desired frequency response of the filter. The narrowband filter may be implemented directly or using the multi-rate method. Here we have estimated the required filter coefficients for both these methods to find the complexity of the narrow band filter.

#### • Specification of the narrowband filter:

| Sampling frequency,  | $F_s = 250Hz$        |

|----------------------|----------------------|

| Pass band ripple,    | $\delta_p = 0.08 dB$ |

| Stop band ripple,    | $\delta_s = 42 dB$   |

| Pass band frequency, | $f_p = .825Hz$       |

| Stop band frequency, | $f_{s} = 4.15 Hz$    |

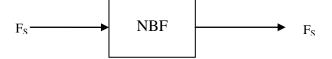

• Direct Approach

Block diagram for implementation of narrow band filter is shown in Figure 2.

Figure 2: General diagram of narrow band filter

Transition width,

$$\Delta f(normalized) freq. = \frac{f_s - f_p}{F_s}$$

(7)

Filter order N Filter order by Kaiser Formulation

|| Volume 11, Issue 1, January 2022 ||

#### DOI:10.15680/IJIRSET.2022.1101117

$$N = -20\log\sqrt{\frac{\delta_s \delta_p - 13}{14.6\Delta f}}$$

(8)

Filter order

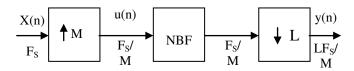

#### • Multi-rate Approach

The block diagram of multi-rate approach for implementation of narrowband filter is shown in Figure 3.

N = 150

Figure 3: Diagram of the multistage for designing level

Suppose the sampling frequency of the narrowband filter is 125 Hz.

Down sampling factor M=2, Calculation of filter order of the decimator:

Specification of decimator:

$$\Delta f(normalized) = \frac{(f_{s1} - f_p)}{F}$$

$$f_{s1} = F_s - \frac{F_s}{2M}$$

$\Delta f = .2467 Hz$

FilterOrderN1 = 9

#### **VI. CONCLUSION**

The narrowband filter is realized in FIR filter. Based on the direct approach, the filter requires 150 filter coefficients to meet the desired frequency response. To implement such a large order FIR filter in hardware involves large resources and sometime difficult to implement in resource constrained application. Keeping this in view, we have used Multirate approach to design the narrowband filter. We have used down sampling factor 2 and 4 for this purpose and found that, down sampling factor 4 requires significantly less filter constants than 2. To implement the narrowband filter, we therefore chosen down sampling factor 4 and designed the decimator, interpolator and narrowband filter.

#### REFERENCES

- [1] Ranendra Kumar Sarma, Mohd. Tasleem Khan, Rafi Ahamed Shaik and Jinti Hazarika, "A Novel Time-Shared and LUT-Less Pipelined Architecture for LMS Adaptive Filter", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 28, Issue 1, 2020.

- [2] Subrahmanyam Mula, Vinay Chakravarthi Gogineni and Anindya Sundar Dhar, "Robust Proportionate Adaptive Filter Architectures Under Impulsive Noise", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 27, Issue 5, 2019.

- [3] Shivashankar Reddy B, Gangadharaiah S L and Narayanappa C K, "FPGA based Optimized LMS Adaptive Filter using Distributed Arithmetic", 3rd IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), IEEE 2018.

- [4] S. Gomathi, G. Murugesan, S. Sasikala and M. Chitra, "Area Efficient Implementation of Adaptive Filters using High Level Transformation", International Conference on Intelligent Computing and Communication for Smart World (I2C2SW), IEEE 2018.

え う は IJIRSET e-ISSN: 2319-8753, p-ISSN: 2347-6710 www.ijirset.com | Impact Factor: 7.569

Volume 11, Issue 1, January 2022

#### DOI:10.15680/IJIRSET.2022.1101117

- [5] Mohd. Tasleem Khan, Shaik Rafi Ahamed, "Area and Power Efficient VLSI Architecture of Distributed Arithmetic Based LMS Adaptive Filter", 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), IEEE 2018.

- [6] Basant Kumar Mohanty, Pramod Kumar Meher and Sujit K. Patel, "LUT Optimization for Distributed Arithmetic-Based Block Least Mean Square Adaptive Filter", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 78, No.06, April 2016.

- [7] Azadeh Safari and Yinan Kong "Four tap Daubechies filter banks based on RNS", 978-1-4673-1157-1/12/\$31.00 © 2012 IEEE.

- [8] Yajun Zhou, Sch. of Autom., HangZhou Dianzi Univ., Hangzhou China "Distributed Arithmetic for FIR Filter implementation on FPGA" 1053-587X/\$25.00 © 2011 IEEE.

- [9] V.Sudhakar, N.S.Murthy, L.Anjaneyulu, "Fully Parallel and Fully Serial architecture for realization of high speed FIR Filters with FPGA's", IEEE June 2010 (IJSETR), Volume 3, Issue 6, ISSN: 2278 7798.

- [10] Animesh Panda, Satish Kumar Baghmar and Shailesh Kumar Agrawal, "FIR Filter Implementation on A FPGA Allowing Signed and Fraction Coefficients with Coefficients Obtained Using Remez Exchange Algorithm" Vol 1, No 2 (October 2010.

- [11] H. Ruckdeschel, H. Dutta, F. Hannig, and J. Teich, "Automatic FIR filter generation for FPGAs," in Proc. 5th Int. Workshop Systems, Ar-chitectures, Modeling, Simulation (SAMOS), T. D. H., Ed. et al., Jul. 2005, vol. LNCS 3553, pp. 51–61.

- [12] S.-S. Jeng, H.-C. Lin, and S.-M. Chang, "FPGA implementation of FIR filter using M-bit parallel distributed arithmetic," in Proc. 2006 IEEE Int. Symp. Circuits Systems (ISCAS), May 2006, p. 4.

- [13] P. K. Meher, "Hardware-efficient systolization of DA-based calculation of finite digital convolution," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 8, pp. 707–711, Aug. 2006.

- [14] D. J. Allred, H. Yoo, V. Krishnan, W. Huang, and D. V. Anderson, "LMS adaptive filters using distributed arithmetic for high throughput," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 52, no. 7, pp. 1327–1337, Jul. 2005.

- [15] H. Yoo and D. V. Anderson, "Hardware-efficient distributed arithmetic architecture for high-order digital filters," in Proc. IEEE Int. Conf. Acoustics, Speech, Signal Processing (ICASSP), Mar. 2005, vol. 5, pp. v/125– v/128.

Impact Factor: 7.569

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com