Volume 11, Issue 6, June 2022

**Impact Factor: 8.118**

6381 907 438

||Volume 11, Issue 6, June 2022||

| DOI:10.15680/IJIRSET.2022.1106135|

# Review of BCD Adder/Sub-tractor using DKG Gate for Portable System

Gopal Dubey<sup>1</sup>, Prof. Satyarth Tiwari<sup>2</sup>

M. Tech. Scholar, Department of Electronics and Communication, RKDF College of Engineering, Bhabha University, Bhopal, India<sup>1</sup>

Guide, Department of Electronics and Communication, RKDF College of Engineering, Bhabha University, Bhopal, India  $^2$

**ABSTRACT**— On this Technical era the excessive velocity and low area of VLSI chip are very-very crucial elements. Each day quantity of transistors and different active and passive elements are drastically developing on a VLSI chip. All of the processors of the gadgets adders and multipliers are playing an essential position. An adder is a pleasing element for the designing of fast multiplier. Ultimately here want a fast adder for excessive bit edition. In this paper, they review of BCD adder based on different types of adder. Offering Kogge stone adder presents much less additives, less path delay and better pace compare to different present CBL adder and different adders. Right here, we're evaluating the BCD adder of different-extraordinary word length from different adders. The design and experiment may be executed by way of the useful resource of Xilinx 14.1i Spartan device circle of relatives.

KEYWORDS: BCD Adder, CBL adder, KSA

# I. INTRODUCTION

In normal way of thinking adders are utilized to perform expansion of numbers. Adders are utilized in a few PCs and various types of processors not exclusively to perform activities in ALUs, but also in various components of the processor for address computation, signal handling applications, etc. [1]. Surmised adders, High speed adders and mistake lenient adders are the various adders utilized for signal handling applications [2]. Despite the fact that adders are intended for various mathematical arrangements, the most widely recognized adders handles ones and zeros designs.

The half viper adds two single pieces to deliver its relating yield aggregate and convey. Similarly the full snake produces two results as total and conveys by adding three single piece inputs.

In like manner a BCD snake delivers a BCD aggregate by adding the BCD inputs [3]. Accept that the two data sources are marked An and B with yield as aggregate S and convey C. On the off chance that the worth of An is 0010 in double same that is 2 in decimal organization and B is 0011 in twofold identical that is 3 in decimal arrangement, then the result aggregate S and convey C is 0101 furthermore, 0 individually in the two paired total and BCD aggregate [7]. However, when the worth of total is more than 9, 1 will set to the worth of convey set and again the aggregate worth will begin from 0000 to 1001 with convey 1 for 10 to 19 individually. The got worth of aggregate (if it surpasses 9) ought to be summarized to the worth 6, for the reason of getting the BCD code with 1 as convey.

As the VLSI was created, huge activities and different ideas were proposed in these streams. Despite the fact that VLSI advancements additionally enjoy the benefits like diminished postponement, region and power factors there are a few actual limits in the innovation of CMOS [8]. In future the idea of "Past CMOS" can start since the scaling of the present CMOS innovation can come to the fundamental cutoff. New advances are expected to settle the downside. Arising gadget innovation will conquer the scaling disadvantage inside the ongoing CMOS innovation

#### II. LITERATURE REVIEW

**Sudhanshu Janwadkar et al. [1],** have propose plan and execution of novel line viper engineering equipped for adding numerous addends in a solitary advance. The design is determined in light of expansion calculation from Shuddha arrangement of vedic math. The viper engineering is especially reasonable for a class of applications, for example, FIR channel, where numerous operands are expected to be added. The execution is especially fit for versatile

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.118|

||Volume 11, Issue 6, June 2022||

| DOI:10.15680/IJIRSET.2022.1106135|

frameworks where region and power utilization are profoundly compelled. We then quantitatively analyze proposed snake design against famous Parallel-prefix viper structures for various word lengths (N = 4, 8, 16 and 32 bits). Every one of the structures are carried out on Genesys2 board (Xilinx part number xc7k325t-2ffg900c) utilizing VHDL coding also, Xilinx Vivado 2016.2 stage. Standard execution measurements like FPGA gadget usage (number of cuts what's more, rationale LUTs), Power Consumption and Performance are considered for correlation. Results demonstrate that proposed vedic snake possesses 35.12 % lesser rationale LUTs and 28.71 % lesser cuts than some other snake structures, viable, while simultaneously, there is an improvement of 9.1 % in on-chip FPGA power utilization than any remaining snake designs. The presentation of vedic snake engineering draws lined up with that of quickest prefix viper being thought of.

Nikhil Advaith Gudala et al. [2], one of the most significant areas of exploration in VLSI is the plan of force productive and rapid information way rationale frameworks. The speed of expansion is compelled in advanced adders when taken to engender a bring through the snake. Whenever the past piece has been added and the convey produced from this option is proliferated onto the following piece, the total for each piece in a rudimentary viper is created consecutively as such. In a few PC frameworks, the Carry Select Adder (CSLA) is utilized to relieve the issue of convey spread delay by creating various convey pieces and afterward choosing a convey for the ideal result. The CSLA, in any case, isn't region proficient since it uses a few Ripple Carry Adders (RCA) sets to create incomplete aggregate and convey by thinking about convey information, and afterward multiplexers pick the last total and convey (mux). The center idea of this study is to utilize the Binary to Excess-1 Converter (BEC) to accomplish rapid and low-power utilization rather than the RCA in the normal CSLA. The outcomes have been examined and analyzed for execution of three adders (regular CSA, CSA with RCA, CSA with BEC). The outcomes from the presentation assessments of the adders are contrasted and one another. All the recreation is done in 45nm innovation. The postponement of CSA and CSA with RCA are same, yet the principle contrast is in decrease of region and power. Also when CSA(BEC) and CSA(RCA) are analyzed, the region has been decreased by around 18.67% and power has been diminished by 25.85%.

Krishna Sravani Nandam et al. [3], the CSL (Carry Select) viper is among the best adders to perform satisfactory math activities for a long time. The design of the CSL snake is important to the point that it will in general diminish region, postponement and power use. The CSL snake structure is with the end goal that the region, deferral and power utilization will be additionally limited. It can differ between the surmised and definite methods of the activity. The CSL snake region, postponement and power are decreased with fast, fruitful entryway level changes. Multiplier is utilized as a fundamental part in computerized signal handling to perform number juggling activities. The double mode can give a multiplier a productive usage, where precision can change essentially during execution. To give a more modest region and defer involving a compelling proposed snake in the multiplier with precise mode and inexact mode. The Dynamic Accuracy Configurable Multiplier is utilized conversely, with their multiplier, surmised multiplier furnishes lower delay and higher power regarding charge of humbler precision. The boundaries with the best grade approach. Aside from precise Evaluation of the 32\_Bit multiplier can be mimicked and orchestrated with the assistance of the Square-Root (SQRT) CSL viper in XILINXISE. Utilizing 4:2 blowers, the boundary result demonstrates lower delay, higher power utilization and high velocity.

Muteen Munawar et al. [4], as the computerized electronic frameworks are getting better with the progression in innovation step by step; there is a need to assemble quicker and more power-effective multipliers, which are the significant structure block in a large portion of the advanced handling frameworks. Dadda tree multiplier is one of the successful multipliers consuming low power and very quicker than different multipliers for example Vedic, Wallace and corner redix4 multiplier. In this paper, we have planned a Dadda tree multiplier with convey select snake followed by paired to abundance 1 converter which makes it a lot quicker and power productive. The outcomes for this multiplier are similarly better thinking about other existing multipliers.

**Priyadharshni et al. [5],** estimated figuring based number juggling units are situated towards decrease in power, deferral, and region. Natural mistake resilience capacity of arising application areas, similar to interactive media, Internet of Things (IoT), and picture handling gives better open doors to improvement of surmised math units. In this paper, a clever 1-bit uncertain full snake (IFA) is proposed with less entryway count. Likewise, two renditions of 16-cycle blunder lenient adders (ETAs), to be specific a low power and region proficient mistake open minded viper (LETA) and worked on low power and region effective mistake open minded snake (ILETA), are proposed. In these

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.118|

||Volume 11, Issue 6, June 2022||

| DOI:10.15680/IJIRSET.2022.1106135|

proposed ETAs, the main piece (MSB) fragments are acknowledged in same methodology, while the most un-critical piece (LSB) portion of LETA and ILETA are acknowledged utilizing a current adjusted full snake (MFA) and proposed IFAs, separately. The proposed and existing ETA adders are carried out utilizing a Verilog equipment depiction language (HDL) and blended in a Synopsys electronic plan robotization (EDA) Tool utilizing Taiwan Semiconductor Manufacturing Company (TSMC) 65nm innovation. The proposed (ILETA, LETA) adders display (55%, half) decrease in power utilization and accomplish huge decrease in region (68%, 61%). Further, in this work, another presentation metric to be specific power and mistake item (PEP) is proposed to assess the surmised adders concerning power and blunder measurements.

Maytham Allahi et al. [6], another convey select viper (CSLA) engineering is proposed with a lower region and a higher speed contrasted with past CSLAs. The proposed CSLA is a low-region and rapid plan using another add-one circuit that is utilized rather than the subsequent wave convey viper (RCA) with the information convey equivalent to one (C in =1) inside each gathering of the fundamental CSLA. Also, to facilitate the add activity, another gathering structure is proposed rather than the essential square-root (SQRT) gathering as well as using a quicker RCA in each gathering. In spite of the way that the proposed CSLA has not accomplished the least power utilization among all current plans in light of the PDK 45nm standard cell library, however it has accomplished the most reduced region and postponement contrasted with past CSLAs. Execution results show that 8 to 33% region decrease and 12 to 44% speed improvement are accomplished in the proposed CSLA contrasted with past plans.

**N. M. Hossain et al.** [7], various sorts of processors and other computerized circuits adders are generally broadly utilized. Low power and region proficient fast circuits are most significant region in the examination of VLSI plan. The convey select snake is one of the quick adders which has less region and decreased power utilization. In this paper, a 16-cycle convey select snake has been introduced utilizing altered XOR based full viper to diminish circuit intricacy, region and deferral. The adjusted full viper configuration requires just two XOR entryways and one multiplexer. The adjusted 16-bit convey select viper gives preferred outcome over customary convey select snake as for region, power utilization and postponement.

**Bavithra et al. [8],** propose four 4:2 blowers, which have the adaptability of exchanging between the specific and rough working modes. In the rough mode, these double quality blowers give higher paces and lower power utilizations at the expense of lower exactness. Every one of these blowers has its own degree of precision in the rough mode as well as various postponements and power dispersals in the estimated and accurate modes. Involving these blowers in the designs of equal multipliers gives configurable multipliers whose exactnesses (as well as their powers and rates) may change powerfully during the runtime. The efficiencies of these blowers in a 32-cycle Dadda multiplier are assessed in a 45-nm standard CMOS innovation by contrasting their boundaries and those of the cutting edge estimated multipliers. All things considered, 46% and 68% lower postponement and power utilization in the rough mode. Likewise, the viability of these blowers is evaluated in some picture handling applications.

**Shah et al. [9],** portrays the plan of fast Vedic multiplier that utilizes the procedures of Vedic math in view of 16 sutras (calculations) to work on the presentation. In this paper the productivity of Urdhva Tiryagbhyam (vertical and transversely) Vedic technique for augmentation which is not quite the same as the course of typical duplication is introduced. Urdhva-Tiryagbhyam is the most effective calculation that gives least deferral for duplication for a wide range of numbers independent of their size. Vedic multiplier is coded in Verilog HDL and animated and incorporated by utilizing XILINX programming 12.2 on Spartan 3E pack. Further the plan of exhibit multiplier is contrasted and the proposed multiplier as far as deferral, memory and power utilization.

**Deepti Gautam et al. [10],** new VLSI calculation for a DHT that can be effectively executed on an exceptionally secluded and equal VLSI engineering having a normal construction is introduced. The simultaneous execution of the DHT calculation can be accomplished by parting on a few equal parts proficiently. What's more, the equipment intricacy can be fundamentally decreased utilizing sub articulation sharing procedure of the proposed calculation in exceptionally equal VLSI execution. With productive sharing of multipliers having similar steady and utilizing the benefits of the proposed calculation, the quantities of multipliers and adders utilized has been essentially diminished and is kept at least contrasted and that of the current calculations. Productive execution of multipliers with a consistent is conceivable in VLSI. Computerized picture handling is the utilization of PC calculations to perform picture handling on advanced pictures. The fundamental activity performed by a straightforward advanced camera is to change the light

||Volume 11, Issue 6, June 2022||

#### DOI:10.15680/IJIRSET.2022.1106135

energy over to electrical energy, then, at that point, the energy is changed over to computerized design and a pressure calculation is utilized to diminish memory prerequisite for putting away the picture. In this venture, picture pressure has been taken as an application to demonstrate the usefulness of DHT calculation in the field of advanced signal handling.

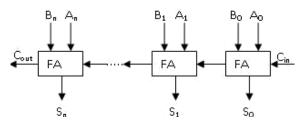

#### III. DIFFERENT TYPES OF ADDER

Ripple carry is a combinational circuit for adding greater than two bit records. It's also known as parallel adder. Ripple carry adder can be designed with the aid of the use of complete adder in cascading shape. Convey output of first full adder is hooked up with enter of the subsequent full adder, so bring is rippled from one adder to some other adder. This is by way of it is referred to as ripple-bring adder. Let us take example, for designing n bit RCA inputs are  $(A_n \dots A_3, A_2, A_1, A_0)$  and  $(B_n \dots B_3, B_2, B_1, B_0)$  then carry bits  $(C_n \dots C_3, C_2, C_1)$  and summation bits  $\operatorname{are}(C_{out} \dots S_2, S_2, S_1, S_0)$ . In this figure all the full adders are connected in cascading form. Bring enter is a further enter which has fixed price. First complete adder gives the convey output and summation output. Convey output of the primary complete adder is hooked up with 2nd cascading complete adder so that you can be taken into consideration as an enter bit.

$$S_0 = (A_0 \oplus B_0) \oplus C_{in} \tag{1}$$

$$S_1 = (A_1 \oplus B_1) \oplus C_1 \tag{2}$$

$$C_{out} = (A_n, B_n) + (C_n, B_n) + (A_n, C_n)$$

(3)

Fig 1: An n-bit Ripple Carry Adder bit binary addition

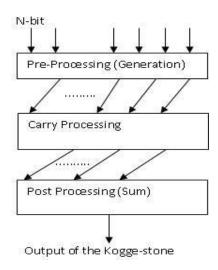

# Kogge Stone Adder

Kogge Stone Adder changed into proposed by using Peter M. Kogge and Harold S. Stone. Kogge Stone Adder is a complicated generation of look a- head conveys Adder. That is also known as parallel prefix adder. It has more area than to Brent Kung Adder however less Fan-out. This adder affords the deliver sign time and turn out to be quickest adder for commercial level.

First block of KSA is Pre- Processing a good way to generate and propagate the convey. Processing of deliver may be carried out over the convey processing place and all the bring sign go through the publish processing block. Inside the pre preprocessing level we find the, generate and propagate alerts from every inputs.

$$P_n = A_n \oplus B_n \tag{4}$$

$$G_n = A_n \cdot B_n \tag{5}$$

||Volume 11, Issue 6, June 2022||

#### | DOI:10.15680/IJIRSET.2022.1106135|

Fig 2: A Block Structure of Kogge Stone

Carry processing stage provides the carries corresponding to each bit. Execution of these bit operation is carried out from parallel. After finding the carries in parallel they are segmented in to smaller pieces.

$$CP_{n-1} = P_{n-1} \oplus P_n$$

(6)

$CG_{n-1} = (P_n \oplus G_{n-1}) + G_n$  (7)

Bottom block is summation block which provides the summation bits. That blocks are comprised with XOR gate. If one input isn't the same as any other then output will be excessive. And if inputs are identical then outputs can be low. Kogge Stone presents the less region than to other parallel adder like deliver choose adder, convey keep adder and appearance in advance adder.

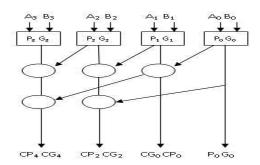

Fig. 3: A Functional Diagram of Kogge Stone Adder

Above diagram is a functional diagram of Kogge Stone adder for 4 bit addition. Here elliptically symbol defined as a carry processing stage. The output of the preprocessing stage is fed to next carry stage and post processing as well.

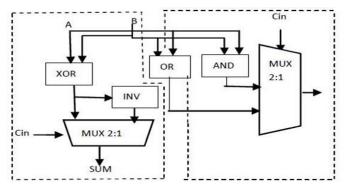

# • Modified Common Boolean Logic Adder

Area and power efficient excessive speed facts logic path are the most enormous regions of studies. With the help of simple change in gate level we will obtain the development inside the effects. velocity of the adder depends on the time required to propagate the bring thru the adder, those adder works in series layout, this is the sum of the primary position bit is calculated while the preceding bits are summed and the convey is propagated to that subsequent level.

Carry select adder (CSLA) is one of the superior adders used in information processing processors to perform fast arithmetic function. It specializes in the hassle of bring propagation put off through producing the deliver independently at each degree and the pick out the efficient one with the assist of multiplexer to perform the sum. The traditional

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.118|

||Volume 11, Issue 6, June 2022||

#### | DOI:10.15680/LJIRSET.2022.1106135|

CLSA is RCA (Ripple carry adder) which generate the partial sum and carry by way of the use of the enter deliver circumstance Cin=zero and Cin=1, select one out of each pair to shape final sum and final convey output.

RCA isn't location efficient as huge wide variety of gates circuitry is used to form the partial merchandise after which the final sum and convey is selected.

Another shape of CLSA adder makes use of binary to excess-1 convertor changing ripple deliver adder with Cin=1. This adder is known as CLSA at the side of BEC. The range of gates used has been reduced while we must layout big bit adder. This adders is more conventional as examine to RCA while cope with silicon vicinity used however that is having marginally higher put off time.

The proposed not unusual Boolean logic (CBL) adder is place-power-put off efficient. It paintings on the good judgment to get rid of the redundant adders and use commonplace Boolean common sense as examine to standard deliver pick adder.

The CBL block is constructed from two components sum technology block and carry era block. In sum generation block the output sum is completed using the multiplex. This multiplex is used to choose the output cost depending at the value of Cin( previous bit).

If Cin=0, then output is xor of the two enter bits. If Cin=1, then output get inverted. In deliver generation block, multiplexer is used to pick out the delivery of next degree relying upon the previous carry enter. If Cin=0, cout is OR of two input and if Cin=1 the output deliver is AND of the input bit.

Fig. 4: Block Diagram of CBL

If

$$C_{in} = 0$$

$Sum = A \ XOR \ B$

$Carry \ A \ OR \ B$

$else$

$Sum = NOT \ (A \ XOR \ B)$

$Carry = A \ AND \ B$

This same process is used for the n number of bits and thus we get the final sum and carry as output.

# **DKG Gate:**

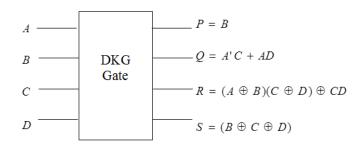

The N-bit Adder/ Sub tractor utilizes the DKG gate and DKG gate to produce two logical calculations: Adder and Sub tractor. DKG is a 4×4 reversible gate whose block diagram is shown in figure 5. Having inputs (A, B, C, D) and output

$$P = B$$

$$Q = A'C + AD$$

$$R = (A \oplus B)(C \oplus D) \oplus CD$$

$$S = B \oplus C \oplus D$$

||Volume 11, Issue 6, June 2022||

#### DOI:10.15680/IJIRSET.2022.1106135

Figure 5: Block Diagram of DKG Gate

#### IV. CONCLUSION

The plan of 32-bit BCD include subtract unit have been actualized utilizing reversible rationale entryways. Modules such as 4-bit BCD expansion, blunder adjustment unit, (4x1) MUX, contingent explanations, 4-bit nine's supplement unit have been outlined utilizing the reversible rationale doors. BCD number juggling units are rapid control with decreased territory. The four piece BCD option is composed in the CPA mold to additionally upgrade the speed of 32-bit BCD math outline for include subtract units. 32-bit subtraction unit have been planned utilizing 4-bit nine"s supplement and 4-bit BCD expansion unit. The proposed module will has extensive variety of utilization in advanced flag preparing.

#### REFRENCES

- [1] Sudhanshu Janwadkar and Rasika Dhavse, "Implementation and Performance Evaluation of Novel Line Adder Architecture for Portable Systems", IEEE Region Conference (TENCON), IEEE 2020.

- [2] Nikhil Advaith Gudala, Trond Ytterdal, John J. Lee and Maher Rizkalla, "Implementation of High Speed and Low Power Carry Select Adder with BEC", IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), 2021.

- [3] Krishna Sravani Nandam, K. Jamal, Anil Kumar Budati, Kiran Mannem, Manchalla. O. V. P. Kumar, "Design of Multiplier with Dual Mode Based Approximate Full Adder", 5th International Conference on Communication and Electronics Systems (ICCES), IEEE 2020.

- [4] Muteen Munawar, Talha Khan, Muhammad Rehman, Zain Shabbir, Kamran Daniel, Ahmed Sheraz and Muhammad Omer, "Low Power and High Speed Dadda Multiplier using Carry Select Adder with Binary to Excess-1 Converter", International Conference on Emerging Trends in Smart Technologies (ICETST), IEEE 2020.

- [5] Priyadharshni, M. and Kumaravel, S., "Low power and area efficient error tolerant adder for image processing application", International Journal of Circuit Theory and Applications 48(5), 696–708, 2020.

- [6] Maytham Allahi Roodposhti, Mojtaba Valinataj, "A Novel Area-Delay Efficient Carry Select Adder Based on New Add-one Circuit", 9th International Conference on Computer and Knowledge Engineering (ICCKE), IEEE 2019.

- [7] N. M. Hossain and M. A. Abedin, "Implementation of an XOR Based 16-bit Carry Select Adder for Area, Delay and Power Minimization", International Conference on Electrical, Computer and Communication Engineering (ECCE), IEEE 2019.

- [8] Bavithra, K. and Kumar, R. S., 'High throughput k best mimo detector using modified final selector based carry select adder', Microprocessors and Microsystems 71, 102847, 2019.

- [9] Shah, S. and Rajula, S., "Design of fir filter architecture for fixed and reconfigurable applications using highly efficient carry select adder", in 'Soft Computing and Signal Processing', Springer, pp. 627–637, 2019.

- [10] Deepti Gautam and Anshuman Singh, "Implementation of DHT Algorithm for a VLSI Architecture" Journal of Basic and Applied Engineering Research, Volume 5, Issue 7; October-December, 2018.

- [11] Low Power Approximate Adders for General Computing Using Differential Transmission Gate" on National Conference on Innovations in Communication and Computing NCICC" 18 SNS College of Technology, 2018.

- [12] Omid Akbari, Mehdi Kamal, Ali Afzali-Kusha, and Massoud Pedram, "Dual-Quality 4:2 Compressors for Utilizing in Dynamic Accuracy Configurable Multipliers", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 34, Issue 7, 2017.

| e-ISSN: 2319-8753, p-ISSN: 2320-6710| <u>www.ijirset.com</u> | Impact Factor: 8.118|

||Volume 11, Issue 6, June 2022||

# DOI:10.15680/IJIRSET.2022.1106135

- [13] G. Challa Ram and D.Sudha Rani, "Area Efficient Modified Vedic Multiplier", International Conference on Circuit, Power and Computing Technologies (ICCPCT), 2016.

- [14] G. Gokhale and P. D. Bahirgonde, "Design of Vedic Multiplier using Area-Efficient Carry Select Adder", 4th IEEE International Conference on Advances in Computing, Communications and Informatics (ICACCI-2015), Kochi, August10-13, 2015, India.

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

📵 9940 572 462 🔯 6381 907 438 🔀 ijirset@gmail.com