e-ISSN: 2319-8753 | p-ISSN: 2347-6710

EDIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 11, Issue 3, March 2022

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

## Impact Factor: 7.569

9940 572 462

6381 907 438

$\bigcirc$

|| Volume 11, Issue 3, March 2022 ||

DOI:10.15680/IJIRSET.2022.1102066

### Design and Implementation of a Single Switch Z – Source DC-DC Converter

#### S.Aafrin

Assistant Professor, Dept. of EEE, Grace College of Engineering, Tuticorin, India

**ABSTRACT:** A single switch Z-source dc-dc converter is proposed in this paper. When compared to the conventional Z- source dc-dc converter, the proposed converter can provide high voltage gain and low voltage stress of switch and the impedance network capacitor and also operates with wide range of load. The proposed Z-source dc-dc converter not only has lower cost but also has lesser weight and size. The operating principle and parameter design is explained.

KEYWORDS: Converter circuit, Pulse Width Modulation, Renewable energy systems, Z-source converter.

#### **I.INTRODUCTION**

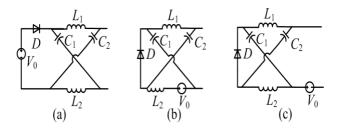

The single switch Z-source impedance network was firstly proposed by F. Z. Peng in 2002 [1]. Applying this impedance network into the circuit makes it obtain buck-boost conversion ability and high reliability [2-7]. Therefore, the Z-source inverter is very suitable for the renewable energy systems which are usually required to convert the low dc input voltage to the high dc output voltage, such as fuel-cell and photovoltaic. As mentioned in [10], both the improved Z - Source and Quasi Z - Source are derived from the traditional Z - Source . Considering the voltage-fed type as an example, Figure 1(a) shows the connection way between the original X-shape Z-source network and the voltage source. By shifting the position of the voltage source, the input part of the Quasi Z - Source and improved Z - Source are shown in Figure 1(b) and Figure 1(c) respectively. In Figure 1(a), the original X-shape Z-source network is actually a two-port impedance network. While in Figure 1(c), the combination of diode D with the X-shape Z- source network can be regarded as a one-port impedance network.

Figure 1. (a) traditional Z-source inverter; (b) quasi-Z-source inverter and (c) improved Z-source inverter.

#### **II.PROPOSED WORK**

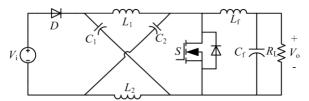

The impedance network as in the inverter is applicable for other three types of power converters too, i.e. dc-dc, ac-ac and ac-dc converters. As this insertion makes the converter achieve high voltage gain, a series of Z-source and quasi-Z-source dc-dc converters have been proposed in [11], and a traditional Z-source dc-dc converter is shown in Figure 2 [12]. However, high capacitor voltage stress, poor load capacity or high switch voltage stress are the drawbacks of Z-source dc-dc converters. Therefore, as referred to the improved Z-source inverter in [8], a modified Z-source dc-dc converter based on one-port impedance network as seen in Figure 1(c) is proposed. As shown in Figure 3, the proposed converter has lower switch and capacitor voltage stress and wide load-range compared with the traditional Z- source dc-dc converter in [12]. The circuit analysis, voltage relationship and parameter design of the proposed converter are explained. Simulation and experimental results are provided to verify the validity of the proposed converter.

|| Volume 11, Issue 3, March 2022 ||

#### DOI:10.15680/IJIRSET.2022.1102066

Figure 2. Traditional Z-source dc-dc converter

Figure 3. Proposed single switch Z-source dc-dc converter

It can be seen from Figure 3 that the proposed Z-source dc-dc converter consists of an input voltage source  $V_i$ , an oneport impedance network, a diode  $D_2$ , a switch S, an output filter capacitor  $C_f$  and a load  $R_L$ . The network consists of two identical capacitors ( $C_1$ ,  $C_2$ ), one diode  $D_1$  and two identical inductors ( $L_1$ ,  $L_2$ ). The network is in series with the input voltage source, thus the input voltage can share the common ground with the output.

Before the circuit analysis, the following assumptions are made.

- 1. All components are ideal;

- 2. The converter is operating in the continuous conduction mode (CCM);

- 3. The control strategy of switch *S* is Pulse-Width-Modulation (PWM).

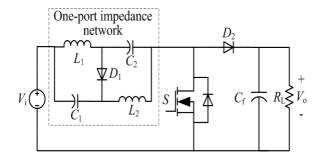

The switching period is denoted by  $T_s$  and duty ratio of switch S by d. According to the on-off state of switch S and diodes  $D_1$ ,  $D_2$ , the proposed converter has three operating modes in a switching period, which are shown in Figure 4.  $v_s$  is the drain to source voltage of switch S;  $V_o$  is the output voltage;  $i_i$  is the input source current;  $i_{D1}$  and  $i_{D2}$  are currents of diodes  $D_1$  and  $D_2$ , respectively.

Due to the symmetry of the network ( $C_1=C_2$ ,  $L_1=L_2$ ), the following equations can be established.

$$\begin{cases} i_{L1} = i_{L2} = i_L \\ i_{C1} = i_{C2} = i_C \end{cases}$$

(1)

|| Volume 11, Issue 3, March 2022 ||

#### DOI:10.15680/IJIRSET.2022.1102066

Figure 4. Three operating modes of proposed converter. Figure 5. Key waveforms of proposed converter.

| $\int v_{L1} = v_{L2} =$ | $= v_L$ | (2) |

|--------------------------|---------|-----|

| $v_{C1} = v_{C2} =$      | $= v_c$ | (-) |

where  $v_L$  and  $i_L$  are the voltage and current of the one-port impedance inductor;  $v_C$  and  $i_C$  are the voltage and current of the one-port impedance capacitor.

[Mode 1] Switch S is on and diodes  $D_1$ ,  $D_2$  are off. From Figure 4(a), there are two voltage loops in the converter, where inductor  $L_1$  is charged by input voltage  $V_i$  and capacitor  $C_2$ ,  $L_2$  is charged by input voltage  $V_i$  and capacitor  $C_1$ . Thus, the inductor current  $i_L$  is increasing linearly and the following equations can be derived.

| $\begin{cases} i_L = -i_C \\ i_I = 2i_L \end{cases}$ | (3) |

|------------------------------------------------------|-----|

| $v_L = V_i + v_C$                                    | (4) |

| $v_s = V_i + 2v_c$                                   | (5) |

In addition, the load  $R_L$  is supplied by capacitor  $C_f$ . The key waveforms of this mode are shown in the interval  $[t_0, t_1]$  in Figure 5. This mode is end when switch S is turned off and the duration time is  $dT_s$ .

[Mode 2] As shown in Figure 4(b), switch S is turned off and diode  $D_1$  is forward biased. The following equations are established.

|| Volume 11, Issue 3, March 2022 ||

#### DOI:10.15680/IJIRSET.2022.1102066

| $\begin{cases} i_L = -i_C \\ i_{D1} = 2i_L \end{cases}$ | (6) |

|---------------------------------------------------------|-----|

| $v_L = -v_C$                                            | (7) |

| $v_s = V_i + 2v_c$                                      | (8) |

The capacitors  $C_1$  and  $C_2$  are charged from inductors  $L_1$  and  $L_2$ , respectively. Then the inductor current  $i_L$  is decreasing linearly. The corresponding waveforms of this mode are shown in interval  $[t_1, t_2]$  in Fig. 5. However, voltage  $v_S$  is smaller than the output voltage  $V_0$ , thus diode  $D_2$  is off. Due to the input voltage source is in series with the one-port impedance network, the input current  $i_i$  equals to zero. It is equivalent that the one-port impedance network is isolated from both the voltage source and the load. Once the voltage  $v_S$  increases to be greater than  $V_0$ , diode  $D_2$  will conduct and mode 2 will be end.

[Mode 3] Switch S is still in off state, but both diodes  $D_1$  and  $D_2$  are on, as shown in Figure 4(c). Thus, equation (7) is still established and the following equations are derived.

$$\begin{cases} i_{i} = i_{L} - i_{C} \\ i_{D1} = 2i_{L} - i_{i} \end{cases}$$

(9)

$$V_{o} = v_{S} = V_{i} + 2v_{C}$$

(10)

Therefore, the one-port impedance network inductors not only charge the capacitors  $(C_1, C_2)$ , but also supply the output capacitor  $C_f$  and load  $R_L$  with the input voltage source  $V_i$ . The inductor current  $i_L$  is still decreasing linearly. The corresponding waveforms of this mode are shown in interval  $[t_2, t_3]$  in Figure 5. Mode 3 is end when switch S is turned on again in the following switching period. Thus, the duration time of modes 2 and 3 is  $(1-d)T_s$ .

#### **III. VOLTAGE RELATIONSHIP**

Due to the large capacitance of capacitor and the high switching frequency, the capacitor voltage  $v_C$  can be assumed to be a constant value  $V_C$ . According to the operating principle of the proposed converter, the inductor voltage  $v_L$  equals to  $V_i+V_C$  when switch S is on and equals to  $-V_C$  when switch S is off. Applying the volt-second balance for the inductor, we have

$$(V_i + V_C)dT_s + (-V_C)(1 - d)T_s = 0$$

(11)

|| Volume 11, Issue 3, March 2022 ||

DOI:10.15680/IJIRSET.2022.1102066

Then,

$$V_c = \frac{d}{1 - 2d} V_i \tag{12}$$

Combining (12) with (10), the voltage gain G of the proposed converter can be derived as

$$G = \frac{V_o}{V_i} = \frac{1}{1 - 2d}$$

(13)

Denote  $V_s$  as the drain to source voltage of switch S when switch S is off. Then, the following equation can be obtained.

$$V_{s} = V_{o} = \frac{1}{1 - 2d} V$$

(14)

From (12), (13) and (14), it is found that the operating range of the duty cycle d is from 0 to 0.5.

A comparison between the proposed converter and the traditional Z-source dc-dc converter in [12] has been presented in Tab. I. It can be found that the proposed converter has higher voltage gain than the traditional one under the same duty ratio d, lower capacitor and switch voltage stress than the traditional one under the same output voltage  $V_o$ . Therefore, the cost and size of the proposed Z-source dc-dc converter has been largely reduced.

#### Tabulation I. Comparison between the proposed converter and the traditional Zsource dc-dc converter:

| Voltage | Proposed Z-source dc-dc<br>converter | Traditional Z-source dc-dc<br>converter |

|---------|--------------------------------------|-----------------------------------------|

| Vo      | $\frac{1}{1-2d}V_i$                  | $\frac{1-d}{1-2d}V_i$                   |

| Vc      | $\frac{d}{1-2d}V_i = dV_o$           | $\frac{1-d}{1-2d}V_i = V_o$             |

| Vs      | $\frac{1}{1-2d}V_i = V_o$            | $\frac{1}{1-2d}V_i = \frac{1}{1-d}V_o$  |

Volume 11, Issue 3, March 2022

DOI:10.15680/LJIRSET.2022.1102066

#### V. SIMULATION RESULT

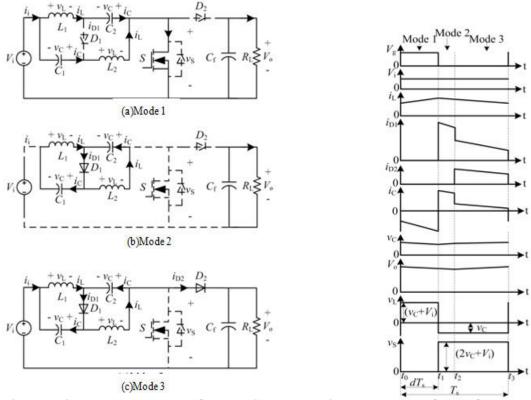

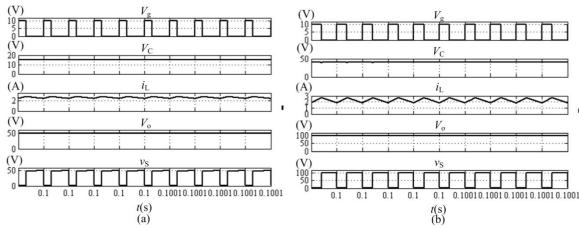

The proposed converter is verified by MATLAB/Simulink. The simulation parameters are:  $V_{c}=20V$ , d=0.3,  $f_{c}=100$ kHz, the rated output power  $P_{out}=50W$  and  $R_{L}=50\Omega$ . The capacitor voltage  $V_{c}=15V$  based on (12), the output voltage  $V_{c}=50V$  based on (13). Set  $\chi_{L}\%=15\%$ , the minimum inductance  $L_{min}=280\mu$ H is derived based on (19). Set  $\chi_{C}\%=1\%$ , the minimum capacitance  $C_{min}=50\mu$ F is derived based on (25). Therefore, inductance  $L=280\mu$ H and capacitance  $C=100\mu$ F are selected in simulation. The output capacitance  $C_{f}$  is  $100\mu$ F as well.

The simulation result is shown in Figure 7(a). As can be seen that the capacitor voltage  $V_c$  is about 15V, output voltage  $V_g$  is about 50V and switch voltage  $V_s$  is about 50V, which are accord with the theoretical value.

By changing the duty ratio d to 0.4 and load  $R_{\rm L}$  to 300 $\Omega$  while the other parameters are unchanged. Based on (22), the proposed converter will still operate in CCM. The corresponding simulation result is shown in Figure 7(b). It is obviously that the inductor current  $i_{\rm L}$  is continuous; the voltage  $V_{\rm C}$  is about 40V, voltage  $V_0$  is about 100V and voltage  $V_{\rm S}$  is about 100V which are agree with the theoretical analysis as well.

Figure 7. Simulation results of the proposed converter: (a) d=0.3,  $R_L=50\Omega$ , (b) d=0.4,  $R_L=300\Omega$ .

#### VI. CONCLUSION

A single switch Z-source dc-dc converter is proposed in this paper. The circuit analysis, parameter design and load capacity of the proposed converter have been illustrated in detail. The validity of the proposed converter has been verified by simulation. It can be concluded that the proposed single switch Z-source dc-dc converter can obtain high voltage gain with lower voltage stresses of switch and the impedance network capacitor. Moreover, it has the advantages of wide-range load, low cost and high power density. Therefore, the proposed Z-source dc-dc converter is suitable for the renewable energy systems which needs a high voltage gain converter to boost their low input dc voltage.

#### REFERENCES

- 1. F.Z. Peng, "Z-source inverter," IEEE Trans. Ind. Appl, vol. 39, no. 2, pp. 504-510, Mar./Apr.2003.

- 2. M. Shen and F. Z. Peng, "Operation Modes and Characteristics of the Z-source Inverter with Small Inductance or Low Power Factor," IEEE Trans. Ind. Electron, vol. 55, no. 1, pp. 89-96, Jan. 2008.

- 3. M. Shen, J, Wang, A. Joseph, F. Z. Peng, L. M. Tolbert, and D. J. Adams, "Constant Boost Control of the Z-source Inverter to Minimize Current Ripple and Voltage Stress," IEEE Trans. Ind. Appl, vol. 42, no. 3, pp. 770-777,

|| Volume 11, Issue 3, March 2022 ||

DOI:10.15680/IJIRSET.2022.1102066

May/Jun, 2006.

- 4. F. Z. Peng, M. Shen, and K. Holland, "Application of Z-source Inverter for Traction Drive of Fuel Cell- battery Hybrid Electric Vehicles," IEEE Trans. Power Electron, vol. 22, no. 3, pp. 1054-1061, May 2007.

- J. B. Liu, J. G. Hu, and L. Y. Xu, "Dynamic Modeling and Analysis of Z-source Converter-derivation of AC Small Signal Model and Design-oriented Analysis," IEEE Trans. Power Electron, vol. 22, no.5, pp. 1786-1796, Sep. 2007.

- 6. F. Z Peng., M. Shen and Z. M. Qian, "Maximum Boost Control of the Z-source Inverter," IEEE Trans. Power Electron., vol. 20, no. 4, pp. 833-838, Jul./Aug. 2005.

- 7. P. C. Loh, D. M. Vilathgamuwa, Y. S. Lai, G. T. Chua, and Y. W. Li, "Pulse-Width Modulation of Z-source Inverters," in Rec., 39th IAS Annual. Meeting, 2004, pp. 148-155.

- 8. Y. Tang, S. J. Xie, C. H. Zhang and Z. G. Xu, "Improved Z-Source Inverter with Reduced Z-Source Capacitor Voltage Stress and Soft-start Capability," IEEE Trans. Power Electron, vol. 24, no. 2, pp. 409-415, Feb. 2009.

- 9. Y. Li, S. Jiang, J. G. Cintron-Rivera and F. Z. Peng, "Modeling and Control of Quasi-Z-Source Inverter for Distributed Generation Applications," IEEE Trans. Ind. Electron., vol. 60, no. 4, pp. 1532-1541, Apr. 2013.

- 10. D. Li, F. Gao, P. C. Loh, M. Zhu, and F. Blaabjerg, "Hybrid-source Impedance Networks: Layouts and Generalized Cascading Concepts," IEEE Trans. Power Electron., vol. 26, no. 7, pp. 2028-2040, Jul. 2011.

- 11. D. Cao and F. Z. Peng, "A family of Z-source and Quasi-Z-source dc-dc converter", in Proc. IEEE Applied Power Electronics Conf 2009, pp. 1097-1101, Feb. 2009.

- 12. V. P. Galigekere and Marian K. Kazimierczuk, "Analysis of PWM Z-source dc-dc converter in CCM for steady state", IEEE Trans. Circuits and Syst. Regul. Pap., vol. 59, no. 4, pp. 854-863, Apr., 2012.

Impact Factor: 7.569

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com