e-ISSN: 2319-8753 | p-ISSN: 2347-6710

EDIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 11, Special Issue 1, April 2022

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

## Impact Factor: 8.118

9940 572 462

6381 907 438

$\bigcirc$

International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 9<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22)

28 <sup>th</sup> -29 <sup>th</sup> April 2022

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

## Optimized Fault-tolerant 3-Dimensional DN System with Efficient NoC Architecture

Dr R Poovendran<sup>1</sup>, S Aswini<sup>2</sup>, M Indrani<sup>3</sup>, M Keerthana<sup>4</sup>

U.G. Student, Department of Electronics and Communication Engineering, Adhiyamaan College of

Engineering, Krishnagiri, Tamil Nadu, India<sup>2-4</sup>

Associate Professor, Department of Electronics and Communication Engineering, Adhiyamaan College

of Engineering, Krishnagiri, Tamil Nadu, India<sup>1</sup>

**ABSTRACT**: Neuromorphic systems have given enhancements over the years, supporting Spiking neural networks (SNN) event-driven nature in the demonstration of low power utilization. The neuromorphic systems require high integration to create a useful functional silicon brain-like, moving to 3D integrated circuits (3D-ICs) with the three- dimensional network on chip (3D- NoC) interconnecting an appropriate approach that permits scalable design, shorter connections, and lower power consumption. Therefore mega dense neuromorphic systems also encounter the reliability issue where a single point of failure can hit the system's operation. The methodology represents NASH, a fault-tolerant 3D- NoC according to neuromorphic as processing elements, fine spiking neuron processing cores (SNPCs) with spike- timing-dependent-plasticity (STDP) on-chip learning. The outcome on MNIST classification, using the fault-tolerant shortest-path K-means-based multicast routing algorithm (FTSP-KMCR), it exhibits the NASH system and can maintain high accuracy for up to 30% permanent liability to interconnect with acceptable regions and power on high when compared to other existing systems.

**KEYWORDS**: Digital Neuromorphic, Spiking neural network, Fault-tolerant , Spiking neuron processing cores,NoC

#### **I.INTRODUCTION**

Spike-based mostly neuro-inspired computing has step by step gained awareness each to produce higher insight into the brain's computation and to explore this computation through event-driven neuro-inspired systems. Spiking neural networks (SNN) square measure used in several applications, like vision systems, brain-computer interface , neuro- robotics management and call making, and brain stimulation. SNN tries to simulate the information process inside the biological brain, which requires parallel arrays of neurons to speak via spikes . In cryptography information as spikes, SNN employs a writing theme which might be rate writing, population writing, or temporal coding. The vegetative cell dynamics of this model are thought of as an associate integration method, together with a spiking mechanism. Typical spikes no matter their amplitude and from square measure handled as similar events, and from the point to finish, last regarding 2 milliseconds traveling down nerve fiber lengths[1]. Another spiking somatic cell model that is noted for its elaborated simulation of the particle channels of a biological somatic cell is the Hodgkin and Huxley model. This model is nonlinear and random. However, it's complicated, making it less ideal for large-scale simulation and hardware implementation. Software simulation of SNN has shown to be a flexible way of exploring the behavior .Hardware implementation (neuromorphic system) on the other hand, provides an alternative approach that holds thepotential for independent spikes to be generated accurately, and resulting

#### International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 9<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22) 28<sup>th</sup> - 29<sup>th</sup> April 2022

#### Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

spikesto be simultaneously fired in real-time. Also, hardware implementation has the edge of computational acceleration over software simulations, and peculiar multi-neuro-core neuromorphic architectures can leverage the parallelism and spike sparsity available in SNN to deliver fast processing with low power. Recent artificial neural networks (ANNs) consist of several layers, and this has caused the term deep neural network (DNN). Each layer of a DNN is often expressed as a two-dimensional (2D) structure, creating the complete network itself a three-dimensional (3D) structure.

#### **II. RELATED WORK**

The neuromorphic chips in 2D domain is a 14-nm 60-mm2 manycore on-chip learning processor. Hence processor uses off-chip communication interfaces in a hierarchical mesh fashion for connecting the chips. In a four-core binate weight neuromorphic chip is applied[4]. Most core houses contain 512 LIF neurons, of entire 528K binary junctions unified in three levels, and a speculative spike-driven joint pliability learning. Therefore the absolutely integrated digital SNN chips which given, mixed-signal seems to be captivating so can exactly follow the dynamics of actual neural systems[5]. The main specimen of this system is described as the ROLLS neuromorphic processor. ROLLS has 128K analog synapses and 256 neuron circuits that support Hence the plausible dynamics and also bi-stable spike-based pliability mechanisms lead to the wellknown learning abilities. The asynchronous digital logic circuits are combined for synapses and to the network configurations. Rolls get evaluated and reveal the perfect characteristics of a pattern recognition task. It requires a complicated implementation to deal with challenges of scalability and precision. True North is another 2D neuromorphic chip with 4096 cores arranged in a mesh topology of  $64 \times 64$ . The system uses a butterfly fat-tree- based topology, that includes mimics the brain's connectivity more closely, will not able to be mapped on an ASIC design because its shape led to the devastation of the silicon area. The pointto-point way in the parent node controls the path diversity hence the bandwidth imbalance here makes the thermal hot spots increases. So the conventional 3D- ICs, TSVs cast-off vertical links between layers and it makes a reduction of hops in the 2D counterparts which includes TSVs enable the biological characteristics of spiking neurons in which the proposed system makes use of the TSVs as neuronal membrane and enhances the capacitance of TSV accordingly ...

#### **III. METHODOLOGY**

The all-inclusive architecture of the proposed fault-tolerant 3D-NoC-based neuromorphic system (NASH). The 3D mesh-based architecture is composed of many nodes. Every node is created with the use of a spiking neuron processing core (SNPC), a fault-tolerant multicast 3D router (FTMC- 3DR)[3]. The SNPC implants256 LIF neurons with the crossbar-based synapse[6]. LIF model is certified and it is impulsive or most learning a is suitable for digital implementation due to its modest hardware cost. The resulting spike from a LIF neuron while executing the task is sent to post-synaptic neurons, which could either be in the same SNPC. If in the same SNPC, the spike is acquired by the post-synaptic neurons later it has been identified, and the weights of its synapse with the pre-synaptic neurons is obtained through the crossbar. Hence the destination SNPC is completely different because the spike is encoded at the network interface as a packet uploaded to local FTMC- 3DR which routes it to the target SNPC(s) attached synaptic neurons occupied. In destination SNPC(s), the spike is translated, postsynaptic neurons are occupied. In destination SNPC(s), the spike is translated, and with the synapse value obtained by the crossbar, dispatched to the postsynaptic neurons located, and with the synapse value obtained by the crossbar, dispatched to the postsynaptic neurons.

International Journal of Innovative Research in Science, Engineering and Technology<br/>An ISO 3297: 2007 Certified OrganizationVolume 11, Special Issue 1, April 20229th National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22)<br/>28 th -29 th April 2022

#### Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

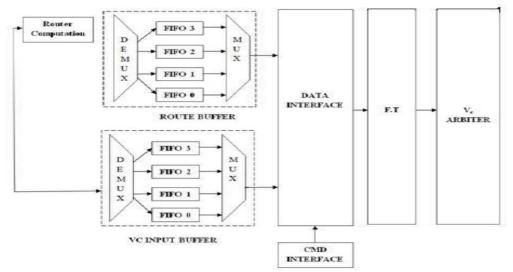

Architecture Of Fault Tolerant Routing Interconnect System For Neural NoC

The encoder and decoder is NI between an SNPC and its local FTMC-3DR. The first 2 bits indicate the 00Type00 of the flit: "00" for configuration and "11" for the spike. The next 9 bits are used to represent the address of the source neuron. The following 6 bits are documented on time in which the source neuron blasted the spike[7]. The last 64 bits is used for the spike array from presynaptic neurons. To ensure economical operation, we have a tendency to adopt and explore the k-means based mostly} multicast routing algorithmic rule (KMCR) and also the shortest path k-means based multicast routing algorithmic rule (SP-KMCR). The KMCR routes spike pack ets by 1st dividing the destination nodes into subgroups, and inside these subgroups, centre of mass nodes that have the smallest amount distance from the opposite nodes within the set ar hand-picked[8].

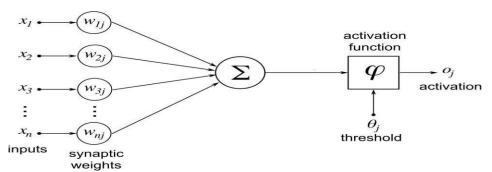

Diagram of an artificial neuron with n inputs with their corresponding synaptic weights. All weighted inputs are added and an activation function controls the generation of the output signal.

The packets are then routed to those centre of mass nodes and from these centre of mass nodes, employing a spanning subtree, to the destination nodes. The SP-KMCR additionally operates in an exceedingly similar manner, dividing the destination nodes into subgroups and so scheming the source's distance to all or any the nodes within the subgroups. However, in contrast to the KMCR, that uses centroids, the SP-KMCR selects a node (SP node) within the set with a lowest distance from the supply node and sends packets.

#### International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 9<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22) 28<sup>th</sup> -29<sup>th</sup> April 2022

#### Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

#### **IV. RESULTS**

The projected system was designed in Verilog-HDL, synthesis and layout were created with Cadence tools. For ASIC implementation, we have a tendency to use NANGATE 45nm open-cell library because the commonplace cells, Open RAM for generating the system memory and TSV from FreePDK3D45 [7]. To explore the potency of the writer, we have a tendency to appraise the neurons interconnect performance mistreatment 2 benchmarks named Inverted apparatus (network size a pair of two) 2 3), and Wisconsin (network size three of three 3 3) performing arts 2 experiments. the primary experiment was distributed while not faults, mistreatment the SP-KMCR, KMCR, and also the baseline XYZ unicast based mostly (UB) multicast routing algorithms[8]. The second was distributed with faults mistreatment the FTSP-KMCR and also the FT-KMCR algorithms. we have a tendency to conjointly perform system performance analysis, by classifying MNIST knowledge set with on-chip and off-chip learning. what is more, we have a tendency to appraise NASH's hardware complexity in terms of space and power and gift a comparison with some notable existing works. The system analyses the network presentation in terms of standard latency and output for the SP-KMCR, KMCR, and XYZ-UB algorithms. The primary observation on SP-KMCR, KMCR, and also the XYZ- UB as represented show similar performance in terms of output on the Inverted setup benchmark inside the zero.08 and 0.2 vary of SR. this leads to the outcome of all 3 algorithms can well service spike traffics inside this vary. Hence the outcome of the XYZ-UB saturates at SR of zero.2 whereas that of the KMCR and SP-KMCR continues to extend.

#### International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 9<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22) 28<sup>th</sup> - 29<sup>th</sup> April 2022

#### Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

However, they each perform some pre-processing on the information set, which makes classification easier. Odin especially utilized skewing and down sampling, which additionally simplified the information set. a tutor signal was additionally accustomed to enhance the coaching. NASH to 28nm (0.55V) with a well-known scaling equation adopted from and its conjunction operation (SOP) when put next thereupon of Odin as shown in, consumes less energy at one.397pJ per SOP.

#### V. CONCLUSION

Hence the paper verifies the hardware design, architecture, and evaluation of a fault-tolerant 3D-NoC-based neuromorphic system using the on-chip learning named NASH system. The methodology system leverages the low communication cost, high scalability and parallelism, and throughput in 3D- NoC for a neuromorphic system that supports large SNN in a massive number. To handle challenges that may arise in spike communication and lead to performance degradation, we employed the FTSP-KMCR routing algorithm. We presented the network and performance evaluation of NASH with and without faults. Moreover, the experiments show that the proposed NASH achieves better accuracy with less ACT when compared to the baseline system and sustains a 97.6% accuracy with up to 30% fault rate while experiencing a 40% increase in the ACT as opposed to the baseline system. As future work, we intend to further explore large-scale biological applications that will leverage NASH's potential and reveal other aspects of its efficiency. Furthermore, these applications could provide guidelines for other may need to be included NASH for efficiency, faulttolerance, in and performance.

#### REFERENCES

- 1. C. C. Nachiar, N. Ambika, R. Moulika and R. Poovendran, "Design of Cost-effective Wearable Sensors with integrated Health Monitoring System", 2020 Fourth International Conference on I-SMAC (IoT in Social Mobile Analytics and Cloud) (I-SMAC), pp. 1289-1292, 2020.

- 2. Ranjani MB, Poovendran R (2016) Image duplication copy move forgery detection using discrete cosine transforms method. Int J Appl Eng Res 11(4):2671–2674

- 3. Poovendran R, Sumathi S (2019) An area-efficient low-power SCM topology for high performance network-on Chip (NoC) architecture using an optimized routing design. Concurrency Comput Pract Experience 31(14)

- POOVENDRAN R, SUMATHI S. An area-efficient FPGA implementation of network-on-chip (NoC) router architecture for optimized multicore-SoC communication [J]. Sensor Lett, 2018, 16(7): 552-560

- Poovendran R., Muniraj S., Nandakumar A. On Chip Implementation of Packet Switched Network. IOSR Journal of Electronics and Communication Engineering (IOSR-JECE), 2014, vol. 9, is. 2, pp. 38– 42.

- 6. Ogbodo mark ikechukwu, khanh N. dang and Abderazek ben abdallah "On the Design of a Fault-Tolerant Scalable Three-Dimensional NoC-Based Digital Neuromorphic System with On-Chip Learning", May 2021.

- 7. <u>An Area-Efficient FPGA Implementation of Network-on-Chip (NoC) Router Architecture for Optimized</u> <u>Multicore-</u> <u>Soc Communication.</u> R Poovendran, S Sumathi - Sensor Letters, 2018.

- D. Valencia, J. Thies, and A. Alimohammad, "Frameworks for efficient brain-computer interfacing," IEEE Trans. Biomed. Circuits Syst., vol. 13, no. 6, pp. 1714–1722, Dec. 2019.

- 9. Z. Bing, C. Meschede, F. Röhrbein, K. Huang, and A. C. Knoll, "A survey of robotics control based on learning- inspired spiking neural networks," Frontiers Neurorobotics, vol. 12, pp. 436–457, Jul. 2018.

- B. Sen-Bhattacharya, S. James, O. Rhodes, I. Sugiarto, A. Rowley, A. B. Stokes, K. Gurney, and S. B. Furber, "Building a spiking neural network model of the basal ganglia on SpiNNaker," IEEE Trans. Cognit. Develop. Syst., vol. 10, no. 3, pp. 823–836, Sep. 2018.

#### International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 9<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22) 28<sup>th</sup> - 29<sup>th</sup> April 2022

Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

- 11. C. Frenkel, J.-D. Legat, and D. Bol, "Morphic: A 65-nm 738k synapse/mm2 quad-core binary-weight digital neuromorphic processor with stochastic spike-driven online learning," IEEE Trans. Biomed. Cir cuits Syst., vol. 13, pp. 999–1010, Oct. 2019.

- M. Davies, N. Srinivasa, T. H. Lin, G. Chinny, Y. Cao, S. H. Choday, G. Dimou, P. Joshi, N. Imam, S. Jain, and Y. Liao, "Loihi: A neurophic manycore processor with on-chip learning," IEEE Micro, vol. 38, no. 1, pp. 82–99, Jan. 2018.

- S. Yang, J. Wang, B. Deng, C. Liu, H. Li, C. Fietkiewicz, and K. A. Loparo, "Real-time neuromorphic system for large-scale conductance-based spiking neural networks," IEEE Trans. Cybern., vol. 49, no. 7, pp. 2490–2503, Jul. 2019.

- 14. S. Yang, B. Deng, J. Wang, H. Li, M. Lu, Y. Che, X. Wei, and K. A. Loparo, "Scalable digital neuromorphic architecture for large-scale biophysically meaningful neural network with multi-compartment neurons," IEEE Trans. Neural Netw. Learn. Syst., vol. 31, no. 1, pp. 148–162, Jan. 2020.

- compartment neurons," IEEE Trans. Neural Netw. Learn. Syst., vol. 31, no. 1, pp. 148–162, Jan. 2020.

15. Q. Xia and J. J. Yang, "Memristive crossbar arrays for brain-inspired computing," Nature Mater., vol. 18, no. 4, pp. 309–323, Mar. 2019.

#### BIOGRAPHY

Dr. R. Poovendran, Associate Professor, Department of Electronics and Communication Engineering , Adhiyamaan College of Engineering , Anna University .

#### Aswini S,

Department of Electronics and Communication Engineering, Adhiyamaan College of Engineering, Anna University.

#### International Journal of Innovative Research in Science, Engineering and Technology *An ISO 3297: 2007 Certified Organization* 9<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '22) 28<sup>th</sup> -29<sup>th</sup> April 2022

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Indrani M,

Department of Electronics and Communication Engineering, Adhiyamaan College of Engineering, Anna University

Keerthana M,

Department of Electronics and Communication Engineering, Adhiyamaan College of Engineering, Anna University

Impact Factor: 8.118

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com