e-ISSN: 2319-8753 | p-ISSN: 2347-6710

EDIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

800

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 12, Issue 5, May 2023

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

## Impact Factor: 8.423

9940 572 462

$\bigcirc$

e-ISSN: 2319-8753, p-ISSN: 2320-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

|| Volume 12, Issue 5, May 2023 ||

DOI:10.15680/LJIRSET.2023.1205457

### **Telecommand System using FPGA**

Rahul G Mohite, Prof. Chethan G S,

Department of Electronics & Communication Engineering, Jain University, India

Assistant Professor, Department of Electronics & Communication Engineering, Jain University, India

**ABSTRACT-** The main intent of this project was to create an encoder for ground stations using FPGA to send telecommands concurrently so that commands would not go sequentially. Since the signal passes through space, it gets external noise added to them naturally which may also cause damage to the spacecraft. Using BCH code in programming helps to avoid errors during encoding. A parity generator helps to nullify the noise level. And get desired response from the spacecraft.

**KEYWORDS***-TC*- Telecommand, TM- Telemetry, GEO- Geostationary Equatorial Orbit, LEO- Low Earth Orbit, RF-Radio Frequency, BCH- Bose Chaudhury Hocquenghem,"FPGA- Field Programmable Gate Arrays", CLB-Configurable Logic Blocks, ASIC- Application Specific Integrated Circuits, IDE- Integrated Development Environment, RTL- Register Transfer Level, IC- Integrated Circuit, POR- Power-on Reset.

#### I. INTRODUCTION

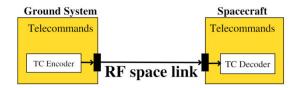

The word Telecommand is derived from the word **tele** which means **remote** in Greek, and **command** which means the order in Latin. So, both together make the definition of Telecommand, that is the command sent to the remote system or connected without any direct medium such as wires. The main part of the TC is to convey the controlling information from the ground station to the spacecraft according to which TM can change the parameters which are given from the ground state and the same to receive from the spacecraft to the ground state. Since these are wireless or do not directly containany medium of transferring command the only way is through signals. But the values revived from the parameter sensor such as temperature, connection, direction, etc, give the analog data to the TC which needs to be converted to share commands from bothsides. Therefore, the TC in the Ground System needs Encoder, and TC in the spacecraft needs Decoder. The data is shared through the RF space link.

The transmission of the carrier wave could be by electromagnetic means. The encoder is coded with the help of cycling codes, which meansany lateral shift of the code word is also a code word. This also uses Bose- Chaudhury-Hocquenghem (BCH) Codes, which means this codingdesign of optimum codes is to make the block size smallest for a given size of the message block toobtain desired value. When we desire to give large code, we must look forthe best error-correctingcapabilities. Since BCH is known as the most important and powerful error-correcting cyclic code can be used in our project. Since the security of information from both spacecraft and ground stations is very important, we need to look after their protection for them.Fig.1. shows the top basic block diagram of communication.

Fig. 1. Basic Block diagram of Communications with spacecraft

A parity coder is used to generate polynomialstobalance the errors during encoding and decoding made by the code or external noise. The noise may change the information carrier wave to alter the data which could be harmfulto both data and spacecraft, since the communication system of the spacecraft and ground stations are quite expensive the signals must be sent with high accuracy. And there might be a condition where our telemetry does not respond to our command

e-ISSN: 2319-8753, p-ISSN: 2320-6710 www.ijirset.com | Impact Factor: 8.423 A Monthly Peer Reviewed & Referred Journal |

#### || Volume 12, Issue 5, May 2023 ||

#### DOI:10.15680/IJIRSET.2023.1205457

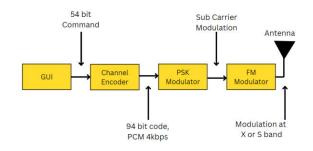

at that time our design helps since we use FPGA design which concurrently processes the codeso the data can be sent in the intermediate steps. While in another hand C or any language goes in sequential order, which may cause unidentified delays to our command. Since this command contains the data which needs to be secured unidentified delays may cause damage or even chances of losing data. Because of this, the command may work or may not. The telemetry measures all the physical parameters and sendsthem to the telecommand from the spacecraft which contains data on the surroundingsand health of the spacecraft and should be given to TC without any disruption.Fig.2. shows the block diagram of the Ground Segment.

Fig. 2. Diagram of the Ground segment.

#### **II. HARDWARE**

#### A. FPGA (FIELD PROGRAMMABLE GATE ARRAY)

"These are semiconductor devices that are based within a matrix of CLB (configurable logic blocks) which are connected to provided programmable interconnections." (FPGA world) This provides the function of reprogramming applications according to the functional requirements after manufacturing. This feature makes it different from ASICs (application-specific integrated circuits). Fig.3. shows the architecture of FPGA.

| G    |     |     |     |     |     |

|------|-----|-----|-----|-----|-----|

|      |     |     |     |     |     |

|      | CLB | CLB | CLB | CLB |     |

| - [] | CLB | CLB | CLB | CLB | TP- |

|      |     |     |     |     |     |

|      | CLB | CLB | CLB | CLB |     |

| - [  | CLB | СLВ | CLB | CLB |     |

|      |     |     |     |     |     |

| Ľ    |     |     |     |     |     |

Fig. 3. FPGA Architecture (<u>https://www.geeksforgeeks.org</u>)

Everybrand has its architecture but on all terms they have variation. This architecture contains programmableinterconnect, configurable I/O blocks, and configurablelogic blocks. Spartan 2 (XC2S200PQ208AMS0345) was used in this design. The design of the chip also includes Top-Down Design, the logic that fits well with the architecture of the component we have chosen, synchronous design, avoiding bus contention and floating nodes, and protection against metastability.

e-ISSN: 2319-8753, p-ISSN: 2320-6710 www.ijirset.com | Impact Factor: 8.423 A Monthly Peer Reviewed & Referred Journal |

#### || Volume 12, Issue 5, May 2023 ||

#### | DOI:10.15680/IJIRSET.2023.1205457 |

The design utilizes the top-down design which means the high-level blocks are defined first and the lower-level blocks' implementation details are filled in. This method simplifies the design, allows more than one editor to design, and allows flexibilityin the chip when necessary. Replacement of section with a high rate of performance design without changingother parts of the chip. The chip cannot be alteredafter production, simulation becomes an extremely important consideration in chip design, therefore the simulation must be done compulsorily before the chip is sent for fabrication. This method allows each module to simulate independently from the rest of the design.

#### **III. SOFTWARE**

"VHDL is generally used to edit text models that describe logic circuits. These kinds of modelsare processed by a synthesis program only if it is part of the logic design."This has a process to control the parallelism inherent in hardware design, but this process distinguishes syntax from the parallel process in the task. The next process is to simulate which also means testing. A program of simulation is used to check/test the logic design using simulationto represent the logic circuit design that interfaces to the design. This group of the testing of the model is called Testbench.

Anyone can design/build hardware of any design which can later be fabricated in a VHDLIDE to get the "RTL schematic" of the required circuit. After the generation of the RTL schematic, they can be verified using simulation software which allows the wave of inputs and outputs of the circuit after giving the appropriate testbench.

Xilinx is part of AMD which develops, designs, and markets programmable logic products including ICs, predefined system functions delivered as intellectual property, customer training, field engineering, and software design tool.

"Modelsim is the verification and simulation tool for the VHDL codes, Verilog, system Verilog, and mixed language designed code."The debuggingenvironment provided by Modelsim's robust allows for tracking down the cause of the problem.

#### **IV. VHDL CODE ARCHITECTURE**

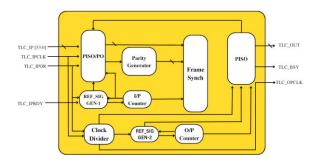

#### **Telecommand Encoder (Top Module)**

- PISO/PIPO (Parallel-In Serial-Out/ Parallel-Out Shift Register)

- Clock Divider

- Reference signal generator 1

- Input Counter

- Frame Synchronizer

- Reference Signal Generator 2

- Output Counter

- Parity Generator

- o EXOR Gate1 & 2

- o OR Gate

- o D-Flip Flop

- o 5-Bit Shift Register

- o 6-Bit Latch

Input Data: 54-bits D\_(1) to D\_(54) where D\_(1) is MSB

Output Data: 6-bits P\_01 (n) to P\_06 (n) where P\_01 is MSB, n varies from 0 to 54.

**Step1:** Initialize P\_01(0), P\_02(0), P\_03(0), P\_04(0), P\_05(0), P\_06(0) to 0<sub>B</sub>.

**Step 2:** For n=1 to 54, do

- $P_01(n) = P_02(n-1)$

- $P_02(n) = P_03(n-1)$

- $P_{03(n)} = P_{04(n-1)}$

e-ISSN: 2319-8753, p-ISSN: 2320-6710 www.ijirset.com | Impact Factor: 8.423 A Monthly Peer Reviewed & Referred Journal |

|| Volume 12, Issue 5, May 2023 ||

DOI:10.15680/IJIRSET.2023.1205457

- $P_04(n) = P_05(n-1)$

- P\_05(n)= D\_(n) XOR P\_01(n-1) XOR P\_06(n-1)

- $P_{06(n)} = D(n) \text{ XOR } P_{01(n-1)}$

Step3: Parity bits P\_01(54), P\_02(54), P\_03(54), P\_04(54), P\_05(54), P\_06(54).

#### V. WORKING

#### Algorithm

Step 1: Set POR, Ready Signal, to '0'.

Step 2: Apply the 54-bit parallel data command at the input shift register.

Step 3: When 'RDY' input is 1, the parallel data will be latched into the shift register and the input counter will start to count.

Step 4: Parity will be generated on every count.

Step 5: At the count of 54, the 54-bit parallel data and 6-bit parity will be taken into frame synchronizer.16-bit header and 20-bit trail bits are added to make a command frame of 96 bits.

Step 6: At the counter of 55, the frame synchronizer produces a ready pulse for the output shift register. Counter 1 is set to '0'.

Step 7: When the PISO finds a ready pulse at the input, the parallel 96-bit command is latched into the register and the output counter will start to count.

Step 8: For count (in output counter) >96, the serial data would be transmitted out of the shift register at speed of 4kbps.

Step 9: At the count of 96 (atthe output counter), the shift register transfers its last bit out and the output counter is set to '0'.

Step 10: The PIPO (input shift register) is enabled to accept the next command. Fig. 4. Shows the block diagram of interconnects and pin diagram.

Fig. 4. Block Diagram

#### Practical Working.

Since the health of the spacecraft is very necessary, we have to look for a good communication medium. Therefore, the proposed project deals with communication system design from the ground station to the spacecraft. TC and TM are the two major working parts when it comes to unchangeable or non-replaceable parts.TM sends measured parameters such as temperature, speed, direction, voltage control, etc., according to which the ground station changes and sends the data

#### IJIRSET©2023

e-ISSN: 2319-8753, p-ISSN: 2320-6710 www.ijirset.com | Impact Factor: 8.423 A Monthly Peer Reviewed & Referred Journal |

#### || Volume 12, Issue 5, May 2023 ||

#### DOI:10.15680/IJIRSET.2023.1205457

to change accordingly. Since the data or signals must be sent in an air medium there would be some loss of signal which may damage to spacecraft. Therefore, the parity generator is kept nullifying the loss. The BCH code allows the optimization of the errors during the encoding. Data shared by any spacecraft also includes several security data which need to be secured and sent to the respective ground station.

#### **VI.** CONCLUSION

A 4kbps TC encoder has been designed and understood. This TC uses PSK modulation with a 44-kHz sub-carrier so that it does not intervenewith 32 kHz of TM by which several errors can be reduced which were caused by cross talks. This project can be implemented for the spacecraft which are in GEO which means points toward one place of approximately 36,000 km from the earth's surface, or the altitude of the GEO is about 5.6 times the radius.

Direct-broadcast Televisions satellites are the best examples of GEO satellites. Earth-surveillance missions including military and weather tracking missions could be done by GEO. Not only in GEO but in the LEO as well. Which is approximately 2,000km of its altitude.Finally,itexploresthe utilization of data within a particular place by involving another spacecraft. As time changes this may get improved.

#### References

- 1. The Designer's Guide to VHDL, Volume s3, Third Edition (System on Silicon), Peter Ashenden.

- 2. VHDL: Programming by Example, Douglas Perry.

- 3. Digital system design Using VHDL, Jr. Charles H. Roth

- 4. VHDL Primer, A (3<sup>rd</sup>Edition), Jayaram Bhasker

- 5. FPGA Prototyping by VHDL Examples: Xilinx, Spartan-3 Version, Pong P Chu.

- 6. <u>WWW.edaboard.com</u>

- 7. <u>WWW.fpgaworld.com</u>

- 8. <u>WWW.vhdl.org</u>

- 9. WWW.doulos.com/knowhow/vhdl

#### BIOGRAPHY

#### **Rahul G Mohite**

U.G. Student, Department of Electronics & Communication Engineering

Faculty of Engineering and Technology

Jain (Deemed-to-be University)

Bengaluru, Karnataka, India.

#### Prof. Chethan G S

Assistant Professor, Department of Electronics & Communication Engineering

Faculty of Engineering and Technology

Jain (Deemed-to-be University)

Bengaluru, Karnataka, India.

Impact Factor: 8.423

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com