(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

### **Impact Factor: 8.699**

## Volume 14, Issue 4, April 2025

⊕ www.ijirset.com ⊠ ijirset@gmail.com 🖄 +91-9940572462 🕓 +91 63819 07438

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 4, April 2025

|DOI: 10.15680/IJIRSET.2025.1404359|

## Design an Efficient Braun Multiplier Using KSA Based Pass Transistor Logic Using 22nm

#### J.S.Deepika

Assistant Professor, Department of ECE, Sri Vasavi Institute of Engineering & Technology (Autonomous), Nandamuru,

Pedana, A.P, India

#### M.Dharma Teja, K.Sai Sri, B.Kesava Sai Nath, CH.Pavani

Department of ECE, Sri Vasavi Institute of Engineering & Technology (Autonomous), Nandamuru, Pedana, A.P, India

**ABSTRACT**: The Braun multiplier is a well-established and widely recognized array multiplier architecture that has gained popularity due to its inherent simplicity, structural regularity, and efficient mechanism for partial product generation. These characteristics make it a highly favourable choice in the design of digital circuits, particularly in applications where predictable and uniform hardware structures are essential. Traditionally, Braun multipliers have been effectively utilized in various arithmetic operations within digital systems; however, with the continuous evolution of modern computing systems, there has been an increasing demand for designs that offer not only high computational speed but also reduced power consumption and enhanced overall performance.

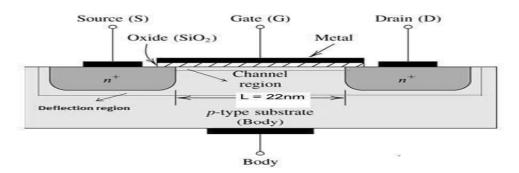

In response to these emerging requirements, the integration of a Kogge-Stone Adder (KSA) into the Braun multiplier architecture, along with the implementation of advanced Pass Transistor logic technology at the 22nm scale, represents a significant and innovative advancement over conventional multiplier designs. The inclusion of the KSA improves the speed of the final addition stage, which is critical in large-bit-width multipliers, due to the parallel prefix structure of the KSA that minimizes the carry propagation delay. Furthermore, leveraging 22nm CMOS technology allows for more compact, power-efficient, and faster circuits, which are highly desirable in the design of high-performance digital systems.

**KEYWORDS**: Pass Transistor Logic, Braun multiplier, Kogge Stone Adder, Area consumption, , Parallel Prefix Adder, 22nm Technology, Tanner EDA.

#### I. INTRODUCTION

The Braun multiplier is a well-established and widely recognized array multiplier architecture that has gained popularity due to its inherent simplicity, structural regularity, and efficient mechanism for partial product generation. These characteristics make it a highly favourable choice in the design of digital circuits, particularly in applications where predictable and uniform hardware structures are essential. Traditionally, Braun multipliers have been effectively utilized in various arithmetic operations within digital systems; however, with the continuous evolution of modern computing systems, there has been an increasing demand for designs that offer not only high computational speed but also reduced power consumption and enhanced overall performance. In response to these emerging requirements, the integration of a Kogge-Stone Adder (KSA) into the Braun multiplier architecture, along with the implementation of advanced Pass Transistor logic technology at the 22nm scale, represents a significant and innovative advancement over conventional multiplier designs. The inclusion of the KSA improves the speed of the final addition stage, which is critical in large-bit-width multipliers, due to the parallel prefix structure of the KSA that minimizes the carry propagation delay. Furthermore, leveraging 22nm CMOS technology allows for more compact, power-efficient, and faster circuits, which are highly desirable in the design of high-performance digital systems.Keywords – Pass Transistor Logic, Braun multiplier, Kogge Stone Adder, Area consumption, , Parallel Prefix Adder ,22nmTechnology,Tanner EDA..

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 4, April 2025

#### |DOI: 10.15680/IJIRSET.2025.1404359|

#### **II. PROPOSED SYSTEM**

The new Braun Multiplier using Kogge Stone Adder design now uses 22nm technology transistors.

In 22nm technology, the transistors have a much smaller channel length, significantly reducing area consumption and improving efficiency.

The system now uses fewer transistors—down from the original 276—resulting in less circuit complexity, lower power consumption, and faster operation.

Building a Better Braun Multiplier:

After testing the adders, researchers used them in a 4-bit Braun Array Multiplier (BAM).

The version of PTL, was used to build a BAM, and the performance was compared.

The results? All designs worked well, but one stood out.

Results for the PTL KSA (in 22nm):

Power usage: lower than in the 120nm version due to better transistor performance

Area: more compact layout compared to 120nm design

Delay: overall delay will be reduced to

With growing demand for faster and smaller electronics, efficient circuit design is more important than ever. This study proves that by rethinking how we build multipliers, we can save space, reduce power, and increase speed all without sacrificing performance.

Now, using 22nm technology, we take a big step forward in chip design. Smaller, faster, and more energy-efficient circuits are no longer the future they're the present

#### **III. EXPERIMENTAL RESULTS**

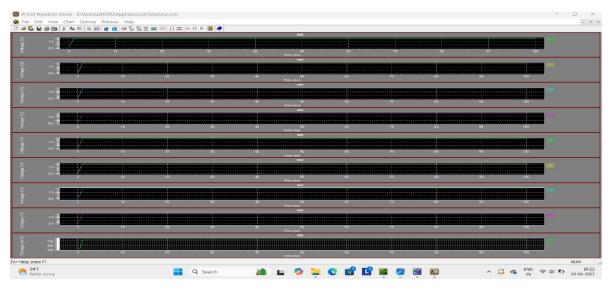

Fig 1: Input Waveforms

|www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 4, April 2025

#### |DOI: 10.15680/IJIRSET.2025.1404359|

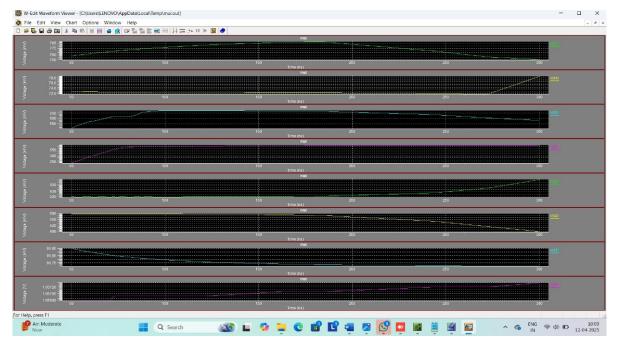

#### Fig 2: Output Waveforms

| nput file: mul.sp<br>rogress: Simulation completed                                                                                                                                                       | Output: mul.out                                                                                                                                                                                     |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| otal nodes: 1162 Active devices:<br>otal devices: 265 Passive devices:                                                                                                                                   |                                                                                                                                                                                                     |  |  |  |

| Inductors - 0<br>Transmission lines - 0<br>Voltage sources - 9<br>VCVS - 0<br>CCVS - 0<br>V-control screws - 0<br>HEDL devices - 0<br>HEDL devices - 0<br>Independent nodes - 1152<br>Total nodes - 1162 | Mutual inductors - C<br>Coupled transmission lines - O<br>Current sources - C<br>VCCS - O<br>T-control CCCS - O<br>External C model instances - O<br>Subcircuit instances - I<br>Boundary nodes - 1 |  |  |  |

| Measurement result summary<br>TRAN_Measure_Delay_2 =                                                                                                                                                     |                                                                                                                                                                                                     |  |  |  |

| Parsing<br>Setup<br>DC operating point<br>Transient Analysis<br>Overhead                                                                                                                                 | 0.01 seconds<br>0.06 seconds<br>0.08 seconds<br>0.36 seconds<br>0.80 seconds                                                                                                                        |  |  |  |

| Total<br>Simulation completed                                                                                                                                                                            | 1.31 seconds                                                                                                                                                                                        |  |  |  |

#### Fig 3: Delay OutputS

| T-Spice - [muLout]                               |                                         |               |               |               |               |  |                | - 0 × |

|--------------------------------------------------|-----------------------------------------|---------------|---------------|---------------|---------------|--|----------------|-------|

| File Edit View Simulation Table S                |                                         |               |               |               |               |  |                |       |

| * Gefnrs = 0 [sq]                                | tnom = 25 [deg C]                       |               |               |               |               |  |                |       |

| dernis - o (sq)                                  | chom = Sp (quad c)                      |               |               |               |               |  |                |       |

| * General options:                               |                                         |               |               |               |               |  |                |       |

| temp = 25 [deg C]                                | threads = 16                            |               |               |               |               |  |                |       |

| · Output options:                                |                                         |               |               |               |               |  |                |       |

| acout = 1                                        | ingold = 0                              |               |               |               |               |  |                |       |

| *                                                |                                         |               |               |               |               |  |                |       |

| Device and node counts:                          |                                         |               |               |               |               |  |                |       |

| MOSFETs - 256                                    | MOSFET geometries - 4                   |               |               |               |               |  |                |       |

| * BJTS - 0                                       | JFETS - 0                               |               |               |               |               |  |                |       |

| MERPETS - 0                                      | picdes - 0                              |               |               |               |               |  |                |       |

| · Capacitors - 0                                 | Resistors - 0                           |               |               |               |               |  |                |       |

| * Inductors - 0                                  | Matual inductors - 0                    |               |               |               |               |  |                |       |

| Transmission lines - 0                           | Coupled transmission lines - 0          |               |               |               |               |  |                |       |

| <ul> <li>Voltage sources - 9</li> </ul>          | Current sources - 0                     |               |               |               |               |  |                |       |

| <ul> <li>VCVS - 0</li> </ul>                     | VCCS - 0                                |               |               |               |               |  |                |       |

| * ccvs - 0                                       | ccca = 0                                |               |               |               |               |  |                |       |

| <ul> <li>V-control switch - 0</li> </ul>         | I-control switch - 0                    |               |               |               |               |  |                |       |

| <ul> <li>Macro devices - 0.</li> </ul>           | External C model instances - 0          |               |               |               |               |  |                |       |

| * HDL devices - 0                                |                                         |               |               |               |               |  |                |       |

| <ul> <li>Subcircuits - 0</li> </ul>              | Subcircuit instances - 44               |               |               |               |               |  |                |       |

| <ul> <li>Independent nodes - 1152</li> </ul>     | Boundary nodes - 10                     |               |               |               |               |  |                |       |

| Total nodes - 1162                               |                                         |               |               |               |               |  |                |       |

| * *** 2 WARNING MESSAGES GENER                   | ATED DURING SETUP                       |               |               |               |               |  |                |       |

|                                                  |                                         |               |               |               |               |  |                |       |

| *SEDIT: Alter=0                                  | ACMODEL O AC O TRANSIENT 1 TRANSFER     | -             |               |               |               |  |                |       |

| SEDIT: Analysis types book 0 /                   | ACMODEL O AC O TRANSIENT I TRANSPER     | O NOISE O     |               |               |               |  |                |       |

| *WEDIT: .tran 4e-007 4e-00<br>TRANSIENT ANALYSIS | 7                                       |               |               |               |               |  |                |       |

| Time <s> V(00)<v></v></s>                        | V(01) <v> V(02)<v> V(03)<v></v></v></v> | V(04) <v></v> | V(05) <v></v> | V(06) <v></v> | V(07) <v></v> |  |                |       |

| 0.000000+000 2.6831e-005 9                       | .5295e-002 1.8045e-001 3.5213e-001      | 1.8223=-001   | 3.80376-001   | 3.6524e-001   | 3.33610-001   |  |                |       |

| tatus Input Out Start Date Elap.                 |                                         |               |               |               |               |  |                |       |

| nished mulap m. March 2. 00                      |                                         |               |               |               |               |  |                |       |

|                                                  |                                         |               |               |               |               |  |                |       |

|                                                  |                                         |               |               |               |               |  |                |       |

| kdy.                                             |                                         |               |               |               |               |  | Ln 205, Col 32 | NUM   |

|                                                  |                                         |               |               | C #           |               |  |                |       |

#### Fig 4: Transistor count output

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 4, April 2025

#### |DOI: 10.15680/IJIRSET.2025.1404359|

| File Edit View | Simulation Table | Setup Window               | Help        |             |             |             |             |             |      |                | -        |

|----------------|------------------|----------------------------|-------------|-------------|-------------|-------------|-------------|-------------|------|----------------|----------|

| A 13 6 14      | 1 Ba 🖀 🖉 🗠 🗠     | 3 🐻 🥏 🛠 🕨                  | • II II     |             |             |             |             |             |      |                |          |

| .050981e-007   | 2.6783e-005      | 9.5282e-002                | 1.7936e-001 | 5.1418e-001 | 5.0025e-001 | 4.5111e-001 | 4.7642e-001 | 3.3372e-001 |      |                |          |

|                |                  | 9.5307e-002                |             |             |             |             |             |             |      |                |          |

| .060834e-007   | 2.6783e-005      | 9.5284e-002                | 1.7959e-001 | 5.0231e-001 | 4.8785e-001 | 4.5441e-001 | 4.8149e-001 | 3.3383e-001 |      |                |          |

|                |                  | 9.5306e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5284e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5305e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5285e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5305e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5285e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5305e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5286e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5304e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5286e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5303e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5286e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5303e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5287e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5303e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5287e-002                |             |             |             |             |             |             |      |                |          |

|                |                  | 9.5303e-002<br>9.5287e-002 |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             |      |                |          |

| BEGIN NON-GRA  | PHICAL DATA      |                            |             |             |             |             |             |             |      |                |          |

| wer Results    |                  |                            |             |             |             |             |             |             |      |                |          |

| d and from ti  |                  | 0.7                        |             |             |             |             |             |             |      |                |          |

|                |                  | .507337e-004 w             | atte        |             |             |             |             |             |      |                |          |

| x power 8.758  |                  |                            | accs.       |             |             |             |             |             |      |                |          |

|                |                  | time 8.16498e-             | 0.08        |             |             |             |             |             |      |                |          |

| D POWEL 31320  | 3136-003 dc      | 0.104306-                  |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             |      |                |          |

| END NON-GRAPH  | ICAL DATA        |                            |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             |      |                |          |

| BEGIN NON-GRA  | PHICAL DATA      |                            |             |             |             |             |             |             |      |                |          |

| ASUREMENT RES  | ULTS             |                            |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             |      |                |          |

| us Input Ou    | t Start Date E   | lap                        |             |             |             |             |             |             |      |                |          |

| hed mul.sp m   | March 2 (        | 10:                        |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             |      |                |          |

|                |                  |                            |             |             |             |             |             |             | <br> | 1-105 6-104    | NUM      |

|                |                  |                            |             |             |             |             |             |             |      | Ln 196, Col 24 | NUM      |

| op Stories     |                  |                            |             |             |             |             |             | ピ 🖸 🔅       |      | A 🕲 ENG        | 0 m - 14 |

#### Fig 5 Power consumption output

#### **IV.CONCULSION**

This project involved designing a Braun Multiplier using a Kogge-Stone Adder (KSA) combined with pass transistor logic (PTL), targeting 22nm Pass Transistor technology in Tanner EDA. The design aimed to achieve high speed and low power by using the regular and modular structure of the Braun Multiplier, the fast performance of the KSA, and the area-saving benefits of PTL. Simulation results confirmed that the multiplier worked correctly and showed improvements in speed, area, and power usage compared to traditional CMOS designs. Using PTL reduced the number of transistors, which helped decrease unwanted capacitance and increase switching speed. The KSA, with its efficient carry propagation, further boosted the overall speed. The use of 22nm technology also improved the design by allowing for a smaller, more power-efficient layout. The final design passed all DRC (Design Rule Check) and LVS (LayoutVersus Schematic) checks in Tanner EDA, with very low leakage, proving that the approach is suitable for VLSI applications.In summary, combining the KSA and PTL in the Braun Multiplier provides a fast, compact, and low-power solution for modern digital systems.

#### REFERENCES

- 1. "Design an Efficient Braun Multiplier Using KSA Based CMOS Logics"

- Authors: Daphni S, Vijula Grace K. S, Judith Johnsi J, Bamini S

- 2. "Design of Low Power 4-Bit CMOS Braun Multiplier Based on Threshold Voltage Techniques" *Author:* Dayadi Lakshmaiah

- 3. "Design of Braun Multiplier with Kogge Stone Adder & Its Implementation on FPGA" *Authors:* Ms. Madhu Thakur, Prof. Javed Ashraf

- 4. "Des ign of High-Speed Low Power Computational Blocks for DSP Processors"\*\* *Author:* Sai Prasad Goud

- 5. \*\*"Efficient Serial Multiplier Design using Ripple Counters, Kogge-Stone Adder and Full Adder" *Authors:* S. Sangeetha, S. S. R. Kumar

- 6. "Design and Performance Analysis of Multipliers Using Kogge Stone Adder" *Authors:* Neeraja Bandi, R. Sai Prasad Goud

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 4, April 2025

#### |DOI: 10.15680/IJIRSET.2025.1404359|

- 7. " An Optimized 4×4 Braun Multiplier for Parallel Processing Architectures with a 3-bit KSA Adder" *Authors:* M. Sakthimohan, Elizabeth Rani G, Monisha P, Nandhini S

- 8. " Design and Implementation of Braun Multiplier using Verilog: Review" *Authors:* Anukrati Sharma, Aparna Mittal, Anshika Singh, Raman Kapoor

- 9. " Design Analysis of Wallace Tree Based Multiplier Using Approximate Full Adder and Kogge Stone Adder" *Authors:* Navin Kumar M, Adithyaa R S, Bhavan Kumar D, Pavithra T

- 10. S. S. Sapatnekar, "Timing Analysis and Optimization of Sequential Circuits," Springer Science & Business Media, 2012.

- 11. P. Gupta, A. B. Kahng, P. Sharma, and D. Sylvester, "Selective Gate-Length Biasing for Cost-Effective Runtime Leakage Control," IEEE Transactions on Computer

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com