ISSN(O): 2319-8753

ISSN(P): 2347-6710

# International Journal of Innovative Research in Science Engineering and Technology (IJIRSET)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

**Impact Factor: 8.699**

Volume 14, Issue 4, April 2025

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710

#### Volume 14, Issue 4, April 2025

|DOI: 10.15680/IJIRSET.2025.1404361|

## Design an Area Efficient Kogge Stone Adder Using Pass Transistor Logic of 22nm

#### Y.R.K.Paramahamsa

Assistant Professor, Department of ECE, Sri Vasavi Institute of Engineering & Technology (Autonomous), Nandamuru, Pedana, A.P, India

#### D.Punnaiah, P.Sukanya, S.Mohan Kumar, V.Eswar Kumar

Department of ECE, Sri Vasavi Institute of Engineering & Technology (Autonomous), Nandamuru, Pedana, A.P, India

**ABSTRACT:** The design of an area-efficient Kogge-Stone Adder (KSA) using pass transistor logic (PTL) in 22nmtechnology focuses on optimizing the performance, power, and area of high-speed arithmetic units used in modern computing architectures. The Kogge-Stone Adder is a widely used parallel prefix adder known for its fast carry propagation, making it ideal for applications requiring high-speed arithmetic computations, such as digital signal processing (DSP), microprocessors, and cryptographic systems. However, traditional KSA designs suffer from increased area and power consumption due to their complex interconnection and large transistor count. To overcome these challenges, pass transistor logic (PTL) is integrated into the design to significantly reduce transistor count and improve area efficiency

**KEYWORDS**: Pass Transistor Logic, Kogge Stone Adder, Area consumption, Parallel Prefix Adder, 22nm Technology, Tanner EDA.

#### I. INTRODUCTION

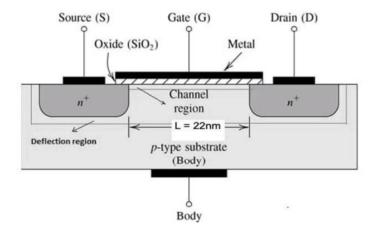

The Kogge-Stone Adder (KSA) is a fast and efficient type of binary adder used in digital circuits, especially in modern processors where speed is very important. It is designed to add two binary numbers by calculating all the necessary carry values in parallel, instead of waiting for each carry to move from one bit to the next. In traditional adders like the ripple carry adder, each bit has to wait for the carry from the previous bit, which takes time and slows down the addition process. The Kogge-Stone adder avoids this delay by using a special tree structure made of logic gates that can compute all carry signals at the same time. This is known as a parallel prefix computation PASS Transistor Logic :Pass Transistor Logic involves nMOS or pMOS transistors to transfer the charge from one node of a circuit to another node under the control of MOS gate voltage.In traditional CMOS logic, each logic function requires a complementary pair of transistors (one PMOS and one NMOS). In contrast, PTL uses a single transistor to implement logic functions, reducing the transistor count.

#### II. PROPOSED SYSTEM

Kogge Stone Adder using Pass Transistor Logic uses 22nm technology transistors.

In 22nm technology, the transistors have a much smaller channel length, leading to lower area consumption, better speed, and improved efficiency.

The system uses fewer transistors and benefits from the compact and high-speed features of 22nm CMOS design, which helps reduce overall circuit complexity.

Power usage: significantly reduced due to improved tec

Results for the PTL KSA (in 22nm):

Power usage: lower than in the 120nm version due to better transistor performance

Area: more compact layout compared to 120nm design

Delay: Delay will be reduced

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 4, April 2025

|DOI: 10.15680/IJIRSET.2025.1404361|

This study successfully shows that a 4-bit Kogge Stone Adder can be made smaller, faster, and more power-efficient by using Pass Transistor Logic combined with 22nm technology. With a reduced number of transistors, lower power consumption, and a smaller layout area, the new design is perfect for VLSI and DSP systems, where saving space is just as important as being fast.

#### III. EXPERIMENTAL RESULTS

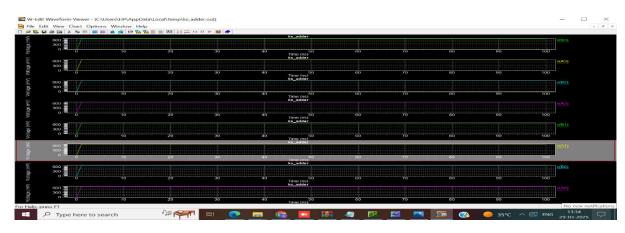

Fig.1.Inputs Wave forms of Proposed system

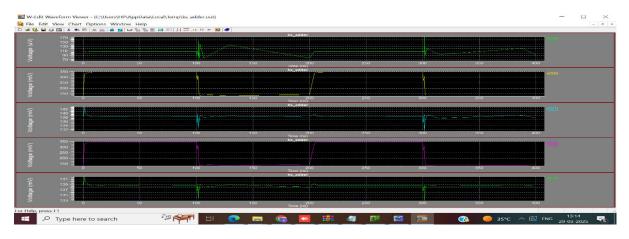

Fig:2: Output Wave forms of Proposed System

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710

#### Volume 14, Issue 4, April 2025

|DOI: 10.15680/IJIRSET.2025.1404361|

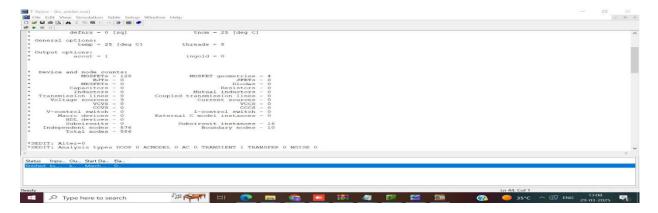

Fig 3:Delay for proposed system

Fig 4:Transistor count in proposed system

Fig 5: power consumption in proposed system

#### IV. CONCLUSION

In this project, a 4-bit Kogge-Stone Adder (KSA) was successfully designed and implemented using pass transistor logic in 22nm CMOS technology with the help of Tanner EDA tools. The main goal was to create a compact, high-speed adder by taking advantage of the efficient Kogge-Stone architecture and the reduced transistor count of pass transistor logic. The Kogge-Stone Adder is known for its fast carry generation and low delay, which makes it ideal for high-performance systems. By using pass transistor logic instead of traditional CMOS logic, the design used fewer transistors, which helped reduce the overall chip area. Simulations confirmed that the adder worked correctly for all input combinations and showed improved speed and lower power consumption. The physical layout in the 22nm technology node also showed efficient use of space, meeting the project's area-saving goals.

In summary, this project shows that combining the Kogge-Stone architecture with pass transistor logic in advanced technology can be a great choice for fast and compact arithmetic circuits. Future work can expand this approach to larger adders and further explore the balance between power, speed, and area in more complex systems

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710

#### Volume 14, Issue 4, April 2025

|DOI: 10.15680/IJIRSET.2025.1404361|

#### REFERENCES

- 1.Zimmermann and W. Fichtner, "Low-Power Logic Styles: CMOS Versus Pass-Transistor Logic," IEEE Journal of Solid-State Circuits, vol. 32, no. 7, pp. 1079–1090, 1997.

- 2.Kogge, P. M., and Stone, H. S., "A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Equations," IEEE Transactions on Computers, vol. C-22, no. 8, pp. 786–793, Aug. 1973.

- 3.D. Marković, V. Stojanović, B. Nikolić, M. A. Horowitz, and R. W. Brodersen, "Methods for True Energy-Performance Optimization," IEEE Journal of Solid-State Circuits, vol. 39, no. 8, pp. 1282–1293, 2004.

- 4.R. K. Krishnamurthy et al., "High-Performance and Low-Power Challenges for Sub70nm CMOS Technologies," IEEE International Symposium on Low-Power Electronics and Design, pp. 368–373, 2002.

- 5.H. T. Bui, A. K. Al-Sheraidah, and Y. Wang, "Design and Analysis of Low-Power 1Transistor Full Adders Using XOR and XNOR Gates," IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 49, no. 1, pp. 25–30, 2002.

- 6.S. H. Unger, "Analysis of Asynchronous Circuits," IEEE Transactions on Computers, vol. C-25, no. 7, pp. 677–685, July 1976.

- 7.M. D. Ercegovac and T. Lang, "Digital Arithmetic," Morgan Kaufmann, 2003.

- 8.Y. Jiang, A. Al-Sheraidah, Y. Wang, E. Sha, and J. Wang, "A Novel Multiplexer-Based Low-Power Full Adder," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 51, no. 7, pp. 345–348, July 2004.

- 9.S. Timarchi and K. Navi, "Universal Barrel Shifter Using Novel Reversible Logic Gates," Journal of Computer Science, vol. 6, no. 2, pp. 197–203, 2010.

- 10.S. S. Sapatnekar, "Timing Analysis and Optimization of Sequential Circuits," Springer Science & Business Media, 2012.

- 11.P. Gupta, A. B. Kahng, P. Sharma, and D. Sylvester, "Selective Gate-Length Biasing for Cost-Effective Runtime Leakage Control," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 27, no. 10, pp. 1836–1845, Oct. 2008.

- 12.C. H. Chang, J. Gu, and M. Zhang, "A Review of 0.18-um Full Adder Performances for Tree Structured Arithmetic Circuits," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 13, no. 6, pp. 686–695, 2005.

- 13.Y. Leblebici, S. Kang, C. H. Kim, and H. Mutlu, "CMOS Digital Integrated Circuits Analysis and Design," McGraw-Hill, 5th Edition, 2022.

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

📵 9940 572 462 💿 6381 907 438 🔀 ijirset@gmail.com