(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

## **Impact Factor: 8.699**

## Volume 14, Issue 5, May 2025

⊕ www.ijirset.com ⊠ ijirset@gmail.com 🖄 +91-9940572462 🕓 +91 63819 07438

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### **Volume 14, Issue 5, May 2025**

DOI: 10.15680/IJIRSET.2025.1405212

# Design of High-Speed, Low-Leakage CAM for Search-Intensive Applications

Prakash M<sup>1</sup>, Jayabratha S<sup>2</sup>, Anbusri G<sup>3</sup>, Monika R<sup>4</sup>, Sanjay C<sup>5</sup>

Assistant Professor, Department of Electronics and Communication Engineering, Builders Engineering College,

Kangeyam, Tirupur, Tamil Nadu, India<sup>1,2</sup>

U.G. Students, Department of Electronics and Communication Engineering, Builders Engineering College, Kangeyam,

Tirupur, Tamil Nadu, India<sup>3,4,5</sup>

**ABSTRACT**: Content Addressable Memory (CAM) is an essential element in rapid search applications like network routers, cache memory, and pattern recognition. However, traditional CAM architectures face the challenge of elevated power usage because of their parallel search functions. The suggested model employs a transmission gate (TG) configuration for the design of CAM cells. The transmission gate type of comparison circuit enhances switching speed and minimizes the voltage drop across the output stage. Therefore, this TG model exhibits a shorter delay compared to standard CAM architectures. A paired match lines each analysis technique is introduced to minimize ML transitions per word while also enhancing density in the comparison units. In contrast to the traditional design, where there is one ML discharge for each one-bit mismatch, the new method results in only one ML discharge for two-bit mismatches and so forth. This results in a reduction of ML dynamic-power consumption. Furthermore, we conduct a comparative study of existing low-power CAM architectures versusour proposed design, assessing factorslike power efficiency, search delay, and area overhead. The experimental findings reveal a notable decrease in power consumption while preserving competitive performance. This research offers important insights into energy-efficient CAM architecture, improving their applicability for future computing tasks.

**KEYWORDS**: ContentAddressableMemory(CAM), TransmissionGate(TG), Low-PowerCAMDesign, Matchline(ML) Optimization, Search Efficiency, Dynamic Power Reduction, Energy-Aware Architecture, Pattern Recognition, Routing Applications and Cache Systems.

#### I. INTRODUCTION

Memory is utilized to retain data. There are different varieties of computer memories. One type among them is referred to as associative memory. This associative memory is also known as content addressable memory (CAM). CAM functions as a hardware search engine that matches content instead of physical addresses. Associative memories operate at a faster pace than traditional RAM since they execute the entire procedure in a single clock cycle. CAM functions in a way that is different from that of random access memory (RAM).

The address is taken as the input to RAM, whereas the data is produced as the output of RAM. In context-aware computing, a user inputs information in the form of text, and the address linked to the content is provided as output. CAM also incorporates external circuitry like sense amplifiers, decoders, etc. It is widely employed in applications such as ultra-fast computers, space satellite ground station systems, cache memory, pattern matching, and more. CAM carries out the function of bit storage using RAM (preferably SRAM) and can also compare bits. Creating a high-speed CAM that can manage longer text is a challenging task.

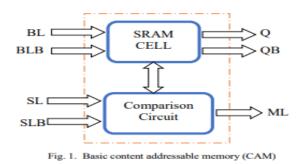

Designers had to create low-power cells with top performance to meet the standards of the lower technology node.CAM's design can be split into two parts. The first chip consists of an SRAM circuit. The information is used for storage. The second component of the block is a comparator circuit that verifies whether the input provided corresponds to the SRAM cell's stored data. Figure 1 reveals that the SRAM cell has the input terminal called Bit Line (BL) pointing to the bit to be written (stored) within the cell.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405212|

SRAM bit cell output is Q and Q-bar. Further dividing into the evaluation loop, the input of this search line (SL) bit specifies the data against which BL should be contrasted. The output of the CAM circuit is the match line (ML). If the bit-line and select line differ, the output will be 0; otherwise, the match line (ML) will have a value of 1. Table I. lists several input and output circumstances of CAM. Before we go on forth several notes to mention that, the NMOS transistor is ideal to pass logic "0" and turns ON when its gate voltage is high. PMOS transistor is good for passing logic '1' and turning ON when its gate voltage is low.

| BL | BLB | SL | SLB | ML |

|----|-----|----|-----|----|

| 0  | 1   | 0  | 1   | 1  |

| 0  | 1   | 1  | 0   | 0  |

| 1  | 0   | 0  | 1   | 0  |

| 1  | 0   | 1  | 0   | 1  |

#### TABLE I. CONVENTIONAL CAM OPERATION

**CAM:**Content-addressable memories (CAMs) are hardware search engines that are much faster than algorithmic approaches for search-intensive applications. CAMs are composed of conventional semiconductor memory (usually SRAM) with added comparison circuitry that enables a search operation to complete in a single clock cycle. The two most common search-intensive tasks that use CAMs are packet forwarding and packet classification in Internet routers.

We survey recent developments in the design of large-capacity content-addressable memory (CAM). A CAM is a memory that implements the lookup-table function in a single clock cycle using dedicated comparison circuitry. CAMs are especially popular in network routers for packet forwarding and packet classification, but they are also beneficial in a variety of applications that require high-speed table lookup. The main CAM-design challenge is to reduce power consumption associated with the large amount of parallel active circuitry, without sacrificing speed or memory density. In this paper, we review CAM- design techniques at the circuit level and at the architectural level. At the circuit level, we review low-power match line sensing techniques and search line driving approaches. At the architectural level we review three methods for reducing power consumption.

Content-addressable memory (CAM) is frequently used in applications, such as lookup tables, databases, associative computing, and networking, that require high-speed searches due to its ability to improve application performance by using parallel comparison to reduce search time. Although the use of parallel comparison results in reduced search time, it also significantly increases power consumption.

Content-addressable memory (CAM) is a special type of computer memory used in certain very high speed searching applications. It is also known as associative memory, associative storage, or associative array, although the last term is more often used for a programming data structure.

#### Hardware Associative Array:

Unlike standard computer memory (random accessmemory or RAM) in which the user supplies a memory address and the RAM returns the data word stored at that address, a CAM is designed such that the user supplies a data word and the

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405212|

CAM searches its entire memory to see if that data word is stored anywhere in it. If the data word is found, the CAM returns a list of one or more storage addresses where the word was found (and in some architectures, it also returns the data word, or other associated pieces of data). Thus, a CAM is the hardware embodiment of what in software terms would be called an associative array.

#### **Standards for Content-Addressable Memories:**

A major interface definition for CAMs and other Network Search Elements (NSEs) was specified in an Interoperability Agreement called the Look-AsideInterface (LA-1 and LA-1B) developed by the NetworkProcessing Forum, which later merged with the OpticalInternetworking Forum (OIF). Numerous devices have been produced by Integrated Device Technology,Cypress Semiconductor, IBM, and others to the LA interface agreement. On December 11, 2007, the OIF published the serial look aside (SLA) interface agreement.

#### Semiconductor implementations:

Because a CAM is designed to search its entire memory in a single operation, it is much faster than RAM in virtually all search applications. There are cost disadvantages to CAM however. Unlike a RAM chip, which has simple storage cells, each individual memory bit in a fully parallel CAM must have its own associated comparison circuit to detect a match between the stored bit and the input bit. Additionally, match outputs from each cell in the data word must be combined to yield a complete data word match signal. The additional circuitry increases the physical size of the CAM chip which increases manufacturing cost. The extra circuitry also increases power dissipation since every comparison circuit is active on every clock cycle. Consequently, CAM is only used in specialized applications where searching speed cannot be accomplished using a less costly method.

#### AlternativeImplementations:

To achieve a different balance between speed, memory size and cost, some implementations emulate the function of CAM by using standard tree search or hashing designs in hardware, using hardware tricks like replication or pipelining to speed up effective performance. These designs are often used in routers.

#### TernaryCAMs:

BinaryCAMisthemostbasictypeofCAM; it employs datasearch wordsmadeentirely of 0s and 1s. This adds searchflexibilitybygivingoneormorebits in the stored data word a third matching condition of "X" or "Don't Care." A ternaryCAM could, for instance, have a stored word of "10XX0," which will match any of the four search words & '10000, "10010," 10100,' or & '10110". Because the internal memory cell must now encode three potential states rather than the two of binary CAM, the increased search flexibility comes at an extra cost over binaryCAM.Normally, including a mask bit (a "care" or "don't care" bit) on each memory cell will activate this further state. Using complex valued representations, holographic associative memory offers a mathematical model for "Don't Care" fused associative recall.

#### **Example Applications:**

Incomputernetworkingequipment, content-addressable memory is quite frequently employed. When a network switch gets a Data Frame from one of its ports, for instance, it updates an internal table with the source MAC address of the frame and the port it was received on. Then the table is checked for the destination MAC address to find out which port the frame needs to be moved to; it is forwarded on that port. Normally, the MAC address table uses a binary CAM, so the destination port can be rapidly located and the switch's latency reduced.

Network routers are typical applications of ternary CAMs, where each address has two components :the networkaddress thatcanchangeinsizedependingonthe subnet setup, and the host address that takes up the rest bits. A network mask for each subnet tells which bits of the address are the network address and whichbits are the host address. Consulting the router's routing table— each known destination network address, its linked networkmaskandthedataneededtoroutepacketstothat destination—routing occurs. The router without CAM would match the destination address of the packet to be routed against every entry in the routing table, do a logicalANDwiththenetworkmask,andcompareitwith the network address. If they are equal, the appropriate routing data is employed to send the package.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405212|

The lookupprocedurebecomesquitefastifyouuseaternary CAM for the routing table. Since the addresses are kept using "don't care" for the host part of the address, a search of the destination address in the CAM immediately finds the appropriate routing entry; the CAM hardware performs both the masking and comparison.

#### **Other CAMA pplicationsInclude:**

- CPUstoragecontrollersandTranslation Look aside Buffers

- Database engines

- Datacompressionhardware

- Artificialneuralnetworks

- IntrusionPreventionSystem

#### **II. EXISTING MODELS**

#### 1) LowMatch-LineVoltageSwingTechniqueFor Content Addressable Memory:

Designing a content addressable memory (CAM) with enhancedsearchefficiencycallsforauniquepre-charge approach. By reducing the loading capacitance and ML voltage swing, this method lowers the match line (ML) powerdissipation. The integration of this approach with predictive 45-nm CMOS technology has been accomplished in a 256×64-bit NOR-based CAM; post layout simulations are done in SPECTRE on a 1 V supply. This approach lowers the energy dissipation by 38% vis-à-vis the old pre-charging, which improves search speed by 4.7%.

#### 2) QUASIFGMOS6TSRAMCellDesign:

#### AStrategyForLowPowerApplications:

Low power and high performance based static random access memory (SRAM) has gained paramount interest as they became indivisible part of microprocessors, portable-devices, system-on-chips and modern VLSI systems. As technology scaled down, low voltage and low power operation are be coming the foremost important issue for mixed signal systems. This paper implements various low power strategies for 6T SRAM cell withsupply voltage VDD=220mV using TSMC 0.18µm technology in mentor graphics tool while operating in sub-threshold region which isverycrucial for lowering power dissipation and achieves higher speed compared to CMOS circuits.

#### 3) Single Bit-Line 11T SRAM Cell For Low Power And Improved Stability

This research focuses on a novel 11T static random access memory (SRAM) cell that incorporates power gatingtransistors and atransmission gatetoachievelow leakage and dependable writing functionality. The proposed cell features distinct paths for reading and writing, which significantly enhances both read and writeperformance.

Additionally, it addresses theissue of row half select disturbance and employs a row-based virtual ground signal to prevent unnecessary bit-line discharge in the unselected row, thus reducing energy usage. The cell also benefits from low power consumption attributed to the stack effect. To demonstrate the effectiveness of the cell, its design parameters are compared with other SRAM cells that havebeenpublished, specifically, conventional6T, 10T, 9T, and power-gated 9T (PG9T).

In standby mode, this cell showsareductioninleakagepowerfrom 6. 71to7. 37% at an operating voltage of 1. 2 V, with improvements inwriteandreadpowerranging from 29. 21 to 58. 68% and 32. 74 to 71. 11% compared to other cells. The proposed cell achieves higher write and read staticnoisemarginswithenhancementsof13.54and63. 28%, respectively, when compared to the conventional 6T SRAM cell. The cell also offers an improvement in write delay of 29. 77 to 49. 40% and a read delay improvement of 7 to 12% when compared to 9T, 10T, and PG9T, respectively.

#### **ExistingCAM Designs:**

There are primarily two categories of structures: the matching and searching approach. Also referred to as: NAND-CAM and NOR-CAM [9,10]. The main source of powerus agein CAM cells is the matchine along with the search line pair (SL, SLB).

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405212|

#### A. NAND-CAMDesign:

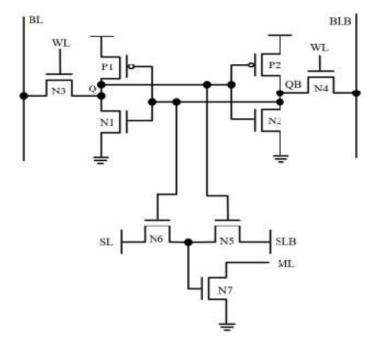

In NAND-CAM design, a standard 6 transistor SRAM cell is linked to the input bit lines via the two access transistors.Twocross-coupledinvertersareconnected to thestoragenodesQandQB.TransistorsN5,N6,andN7 are utilized for comparing the data that needs to be searched. The output is obtained from the source terminal of N7 through ML, as illustrated in Fig. 2. A pre-charge circuit is attached, which is in turn linked to an inverter to generate the output ML.

#### Fig.2. BasicNAND-CAM structure

#### **TABLEII.NAND-CAMOPERATION**

| BL | BLB | SL | SLB | ML | REMARKS                                               |

|----|-----|----|-----|----|-------------------------------------------------------|

| 0  | 1   | 0  | 1   | 1  | N6-ON, N7-OFF.<br>Therefore, ML does<br>not discharge |

| 0  | 1   | 1  | 0   | 0  | N6, N7-ON. ML<br>discharges to<br>ground              |

| 1  | 0   | 0  | 1   | 0  | N5, N7-ON. ML<br>discharges to<br>ground              |

| 1  | 0   | 1  | 0   | 1  | N5-ON, N7-OFF.<br>Therefore, ML does<br>not discharge |

The ML lines start in the pre-charge phase and subsequently discharge to the ground when all CAM cells are matched. A significant disadvantage of NAND CAMisthatitcausesavoltagedropacrossthefollowing stage due to the pass transistors N5 and N6 used in the comparison circuit. This results in a heightened delay factor, which in turn decreases the speed of the comparison circuit. Nevertheless, employing pass transistors uses minimal power. To enhance and assess thespeedparameterfurther, we transition to NORCAM design.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405212|

#### B. NOR-CAMDesign:

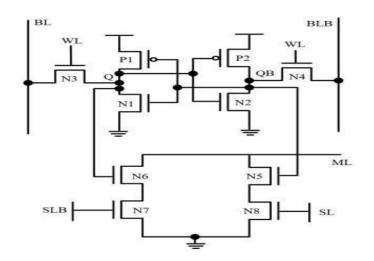

NOR-CAM design additionally includes a standard 6T SRAM cell featuring NOR functionality as a reference circuit.AsdepictedinFig.3,transistorsN5andN6link to the storage nodes QB and Q respectively. The match line (ML) is replenished prior to the searching process. When one or more cells in a CAM do not match, the match-line discharges, logichasbeenestablishedinNOR.Theresultisreturned signifying that the comparison onlyaftereveryCAMcellwithinasingleCAMwordis matched, meaning the search is completed. The CAM input text can remain unchanged from its original state. Incaseofamismatch, the ML is promptly discharged to 0 due to the brief pullsignificant down route. This situation also leads to power consumption. Table Ш outlinestheNORCAMoperationbyemployingvarious input scenarios.

#### Fig.3.BasicNOR-CAM structure

#### **TABLEIII.NOR-CAMOPERATION**

| BL | BLB | SL | SLB | ML | REMARKS                                                               |

|----|-----|----|-----|----|-----------------------------------------------------------------------|

| 0  | 1   | 0  | 1   | 1  | N5, N7-ON. No closed<br>path. Therefore, ML does<br>not discharge     |

| 0  | 1   | 1  | 0   | 0  | N5, N8-ON. A path exists<br>for discharge. ML<br>discharges to ground |

| 1  | 0   | 0  | 1   | o  | N6, N7-ON. A path exists<br>for discharge. ML<br>discharges to ground |

| 1  | 0   | 1  | 0   | 1  | N6, N8-ON. No closed<br>path. Therefore, ML does<br>not discharge     |

#### C. TransmissionGateCAMDesign:

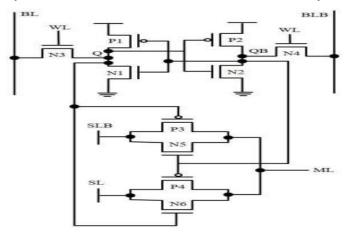

The transmission gate variant of the comparison circuit enhancestheswitchingspeedandminimizesthevoltage drop Thus, this TG model experiences as horter delay compared to traditional CAM across output stage. the architectures. Asignificantissue with the passtransistor is the threshold voltage drop across the output when the gate terminal is at logic 1. This becomes problematic if the input remains continuously at logic 1. This concern is categorically unacceptable and necessitates an additional circuit at the output to boost voltage. The TG-CAMcomprises10transistorsandiscapable of passing both 0 and 1. Another key benefit is the absence of supplementarypre-chargecircuitry. This contributes to a decrease in layout area. The TG-CAM design is illustrated in Fig. 4, with the design's functionality summarized in Table IV.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### **Volume 14, Issue 5, May 2025**

#### |DOI: 10.15680/IJIRSET.2025.1405212|

#### Fig.4.Transmissiongate(TG-CAM)structureTABLE IV. TG-CAM

#### TABLE IV. TG-CAM FUNCTIONALITY

| BL | BLB | SL | SLB | ML | REMARKS                                         |

|----|-----|----|-----|----|-------------------------------------------------|

| 0  | 1   | 0  | 1   | 1  | TG1 (P3, N5) ON. SLB<br>(1) passed to output ML |

| 0  | 1   | 1  | 0   | 0  | TG1 (P3, N5) ON. SLB<br>(0) passed to output ML |

| 1  | 0   | 0  | 1   | 0  | TG2 (P4, N6) ON. SL (0)<br>passed to output ML  |

| 1  | 0   | 1  | 0   | 1  | TG2 (P4, N6) ON. SL (1)<br>passed to output ML  |

#### III. PROPOSEDMETHODOLOGY

#### **ProposedOML-CAM:**

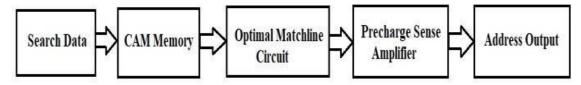

Fig.5.BlockdiagramofproposedOML-CAM:

The block diagram of the suggested OML CAM is depicted in fig. 5. Considering the high-speed characteristic of TG-CAM, the suggested CAM macro aims to provide the following contributions:

- **1.** Atwo-bitstoragewithacomparison-basedCAMcell that incorporates OML evaluation is proposed. Because twoadjacentcells possessa collective evaluationblock, each pair of cells shares a single ML node.

- **2.** Unlike the traditional design, which has one ML dischargeforeachone-bitmismatch,twoMLdischarges fortwobitmismatches,andsoforth,theproposedOML approach has only one ML discharge for two-bit mismatches.ThisresultsinreducedMLdynamic-power consumption.

- **3.** TocreateanN-bitCAMword,N/2proposedcellsare constructed in TG-type match line so that the match speed (ML delay) aligns with the traditional high-speed match line.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 5, May 2025 |DOI: 10.15680/IJIRSET.2025.1405212|

**4.** The performance (power and delay) of the proposed OML-CAM is evaluated against referenced designs and detailed analyses are included to assess the viability of searching operations across varying process–voltage–temperatures.

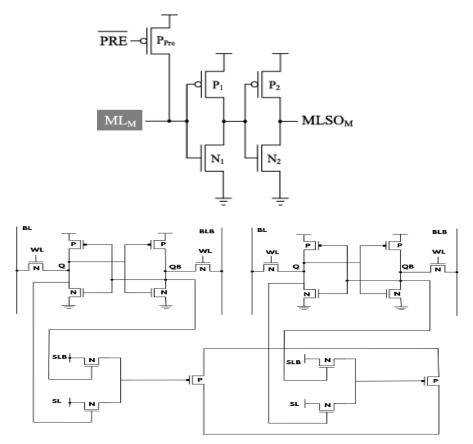

Improvements in circuit-level techniques made in the comparison and evaluation section of CAM cells enhancedsearchspeed.Duringthesearch,mostofthe entries in a CAM array result **ProposedOptimizedMatch-LineStructure.**in mismatches. In traditionalandexistingMLmethods,each1-bitcellis equippedwithaspecificcompare-evaluatecircuit.All the mismatched cells generate individual ML state-change (from pre-charged to discharged) pathways in a CAM word or row. The worst-case scenario for discharge occurs when all bits miss in an ML row, at which point the row discharges through 'N' equivalent paths for an N-bit data (word). The suggested OML- CAM aims to minimize the number of discharge pathways. A 2-bit (2B) TG-CAM cell is employed, where the storage on the rights ideand the storage on the left side are compared within a common ML block. Every search scenario isinitiated by a fully a storage or pre-charge transistor (PPre) of the sense amplifier shown in **Fig. 6.**

Fig.6.Inverter-basedsenseamplifierwithpre-chargecontrolledbySignalPRE.

#### 1. Pre-ChargePhase:

Pre-charge signal (PRE) isimplemented using '0'logic, while SLi and SLi are likewise reset to '0'; ML is pre- charged to the supply voltage (VDD).

#### **2.** EvaluationPhase:

PRE is modified to '1' logic so that the pre-charge transistor (Ppre) is OFF while the input search data is applied to the complementary search-lines (SLi, SLi). When SL corresponds with the bit line (BL), the match line ML stays high; otherwise, during a mismatch condition, ML is discharged to zero.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405212|

#### **3.** OperationOfProposedOML-CAM:

Content Addressable Memory (CAM) is a distinct type of memory intended for rapid data searches and simultaneous comparisons. In contrast to traditional RAM, which accesses databased on a specific daddress, CAM scans for a specific input pattern throughout all stored entries at once and provides the address of the corresponding match. This capability renders CAM crucial for uses such as high-speed network routing, pattern identification, and cache memory.

AvitalcomponentofCAMdesignisitsmatchline(ML) architecture, which influences power efficiency and operational speed. This paper examines the functioning of CAM with an ideal shared match line for two CAM cells, paired with a pre-charge sense amplifierto improve performance.

**Content Addressable Memory (CAM) Architecture:** CAM is made up of a matrix of CAM cells, with each cellabletostoreandcomparedatabits.ACAMcell generallyconsistsof:StorageElement:Oftenapair of cross-coupledinverters(SRAM-based)ornon-volatile memory elements.

- **Comparison Circuitry:** Consisting of XOR logic to compare archived data with incoming data.

- Match line (ML): A signal line utilized to identify a match or mismatch.

- Pre-chargeSenseAmplifier: Guaranteesrapid and energy-efficient detection of match situations.

#### SharedMatchline Structure:

A common match line architecture enhances power and area efficiency by minimizing unnecessary components in the CAM array. In a two-CAM-cell shared ML configuration:

- The match line is common to two neighboring CAM cells, which lowers ML capacitance and power consumption.

- Each CAM cell adds to theML state depending on the outcome of its comparison task.

- An active pre-charge and evaluation phase guarantees correct operation Operation Phases:

#### 1. PrechargePhase:

- Prior to the start of comparison, the ML is charged to a high voltage (Vdd).

- A pre-charge sense amplifier (PSA) guarantees that the ML is completely charged, minimizing variations and the effects of leakage current.

#### 2. EvaluationPhase:

- The CAM array receives the input data, and each CAM cell executes an XOR operation to compare the stored data with the input data.

- When both cells correspond to the input, the ML stays at a high level; if not, it discharges.

- The PSA identifies the ultimate ML condition and quickly enhances minor voltage discrepancies to signal a match or mismatch status.

#### Pre-charge Sense Amplifier (PSA) in CAM Operation:

Apre-chargesenseamplifierisessentialforminimizing ML power consumption and enhancing speed. Its roles encompass:

Swift Pre-charging: Rapidly charges the ML to Vdd prior to the comparison cycle.

- Low-Power Sensing: Identifies small voltage changes and amplifies them for dependable match detection.

- Decreased ML Capacitance: By merging with a shared ML, the PSA boosts power efficiency.

#### AdvantagesofSharedMLandPSA:

- **Power Decrease:** Sharing ML diminishes switching activity, resulting in decreased dynamic power usage.

- Space Efficiency: A reduced number of match line wires results in a more condensed CAM design.

- EnhancedSpeed:Quickermatchlinedischarge and sensing enhance the speed of search operations.

- Enhanced Noise Immunity: PSA enhances minor voltage variations, rendering detection resilient to process fluctuations.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405212|

The ideal shared match line design with a pre-charge senseamplifieroffersaveryeffectiveCAMstructureby loweringpower usage, increasing speed, and decreasing area overhead. This method is especially advantageous in high-speed scenarios where energy efficiency and performance are essential, like networking devices and AI accelerators. Future developments may concentrate on further minimizing power leakage and improving process scalability for upcoming CAM applications.

## IV. COMPARISON OF THE PROPOSED OPTIMAL MATCH LINE - BASED CAM WITH THE PREVIOUS EXISTING CAM STRUCTURE

| Parameters       | Existing | Proposed |

|------------------|----------|----------|

| Technology       | 130nm    | 130nm    |

|                  |          |          |

| WordLine (V)     | 1.2 V    | 1.2 V    |

| ArraySize        | 4X4      | 4X4      |

| Transistor Count | 176      | 144      |

| Power            | 27.21mw  | 13.16mw  |

| Delay            | 30.32 ns | 19.62 ns |

#### V.CONCLUSION

In the suggested work, a content addressable memory (CAM) system is constructed utilizing transmission gates(TG)togetherwithoptimalmatchlinesensing. The proposed design incorporates a transmission gate (TG) configuration for the CAM cell architecture. The transmission gate comparison circuit enhances the switchingspeedwhileminimizingthevoltagedropacross the output stage. А dual Match-line search analysisapproachisintroducedtolessenMLtransitions per word and enhance density within the comparison units. In contrast to traditional designs, the proposed approachemploys only a singleML dischargeforevery two-bit mismatch. This results in а reduction of ML dynamic power consumption. The proposed CAM structureisdesignedasa4X4array,andmetricssuchas power dissipation and delay at 130nm have been examined.Thefindingsindicatethattheproposeddesign outperforms existing methodologies concerning power and power delay product. In the future, all high- performance computing applications, including DSP, multimedia, implantable systems, and reconfigurable computing, can be developed using Match-line optimized transmission gate (TG)-CAM to achieve improved delay withstand capabilities even amid temperature fluctuations.

#### REFERENCES

- 1. T. V. Mahendra, S. W. Hussain, S. Mishra, and A. Danda pat, "Technique for Low Match-Line Voltage Swing in Content Addressable Memory," 7th International Conference on Smart Computing and Communications(ICSCC),2019,pp.1-5,doi:10.1109/ICSCC.2019.8843590.

- Z.Cai,Z.Wang,K.Zheng,andJ.Cao,"Architecture of a Distributed TCAM Coprocessor for Integrated Longest Prefix Matching, Policy Filtering, and Content Filtering,"IEEETransactionsonComputers,vol.62,no. 3,pp.417-427,March2013,doi:10.1109/TC.2011.255.

- 3. T. Venkata Mahendra, S. Mishra, and A. Danda pat, "Content-Addressable Memory with Self-Controlled High-PerformancePre-charge-Free,"IEEETransactions on Very Large Scale Integration (VLSI) Systems, vol. 25,no.8,pp.2388-2392,Aug.2017,doi:10.1109/TVLSI.2017.2685427.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### **Volume 14, Issue 5, May 2025**

#### |DOI: 10.15680/IJIRSET.2025.1405212|

- 4. D. Nayak, P. K. Rout, S. Sahu, D. P. Acharya, U. Nanda, and D. Tripthy, (2020). "SRAM with a novel indirect read technique that can recycle charge and conduct differential reading for reduced power consumption, enhanced stability, and performance," Microelectronics Journal, 97, 104723.

- G.Qin,S.Ata,I.Oka,andC.Fujiwara, "Methodsfor Effective Bit Selection to Enhance Performance of Packet Classifications on IP Routers," Global Telecommunications Conference, 2002. GLOBECOM '02.IEEE,2002,pp.2350-2354vol.3,doi:10.1109/GLOCOM.2002.1189051.

- S. Mishra, T. V. Mahendra, J. Saikia, and A. Danda pat, "Dynamic TCAM with Low Overhead Featuring a Pipelined Read-Restore Refresh Scheme," IEEE TransactionsonCircuitsandSystemsI:RegularPapers, vol.65,no.5,pp.1591-1601,May2018,doi:10.1109/TCSI.2017.2756662.

- K. Pagiamtzis and A. Sheikholeslami, "Tutorial and survey on content-addressable memory (CAM) circuits andarchitectures,"IEEEJournalofSolid-StateCircuits, 727,March2006,doi:10.1109/JSSC.2005.864128.

- V. M. Telajala, W. H. Sheikh, S. Mishra, and A. Danda pat, "Single Ended Storage Content Addressable Memory with Low Power Split-Control," 2019 IEEE International Symposium on Smart Electronic Systems (iSES)(PreviouslyiNiS),2019,pp.369-372,doi:10.1109/iSES47678.2019.00091.

- V. M. Telajala, W. H. Sheikh, S. Mishra, and A. Danda pat, "Single Ended Storage Content Addressable Memory with Low Power Split-Control," 2019 IEEE International Symposium on Smart Electronic Systems (iSES)(PreviouslyiNiS),2019,pp.369-372,doi:10.1109/iSES47678.2019.00091.

- 10. K. S, K. D, S. M V, and M. Rao, "Implementation and Design of a Low Power Ternary Content AddressableMemory(TCAM),"2020InternationalSoC DesignConference(ISOCC),2020,pp.15-16,doi:10.1109/ISOCC50952.2020.9333092.

- 11. M.A.Foysal, M.Z.Anam, M.S.Islam, I.Tahmid, and K. Mondal, "Ternary content addressable memory (TCAM) performance analysis," 2015 International Conference on Advances in Electrical Engineering (ICAEE), 2015, pp. 105-108, doi:10.1109/ICAEE.2015.7506807.

- 12. V. V. S. Satti and S. Sri adibhatla, "Design of EfficientCAMcellsforreducedpoweranddelay,"2017 International Conference on Microelectronic Devices, CircuitsandSystems(ICMDCS),2017,pp.1-5,doi:10.1109/ICMDCS.2017.8211585.

- 13. P. Beckett and S. C. Goldstein, "Area reduction impacts on power in nanoscale CMOS," 2005 IEEE InternationalSymposiumon Circuitsand Systems, 2005, pp.2329-2332vol.3, doi:10.1109/ISCAS.2005.1465091.

- R.LorenzoandS.Chaudhary,"CMOSlogiccircuits with low leakage and minimum energy use," 2015 International Conference on Electronic Design, Computer Networks and Automated Verification (EDCAV),2015,pp.44-47,doi:10.1109/EDCAV.2015. 7060536.

- 15. A. Yalla, and U. Nanda, "A strategy for low power applications: Quasi FGMOS 6T SRAM cell design," International Journal of Nanoscience (2019).

- 16. R.LorenzoandR.Paily,"Forenhancedstabilityand less power: Single bit-line 11T SRAM cell," IET Computers and Digital Techniques, vol. 14, no. 3, pp. 114-121, May 2020.

- 17. R. Lorenzo and R. Paily, "Half-selection disturbance free 8T low leakage SRAM cell," International Journal of Circuit Theory and Applications (Wiley), vol. 50, no. 5, pp. 1557-1575, Feb. 2022, doi: https://doi.org/10.1002/cta.3232.

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com