# International Journal of Innovative Research in Science Engineering and Technology (IJIRSET)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

### **Impact Factor: 8.699**

## Volume 14, Issue 5, May 2025

⊕ www.ijirset.com ⊠ ijirset@gmail.com 🖄 +91-9940572462 🕓 +91 63819 07438

International Journal of Innovative Research of Science, Engineering and Technology (IJIRSET)

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405022|

# Full Adder Design using 11T and 10T Transistor Techniques

#### Prof. Hari Krishna Moorthy, Thirisha. S, Tharun Kiruthik S.B, Syed Tanzeel

Department of Electronics and Communication Engineering, Jain University Global Campus, Bengaluru, India

**ABSTRACT:** In this paper, we introduce low-power and area-efficient 11T and 10T CMOS full adder circuits. These circuits are simulated with industry-standard EDA tools to compare power, delay, and transistor count performance. Our results show that these designs significantly outperform traditional 28T CMOS enhancers based on power and transistor minimization and can be applied to low-power applications such as mobile and embedded systems.

KEYWORDS: Full Adder, Low Power, 10T, 11T, CMOS, VLSI, Power Delay Product (PDP), Area Optimization

#### I. INTRODUCTION

The full adder serves as a core element in many digital and arithmetic logic systems. Due to high need for powersensitive and portable systems, the minimization of power while not degrading performance has emerged as an important theme in VLSI design. The 28-transistor-based conventional full adders dissipate more power and require larger areas. In this paper, we present 11T and 10T full adder topologies with a lower transistor count without degrading the performance.

#### **II. RELATED WORK**

Different low-transistor-count full adders such as 16T, 14T, and 12T have been investigated in literature. Transmission Gate Logic (TGL) Pass Transistor Logic (PTL) and Gate Diffusion Input (GDI) are some of the popular methodologies. But these structures tend to have voltage degradation or poor driving capability. Our 11T and 10T structures resolve these drawbacks with better power-performance trade-offs.

#### III. PROPOSED 11T AND 10T FULL ADDER CIRCUITS

The full adder outputs Sum and Carry, defined by: Sum = A XOR B XOR Cin Cout = AB + BCin + ACin

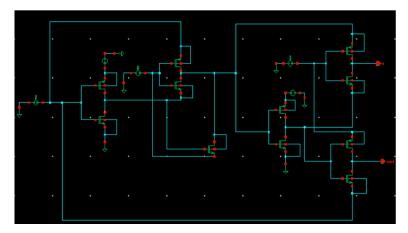

3.1. 11T Full Adder The 11T design implements XOR and multiplexer logic using optimized pass transistor combinations.

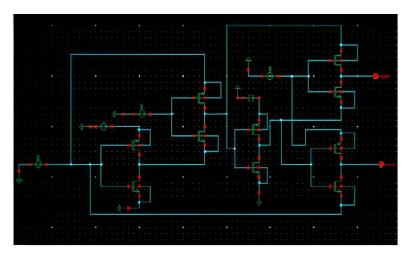

3.2. 10T Full Adder The 10T design further reduces one transistor by simplifying the carry generation logic.

International Journal of Innovative Research of Science, Engineering and Technology (IJIRSET)

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

|DOI: 10.15680/IJIRSET.2025.1405022|

Figure 1: 11T Full Adder Schematic

Figure 2: 10T Full Adder Schematic

#### **IV. SIMULATION SETUP**

Simulation was performed using Cadence Virtuoso with 180nm technology. Supply voltage was 1.8V, and input patterns were presented at 100MHz. Performance characteristics tested are: Power Consumption, Propagation Delay, and Power Delay Product (PDP).

#### V. RESULTS AND DISCUSSION

The results show significant savings in power and area. Although there is a slight delay penalty in the 10T and 11T designs, their PDP is notably improved, indicating energy efficiency.

International Journal of Innovative Research of Science, Engineering and Technology (IJIRSET)

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

#### Volume 14, Issue 5, May 2025

#### |DOI: 10.15680/IJIRSET.2025.1405022|

| Design    | Number         | <b>Operating Powe</b> | Latency (ps) | PDP Value (fJ) |

|-----------|----------------|-----------------------|--------------|----------------|

| C         | of Transistors | ( <u>uW</u> )         |              |                |

| 28T CMOS  | -28            | 8.12                  |              | -0.725         |

| 201 01100 | 20             |                       | 07.0         | 0.720          |

| 11T       | 11             | 2.95                  | 121.2        | 0.357          |

|           |                |                       |              |                |

| 10T       | 10             | 2.73                  | 128.5        | 0.351          |

|           |                |                       |              |                |

#### VI. CONCLUSION

We have suggested two low-power efficient full adder designs with 11 and 10 transistors optimized for low-power VLSI circuits. The designs possess is a consideration between performance and Energy usage and are superior to conventional Architectures based on PDP and transistor count. Extensions of this method to multi-bit adders and incorporation with ALU structures remain as future work.

#### REFERENCES

- 1. Shivani V., et al., "Design of Low Power and High-Speed 10T Full Adder Using GDI Technique," Microelectronics Journal, vol. 88, pp. 80–90, 2019.

- P. Balasubramanian and C. H. Chang, "A Low Power and High Speed 11T Full Adder Cell Using Pass-Transistor Logic," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 4, pp. 1452– 1461, Apr. 2017.

- 3. **T. Srikanth and B. Venkateswarlu**, "Design and Implementation of Area Efficient Full Adder using 10T Technique," Procedia Computer Science, vol. 143, pp. 302–309, 2018.

- 4. **R. Zimmermann and W. Fichtner**, "Low-power Logic Styles: CMOS versus Pass-Transistor Logic," IEEE Journal of Solid-State Circuits, vol. 32, no. 7, pp. 1079–1090, Jul.

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com