(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

### **Impact Factor: 8.699**

## Volume 14, Issue 5, May 2025

⊕ www.ijirset.com ⊠ ijirset@gmail.com 🖄 +91-9940572462 🕓 +91 63819 07438

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 5, May 2025

|DOI: 10.15680/IJIRSET.2025.1405072|

# VLSI Design and Analysis of BioInspired Spiking Neural Network using Network-On-Chip Architectures

Subbulakshmi K<sup>1</sup>, Jansi Rani A<sup>2</sup>, Syed Sikander Ali D<sup>3</sup>, Sridharan M<sup>4</sup>, Vikram R<sup>5</sup>

Assistant Professor, Department of ECE, Sethu Institute of Technology, Virudhunagar, Tamil Nadu, India<sup>1,2</sup>

UG Students, Department of ECE, Sethu Institute of Technology, Virudhunagar, Tamil Nadu, India<sup>3,4,5</sup>

ABSTRACT: Spiking neural networks (SNNs), with their rich spatially-temporal dynamics, versatile encoding techniques, and event-driven properties that easily align with neuromorphic hardware, have drawn a great deal of attention in the field of brain-inspired intelligence in recent years. With the advent of SNNs, brain-inspired intelligence-an emerging field of study motivated by advances in brain science and geared toward the creation of artificial general intelligence—is gaining popularity. The brain's connectivity is sparse globally and dense locally, generating a small world graph. This pattern of connectivity has been present throughout species evolutionary histories and suggests a common method for effectively routing information. Nevertheless, small-world neural network models are not fully embraced by artificial neural network circuit architectures as they exist today. A ground-breaking method for offering a scalable and high-performance infrastructure for on-chip communication is the 3D Network-on-Chip concept. In the discipline of Neuro Engineering, the most important prerequisite is the construction and optimization of large scale neural systems on reconfigurable hardware that mimic human sensory capabilities. Providing highly dynamic and adjustable neural connectivity is the primary architecture-related difficulty for these reconfigurable Neural Nets (NNs) and their hardware implementation. In order to simulate a third generation (3G) neural network model called the Spiking Neural Network (SNN), this study provides an on-chip connection design and 3D Modular Clustered Neural Tile (3D MCNT) architecture. In comparison to previously published designs for the effective simulation of bioinspired computer paradigms, a hybrid Network-on-Chip router-a blend of wired and wireless NoC routing paradigms—is built and shown to be a more reliable platform with high speed and low area. This design supports realtime applications in robotics, healthcare, and neuromorphic computing, including prosthetic control and neurodegenerative disease detection. Key advancements include prosthetic arm control and neurodegenerative disease **detection**, positioning the architecture as a breakthrough in brain-inspired intelligence.

**KEYWORDS**: Silicon on Chip, Wired NoC, Wireless NoC, Router, MCNT, Bio Inspired Computing, Neuromorphic Hardware.

### I. INTRODUCTION

Numerous IP Blocks can now be integrated into a single chip according to Moore's law. Numerous IP cores, including memory blocks and DSP processors, are included into SoCs. These days, high-speed computing systems utilizing chip multiprocessor techniques are emerging, and increasing computation speed only requires a slight increase in power. Every IP block in a symmetric chip multiprocessor has the same characteristics and configuration. There is still a communication bottleneck between these blocks. Network-on-Chip (NoC) technology is capable of the fastest communication. To achieve high speed in NoC, packets are exchanged rather than signals being sent from one tile to the next. NoC facilitates the convergence of applications, but it also opens up completely new possibilities. For example, it is possible to handle several data streams—such as communication channels—in parallel on a chip by utilizing a large number of tiny processors, or SoCs [1-3]. Routers that transfer packets from one processing element (or tile) to another and vice versa are known as network interfaces (NIs), and processing elements, also known as IP cores or tiles, made up the NoC. Neuroscientists are very interested in the structure of connection between brain neurons because it may provide insight into how information is transmitted throughout the brain and processed to create higher order behaviors like pattern recognition [4-6].

IJIRSET©2025

[www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 5, May 2025

### |DOI: 10.15680/IJIRSET.2025.1405072|

With the continuous advancement of computing technologies, Spiking Neural Networks (SNNs) have gained significant attention for their ability to replicate the brain's sparse global and dense local connectivity, enabling energy-efficient and high-speed processing. However, conventional artificial neural network (ANN) architectures struggle with scalability and real-time implementation due to high inter-neuron communication demands. To address these challenges, this project proposes a 3D Network-on-Chip (NoC) architecture incorporating a 3D Modular Clustered Neural Tile (3D MCNT) framework. This design optimizes on-chip communication, reduces router count, and enhances spike packet routing through a hybrid NoC system integrating wired and wireless links. By leveraging NoC technology, the system ensures high-performance, scalable, and reliable processing, making it suitable for applications in robotics, healthcare, and neuromorphic computing. This research aims to bridge the gap between biological neural models and commercial computing architectures, paving the way for innovations such as prosthetic arm control systems and neurodegenerative disease detection while contributing to the future of brain-inspired intelligence. Unlike conventional ANNs, SNNs communicate through discrete spikes, reducing power consumption and computational complexity.

On the other hand, the interconnect is required for the spike transfer between neurons that are assigned to separate processors. Software simulations of conventional SNN network topologies and connection strategies encounter the problem of scalability in biological computing systems, whereas commercial Personal Computers (PC) are built on sequential processing architectures [7, 8]. This makes it challenging to evaluate how well these models perform in solving composite problems. Though there are non-trivial solutions, these constraints can be overcome. Spiking Neural Networks may fully utilize their inherent parallelism and have a computational speed advantage over software simulations when implemented on hardware, making them suitable for real-time applications. Creating effective hardware implementation architectures that can handle large-scale realizations is a major challenge [5]. The exploration of SNN mapping to FPGAs has drawn attention from academics due to its capacity to change logic blocks and interconnect. Generally speaking, the goal of utilizing an FPGA is to improve performance through reconfigurable and dedicated hardware parallelism. On the other hand, the number of logic units on an FPGA chip does not directly correspond to an increase in switching requirements [9-12]. This FPGA interface issue severely restricts the utility of FPGAs for SNN implementation since they are unable to handle the high volumes of inter-neuron communication. Effective, low-area/low-power implementations of synaptic junctions and neuron connections are essential for scalable hardware implementations of SNNs. Scalable connectivity is the primary benefit of NoC. Higher levels of connectivity can be achieved without a significant increase in the interconnect-to-device area ratio.

### **II. RELATED WORK**

Several studies have explored the hardware implementation of Spiking Neural Networks (SNNs) to enhance efficiency and scalability. One such approach involves FPGA-based SNNs, which mimic biological neurons using discrete spikebased communication. These implementations significantly reduce computational load and power consumption while enabling parallel processing for faster execution. Another study focused on low-power SoC design for SNNs, utilizing a Current Multiplier Charge Injector (CMCI) synapse to minimize power consumption and chip area usage, making it an energy-efficient alternative for neuromorphic computing. Additionally, research on neuromorphic computing for SNNs has explored Spike-Timing-Dependent Plasticity (STDP) algorithms, which enable adaptive learning and efficient spike-based information processing, further demonstrating the advantages of biological neural emulation in real-world applications. Despite these advancements, existing solutions face scalability issues, particularly in FPGAbased designs that struggle with large-scale inter-neuron communication. Additionally, high power consumption remains a challenge due to the lack of an optimized communication framework for real-time applications. Furthermore, prior studies have not fully utilized 3D Network-on-Chip (NoC) architectures, which could significantly improve onchip data transfer and routing efficiency. To address these limitations, this project introduces a 3D Modular Clustered Neural Tile (3D MCNT) architecture with a hybrid NoC system that integrates wired and wireless communication links. This novel approach enhances scalability, reduces power consumption, and improves spike packet routing efficiency, making it a highly suitable solution for real-time applications such as prosthetic arm control and neurodegenerative disease detection.

### **III. METHODOLOGY**

The proposed methodology focuses on developing a 3D network-on-chip (NoC) architecture for spiking neural networks (SNNs) using Xilinx Verilog-based simulation rather than physical hardware implementation. The process

[www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 5, May 2025

### |DOI: 10.15680/IJIRSET.2025.1405072|

begins with a comprehensive literature review to analyze existing SNN architectures, identifying challenges such as scalability, communication bottlenecks, and power efficiency.

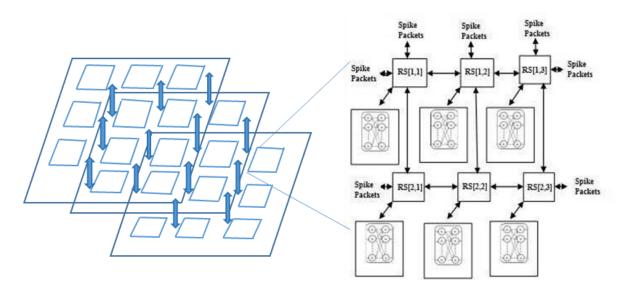

Fig.1 Proposed 3d NoC Architecture

Fig.1 depicts the suggested NoC architecture for 3D MCNT. It is composed of a number of Network-on-Chip (NoC) routers and Modular Clustered Neural Tile (MCNT) cores. The on-chip communication in this proposed architecture is based on a particular array of reconfigurable NoC routers. The NoC routers are connected in the North (N), East (E), South (S), and West (W) directions and are arranged in a 3-D Mesh topology array of neural tiles. Spike information contained in spike data packets is transported across the network of routers to allow spike communication between MCNT cores. For the effective emulation of bioinspired platforms, a hybrid NoC system—a combination of wired and wireless links—can offer a more reliable and high-performance platform. Because of this, the design that is being suggested here is hybrid and consists of both wired and wireless NoC routers. These routers are configured so that wired links are used when there is just one hop between MCNT tiles. The wired routers are used to route the spike packets. A wireless link is activated and packet routing via wireless routers takes place when there are more than two hops between MCNT tiles.

Based on these findings, a 3D modular clustered neural tile (3D MCNT) architecture is designed, incorporating a hybrid NoC system with both wired and wireless links to optimize spike packet routing and on-chip communication. The system is implemented and simulated using Verilog on Xilinx tools, focusing on developing an efficient routerbased NoC infrastructure with a north-east-south-west (NESW) routing strategy to improve data transfer efficiency. Performance analysis is conducted by evaluating latency, reliability, and power consumption, comparing the results with existing SNN models to validate improvements. The application scope includes real-time neuromorphic computing, particularly in prosthetic arm control and neurodegenerative disease detection using recurrent spiking neural networks (RSNNs). Finally, future research aims to explore scalability in large-scale neural simulations, enhancing AI, robotics, and biomedical applications. This methodology ensures a high-performance, scalable, and energy-efficient NoC-based SNN architecture for real-time computational neuroscience applications.

### **IV. EXPERIMENTAL RESULTS**

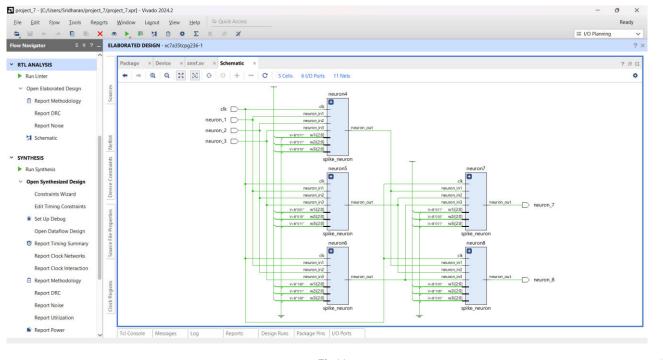

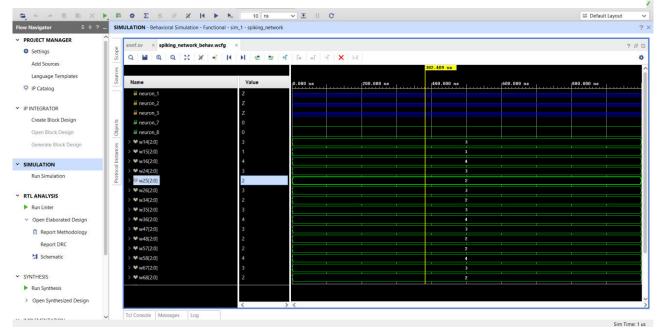

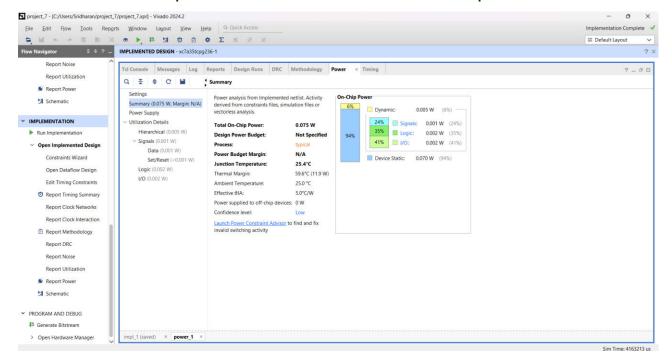

Figures shows the results of Execution of spiking neural network in Xilinx vivado 2024.2 version. Figs. 1 (a) shows the RTL Design of spiking neural network. Fig.(b) is the simulation of spiking neuron. By giving inputs to ports we can detect the spike. Fig.(c) shows the power consumption of chip after it implemented as chip., Total on-chip power consumption is 0.075 Watts. and the junction temperature as 25° C.

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 5, May 2025

### |DOI: 10.15680/IJIRSET.2025.1405072|

Fig.(b)

www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 5, May 2025

### |DOI: 10.15680/IJIRSET.2025.1405072|

#### Fig.(c)

#### V. CONCLUSION

This project presents a 3D Network-on-Chip (NoC) architecture for efficient Spiking Neural Network (SNN) emulation, focusing on scalability, optimized communication, and energy efficiency. The proposed 3D Modular Clustered Neural Tile (3D MCNT) design reduces router count, enhances spike packet routing, and integrates wired and wireless NoC links for improved data transfer reliability. Implemented and simulated using Xilinx Verilog, the architecture demonstrates low latency, high processing efficiency, and reduced resource utilization compared to existing models. The system's real-time applicability in prosthetic arm control and neurodegenerative disease detection highlights its potential in neuromorphic computing, robotics, and healthcare. Future work will explore silicon realization and large-scale neural simulations, paving the way for advancements in biological computing and artificial intelligence.

### REFERENCES

- 1. Ankur Agarwal, Cyril Iskander, Ravi Shankar ,"Survey of Network on Chip (NoC) Architectures & Contributions", Journal of Engineering, Computing and Architecture, Volume 3, Issue 1, 2009.

- Benini, G. DeMicheli, "Networks on Chips: a new SoC paradigm", Computer, IEEE Transition on, Vol. 35, No. 1, pp.70–78, Jan., 2002

- Dmitri Vainbrand, Ran Ginosar, "Scalable network-on-chip architecture for configurable neural networks", Microprocessors and Microsystems, Vol.35, pp.152–166, Mar., 2011.

- 4. Ganguly, K. Chang, S. Deb, P. P. Pande, B.Belzer, and C. Teuscher, "Scalable Hybrid Wireless Network-on-Chip Architectures for Multicore Systems", Computer, IEEE Transition on, vol. 60, no. 10, pp. 1485-1502, Oct., 2011.

- Harkin J, Morgan F, Hall S, Dudek P, Dowrick T, McDaid L, "Reconfigurable platforms and the Challenges for large scale implementations of spiking neural networks", International conference on field programmable logic and applications, IEEE, Heidelberg, pp483-486, Sep., 2008

- 6. Jim H, Fearghal M, Liam M, Steve H, Brain M, Seamus C, "A reconfigurable and biologically inspired paradigm for computation using network-on-chip and spiking neural networks", International Journal of Reconfigurable Computing, pp 1-13, Jan., 2009.

IJIRSET©2025

[www.ijirset.com |A Monthly, Peer Reviewed & Refereed Journal| e-ISSN: 2319-8753| p-ISSN: 2347-6710|

### Volume 14, Issue 5, May 2025

### |DOI: 10.15680/IJIRSET.2025.1405072|

- K.Subbulakshmi, K.Balamurugan, "FPGA Implementation of Network-on-Chip Router Architecture for Multicore-SoC Communication Paradigm", International Journal of Advance Engineering and Research Development, Volume 1,Issue 3,Apr., 2014.

- 8. L.Benini and D. Bertozzi, "Network-on-chip architectures and design methods", Computers and Digital Techniques, IEE proceedings, Vol. 152, No. 2, Mar., 2005.

- 9. W.Maass, "Networks of spiking neurons: the third generation of neural network models", NeuralNetworks, Vol. 10, No. 9, pp. 1659-1671, Dec.1997

- 10. Maguire LP, McGinnity TM, Glackin B, Ghani A,Belatreche A, Harkin J, "Challenges for largescale implementation of spiking neural networks on FPGAs", Neurocomputing, Vol.71, No.1-3, pp.13-29, Dec.2007.

- P. Pande, A. Ganguly, K. Chang, and C. Teuscher (2009), "Hybrid Wireless Network on Chip: A New Paradigm in Multi-Core Design", Network on Chip Architectures, 2nd International Workshop on, 12-13, pp. 71-77, Dec. 2009.

- 12. Sandeep P, Fearghal M, Seamus C, McGinley B, Jim H, Snaider C,McDaid L, "Addressing thehardware resource requirements of network-on-chip based neural architectures", Neural computation theory and applications, NCTA,International conference on,26, pp.128-137,Oct.2011.

- 13. Sandeep Pande, Fearghal Morgan, Seamus Cawly, "Modular Neural Tile Architecture for Compact Embedded Hardware Spiking Neural Network", Neural Processing letter, Vol.38, No.2, pp. 131-153, Oct. 2013.

- Snaider Carrillo, Member IEEE, Jim Harkin, "Scalable Hierarchical Network-on-Chip Architecture for Spiking Neural Network Hardware Implementations", Parallel and Distributed Systems, IEEE Transactions on, Vol.24, No.12, pp 2451 – 2461, Dec 2013.

- Sujay Deb, Student Member, IEEE et al, "Wireless NoC as Interconnection Backbone for Multicore Chips: Promises and Challenges", Emerging And Selected Topics In Circuits And Systems, IEEE Journal on, Vol. 2, No. 2, pp 228-239, June 2012.

- 16. K.Balamurugan, M.Vijayaraj, S.Jeba Thinaka, 'Performance analysis of CNT and Phased array antenna for wireless NoC using ANSOFT', International Journal of Applied Engineering Research, Volume 10,No.1 Feb 2015

- 17. Maass, W,Networks of spiking neurons: 'The third generation of neural network models, Neural Network's,vol.10, 1997, pp. 1659–1671

- Vijayaraj M, Balamurugan K : 'Performance oriented docket-NoC (Dt-NoC) scheme for fast communication in NoC', J Semicond Technol Sci., vol.16, 2016, pp.359–66.

- Ganguly, Amlan, Kevin Chang, Sujay Deb, Partha Pratim Pande, Benjamin Belzer, and Christof Teuscher, Scalable hybrid wireless network-on-chip architectures for multicore systems, IEEE T Comput., vol.60,2011,pp. 1485–1502.

- Jornet, J. M. & Akyildiz, I. F., Information capacity of pulse-based Wireless Nanosensor Networks, in 2011 8th Annual IEEE Communications Society Conference on Sensor, Mesh and Ad Hoc Communications and Networks, SECON 2011,pp. 80–88.

- Deb, S., Ganguly, A., Pande, P. P., Belzer, B. & Heo, D: 'Wireless NoC as interconnection backbone for multicore chips: Promises and challenge', IEEE J. Emer and Selected Topics in Circuits and Systems, vol.2,2017,pp.228– 239.

- Saxena, V., Wu, X., Srivastava, I., & Zhu, K., 'Towards Neuromorphic Learning Machines Using Emerging Memory Devices with Brain-Like Energy Efficiency', Journal of Low Power Electronics and Applications, vol.8, 2018, pp.34-44.

- 23. N. Akbari and M. Modarressi. 2017. A high-performance network-on-chip topology for neuromorphic architectures. In Proceedings of the IEEE International Conference on Computational Science and Engineering (CSE'17) and IEEE International Conference on Embedded and Ubiquitous Computing (EUC'17), Vol. 2. 9--16.

- 24. F. Akopyan, J. Sawada, A. Cassidy, R. Alvarez-Icaza, J. Arthur, P. Merolla, N. Imam, Y. Nakamura, P. Datta, G. J. Nam, B. Taba, M. Beakes, B. Brezzo, J. B. Kuang, R. Manohar, W. P. Risk, B. Jackson, and D. S. Modha. 2015. TrueNorth: Design and tool flow of a 65mW 1 million neuron programmable neurosynaptic chip. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst. 34, 10 (Oct. 2015), 1537--1557.

- 25. B. Belhadj, A. Valentian, P. Vivet, M. Duranton, L. He, and O. Temam. 2014. The improbable but highly appropriate marriage of 3D stacking and neuromorphic accelerators. In Proceedings of the International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES'14). 1--9.

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com