# "Design and Development of Scalable FFT Architecture for Filter Bank De-multiplexing Application"

# MADHUSUDHAN. S<sup>1</sup>, NAGENDRA KUMAR. M<sup>2</sup>

# 4th sem MTech, Signal Processing, S. J. C. I. T, Chickballapur, India<sup>1</sup>

Associate Professor , Dept of ECE, S. J. C. I. T, Chickballapur, India<sup>2</sup>

**Abstract:** This paper proposes a high speed FFT implementation based on  $\operatorname{Radix}-2^2$  single path delay feedback pipelined structure which was implemented on an FPGA. The radix-2<sup>2</sup> algorithm is used to decrease the number of non trivial multiplication. The number of multiplication needed for calculating the FFT by this algorithm is same as that of radix-4 but its butterfly structure is equivalent to that of radix-2. The simple radix-2 structure helps in efficient VLSI implementation. The single path delay feedback structure is used for the implementation of the algorithm to make it pipelined, which is a part of the filter bank architecture for satellite application.

**Keywords:** *DFT*,*FFT*,*DIT*,*DIF*,*SDF*,*FPGA*,*VLSI*,

#### I. INTRODUCTION

The Fast Fourier Transform (FFT) is a conventional method for an accelerated computation of the Discrete Fourier Transform (DFT) [1], which has been used in many applications such as spectrum estimation, fast convolution and correlation, signal modulation, etc. Even though FFT Algorithmically improves computational efficiency, additional hardware-based accelerators are used to further accelerate the processing through parallel processing techniques. A variety of architectures have been proposed to increase the speed, reduce the power consumption, etc.

DFT Discrete Fourier Transform is the core for any digital signal process. the most efficient way to compute DFT is by FFT Fast Fourier Transform. Fourier Transform Transforms the time domain signal into frequency domain signal by which the characteristics of the signal can be analyzed. By using MATLAB we can easily find the N-point DFT of the signal, but the use of MATLAB for calculating the DFT in satellite communication (satellite) is impractical because it requires huge memory, cost and computer hardware to process. To overcome the above disadvantage a separate model is needed to be developed. Since the incoming data is unknown with respect to length, bandwidth etc, A FFT model is needed such that it can handle any amount of incoming data, such model is called as scalable FFT model. Further this scalable FFT model is used in filter banks which are used in de-multiplexing application.

# **II. ARCHITECTURE**

**TYPES:-**FFT algorithms may be developed using one of three fundamental techniques

- 1. Number theory.

- 2. Matrix manipulation.

- 3. DFT properties [1].

As FFT is an efficient algorithm to compute the DFT.FFT uses DFT properties symmetry and periodicity properties to reduce number of complex multiplications and additions. Two approaches are used for computationally efficient algorithms for evaluating the DFT.

1. Divide and conquer approach.

2. Linear filtering operation on data.

FFT algorithms are of two types.

1. Decimation in time (DITFFT).

Copyright to IJIRSET

- 2. Decimation in frequency (DIFFFT).

- DIT:-In this input sequence is broken into two smaller sequences at each stage (even and odd).

- DIF:-In this the input data is separated into its first N/2 and last N/2 components instead of even& odd.

The DIT/DIF may use Radix-2, Radix-4, and Radix-8 etc Butterfly structure.

The hardware architecture for scalable FFT can be divided into four classes.

1. Single PE (processing element) architecture (memory based).

- a. Single memory.

- b. Dual memory.

- c. Triple memory.

- d. Cached memory.

- 2. Pipe line architecture [2].

- a. R2MDC(Radix-2Multipathdelay commutator).

- b. R2SDF (Radix-2 Single delay feedback).

- c. R4SDF (Radix-4Single delay feedback).

- d.R4MDC(Radix-4Multipath delay commutator).

- e.R2<sup>2</sup>SDF (Radix-2<sup>2</sup> Single delay feedback).

- 3. Array based.

- 4. Column based.

The discrete Fourier transform X(k),k=0,1,...N-1 of the sequence x(n),n=0,1,...N-1 is defined as:

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{kn}$$

Where N is the transform size  $W_N = e^{-j2\pi/n}$  and  $j = \sqrt{-1}$ . According to the decomposition method of [7] that done by substituting with

$$\mathbf{n} = \left(\frac{N}{2}\mathbf{n}_{1} + \frac{N}{4}\mathbf{n}_{2} + \mathbf{n}_{3}\right)_{\mathrm{N}, k} = (k_{1} + 2k_{2} + 4k_{3})_{\mathrm{N}} X(k_{1} + 2k_{2} + 4k_{3}) = \sum_{n_{3}=0}^{\frac{N}{4}-1} \left[H(k_{1}, k_{2}, n_{3})W_{N}^{n_{3}(k_{1}+2k_{2})}\right] W_{\frac{N}{4}}^{n_{3}+k_{3}}$$

Where  $H(k_1, k_2, n_3) = [x(n_3) + (-1)^{k_1} \cdot x(n_3 + \frac{N}{2})] + (-j)^{(k_1 + 2k_2)} [x(n_3 + \frac{N}{2}) + (-1)^{k_1} \cdot x(n_3 + \frac{3N}{4})].$

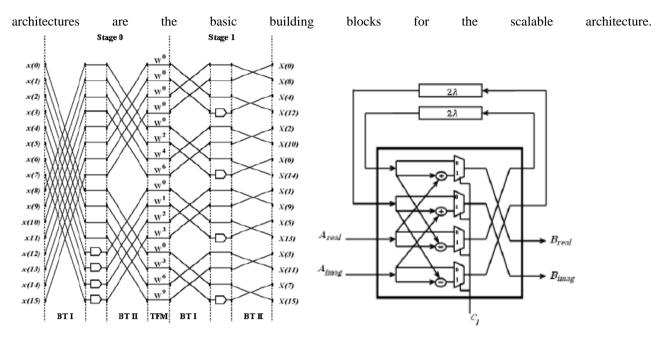

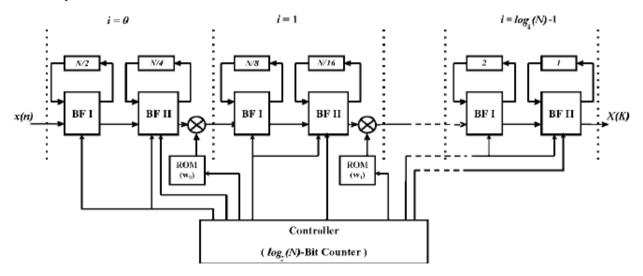

after this simplification, we have a set of four DFT equations of length N/4. The proposed system uses DFT properties, Divide and conquer approach[1], Decimation in frequency(DIFFFT) ,Pipe line architecture,  $R2^2SDF[3]$  which utilizes the delay elements more efficiently by sharing the same storage elements between the butterfly outputs and inputs. A single data stream goes through the multiplier in every stage. This architecture has the same number of butterfly units and multipliers as those in R2MDC and only N-1 delay elements,  $\log_4 N$ -1 Complex multipliers [1] and  $\log_4 N$  butterfly units. Figure (1) shows the DIF FFT butterfly structure using the decomposition formula from 16 to 8 and then 8 to 4 and 4 to 2 point DFT. And construction of two architecture is made using the decomposition formula. These

Fig(1):DIF FFT butterfly for N=16 withTWM

Fig(2)BF I structure.

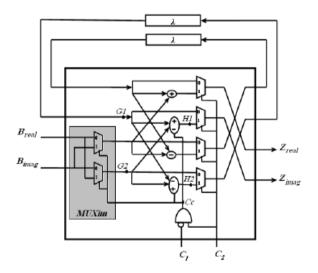

The A input comes from the previous component, TFM. The B output fed to the next component, normally BFII. In

first N/2i+1cycles, multiplexors direct the

Fig(3):BF 2 Structure.

Input data to the feedback registers[6] until they are filled (position '0'). On next N/2i+1cycles, the multiplexors select the output of the adders/sub tractors (position "1"), the butterfly computes a 2-point DFT with incoming data and data stored in the feedback Registers.

The detailed structure of BFII is shown in Fig. 3. The B input comes from the previous component, BFI. The Z output fed to the next component, normally TFM.In first N/2 i+2cycles, multiplexors direct the input data to the feedback registers until they are filled (position 0").In next N/2i+2cycles[4], the multiplexors select the output of the adders/subtractors (position 1"), the butterfly computes a 2-point DFT with incoming data and the data stored in the feedback registers.The multiplication by -j involves real-imaginary swapping and sign inversion. The real-imaginary swapping is handled by the multiplexors and the sign inversion is handled by switching the adding- delay feedback mechanism provides a solution where the first input to the butterfly is delayed until the second input is presented, after

which element structure: In order to reuse the existing hardware, the delay feedback is [7]. By the time, the data appears again at the input of the butterfly. First-in First-out shift register is used to implement the delay-feedback. done by subtracting operations by mean of MUX. When the calculation can proceed. This computing on the block, it is redirected to a feedback delay line[5] by mean of multiplexers Feedback there is a need for multiplication by -j, all imaginary data are swapped and the adding-subtracting operations are switched. multiplexors switches to position "1", the real- accepting part of the data stream into the butterfly elements, but instead of used. The Control unit:Radix-2 control unit is very simple. A log(N) counter is used to switch the BF between modes. It also used as address to ROMs in order to pick the twiddle factors.

Fig(4) architecture of scalable FFT

#### **III.FILTER BANK ARCHITECTURE**

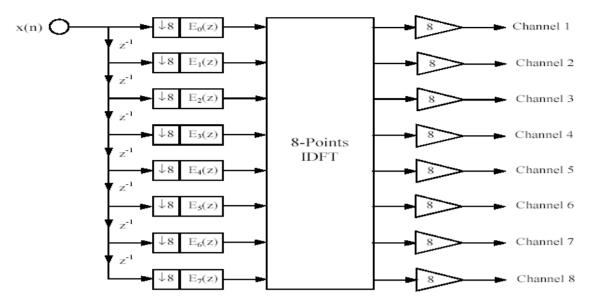

The basic block used in the demultiplexer is a digital filter bank. Starting from the frequency allocation of the incoming signal, the computational complexity of different filter bank architectures has been evaluated and the polyphase filter bank has been chosen. The basic structure of this filter bank is sketched in Fig. 5. The filter input signal (44 MSPS) is decimated by a factor 8 and enters the polyphase components Ei(z). For each component, the input rate is 5.5 MSPS. The same rate is used for the 8-points IDFT. Starting from the 4 real channels -1 guard and 3 data channelswe obtain 8 complex channels, each 5.5 MHz wide. Channels number 2, 3 and 4 (useful channel) are connected to three demodulators, while the others are discarded. The Ei(z) represents the i-th polyphase component of the prototype filter, designed as low pass filter with a cutoff frequency at  $\pi/8$ ; Even if the FIR filter is designed with linear phase, we did not exploit its symmetry in order to reduce its hardware complexity. In fact, due to the particular structure of the polyphase filter bank, a proper sorting of the data samples is necessary and, consequently, a large amount of read/write memory should be used. For the fixed-point implementation of the polyphase component Ei(z), a filter coefficient word-length of 12 bits has been chosen starting from simulation results. The final output is obtained through an 8points IDFT implementing the polyphase decomposition reconstruction. The channels 2, 3 and 4 carry the information corresponding to the 3 data channels. Unfortunately, the signal is complex and shifted in frequency of  $\pi/2$ . If additional processing is not required by the specific application, the unshifted real signal can be obtained by cascading the IDFT with a factor 2 interpolator, a half-band low-pass filter and a  $\pi/2$  frequency shifter. Finally, the real part multiplied by two of the obtained signals is considered as output.

Fig(5): Filter Bank Architecture using FFT model.

#### **IV. RESULT**

The synthesized 1024-point FFT processor on VIRTEX II Pro XC2V30004FG676 can work at a maximum frequency of 43.564 MHZ dissipating 1383mW of power. Its execution speed is 26.26 µsec for calculating 1024-point FFT. The performance was measured using Xilinx Synthesis Tools, which is further used in a filter bank application in order to separate the frequency component.

# V. CONCLUSION

The implemented design gives an easy way to increase the number of points of FFT as well as IFFT by imposing simple modification with the twiddle factor. The design gives the simple and efficient way for the implementation of scalable FFT. Future work includes the development of complete OFDM system and upgrade it to a multiple input multiple outputs (MIMO) system by using high density FPGA device.

| 📰 Wave 🚃        |                  |          |            |          | =        |          |              |          |          |          |                    |       |         |

|-----------------|------------------|----------|------------|----------|----------|----------|--------------|----------|----------|----------|--------------------|-------|---------|

| ] 🗋 • 🚅 🖬 🖏 🚭 📔 | x 🖻 🛍 🖸 🗋   🚳 -  | ₩₩₽      | e  ] 🕸 💥 🗛 | <b>X</b> | @ 🚹 <    | ⊨ 🛶 🕴    | <b>≧†</b> 10 | 0 ps 🌩   | i i      | 1 🕺 🐔    | { <del>}</del> } { | ው ብ ብ | i+ 🖄    |

| 🖪 🍨 🎫   🗗       | ╡┙┓┲             |          | 🗍 🖏 - 🖓 🚱  | 🤹 🛛 🦻    | - 3      | ା ତ୍ର୍   | ۹ 💁          | R   [    |          |          | . <b>.</b> J       | J     |         |

| <b>∕</b> €⊒•    | Msgs             |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 | 0000000000010000 | 00000000 | 00010000   |          |          |          |              | 00000000 | 00000000 |          |                    |       |         |

|                 | 0000000000100000 | 00000000 | 00100000   |          |          |          |              | 00000000 | 00000000 |          |                    |       |         |

| /test12/clk     | 1                |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 | 0000000001010000 | 00000000 | D101000D   |          | 11111111 | 11000001 |              |          | 11111111 | 11001110 |                    |       | 111111  |

|                 | 0000000010100000 | 00000000 | 10100000   |          | 00000000 | 11000001 |              |          | 00000000 | 10111010 |                    |       | 0000000 |

| - •             |                  |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 |                  |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 |                  |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 |                  |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 |                  |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 |                  |          |            |          |          |          |              |          |          |          |                    |       |         |

|                 |                  |          |            |          |          |          |              |          |          |          |                    |       |         |

Fig(6): Modelsim simulation results. Fig(7):Design summary

| FFT_Paper Project Status (04/30/2009 - 05:47:46) |                           |                                         |                                 |  |  |  |  |

|--------------------------------------------------|---------------------------|-----------------------------------------|---------------------------------|--|--|--|--|

| Project File:                                    | FFT_Paper.ise             | Current State:                          | Programming File Generated      |  |  |  |  |

| Module Name:                                     | FFT_Saeed_Core            | • Errors:                               | No Eirora                       |  |  |  |  |

| Target Device:                                   | xc5vsx35t-3lf665          | • Warnings:                             | 29 Warnings (7 new, 0 filtered) |  |  |  |  |

| Product Version:                                 | ISE 10.1 - Foundation     | <ul> <li>Routing Results:</li> </ul>    | All Signals Completely Routed   |  |  |  |  |

| Design Goal:                                     | Balanced                  | <ul> <li>Timing Constraints:</li> </ul> | All Constraints Met             |  |  |  |  |

| Design Strategy:                                 | Xilinx Default (unlocked) | <ul> <li>Final Timing Score:</li> </ul> | (Emina Report)                  |  |  |  |  |

| Device Utilization Summary   |       |           |             |         |  |  |

|------------------------------|-------|-----------|-------------|---------|--|--|

| Slice Logic Utilization      | Used  | Available | Utilization | Note(s) |  |  |

| Number of Slice Registers    | 838   | 21,760    | 3%          |         |  |  |

| Number of Slice LUTs         | 1,058 | 21,760    | 4%          |         |  |  |

| Number used as logic         | 801   | 21,760    | 3%          |         |  |  |

| Number used as Memory        | 255   | 8,320     | 3%          |         |  |  |

| Number of route-thrus        | 7     | 43,520    | 1%          |         |  |  |

| Specific Feature Utilization |       |           |             |         |  |  |

| Number of DSP48Es            | 44    | 192       | 22%         |         |  |  |

# ACKNOWLEDGMENT

The authors would like to thank all the anonymous reviewers for the constructive comments and useful suggestions that led to improvements in the quality, presentation, and organization of this paper. We thank Satish Sharma for his help in completing the paper and advice for the experimental implementation.

#### REFERENCES

J. W. Cooley and J. W. Tukey, "An algorithm for the machine calculation of complex Fourier series," Math. Comput., vol. 19, pp. 297-301, 1965.

B. M. Baas, "A low-power, high-performance, 1024-point FFT processor," IEEE Journal of Solid-State Circuits, vol.34, no. 3, pp. 380–387, March 1999.

[3] Magar, S., S. Shen, G. Luikuo, M. Fleming, and R. Aguilar, "An Application Specific DSP Chip Set for 100 MHz Data Rates," International Conference on Acoustics, Speech, and Signal

Processing, vol. 4, pp. 1989–1992, April 1988. [4] O'Brien, J., J. Mather, and B. Holland, "A 200 MIPS Single-Chip 1K FFT

Processor," IEEE International Solid-State Circuits Conference,

pp. 166–167, 327, 1989.

[5] H. L. Groginsky and G. A. Works, "A pipelined fast Fourier transform," IEEE Transactions on Computers, vol. C-19. pp. 1015- 1019, 1970.

[6] E.H. Wold and A.M. Despain, "Pipeline and parallel-pipeline FFI7 processors for VLSI implementation," IEEE Transactions on Computers, vol. C-33, pp. 414-426, May 1984.

[7] G. Bi and E. V. Jones, "A pipelined FFT processor for word sequential data," IEEE Transactions on Acoustics, Speech, and Signal Processing, vol. 37, pp. 1982-1985, December 1989.

BIOGRAPHY

Madhusudhan S pursuing MTech in Signal Processing from VTU, Belgaum, KARNATAKA, INDIA. Bachelor of engineering in electronics and communication from VTU, Diploma in electronics and communication from BTE,Bangalore,india.and worked as lecturer for 3 academic years in dept of E&C in SNP,BTE, Ramanagara.

NagendraKumar.M,M.Tech,MIE,MIETE,Associate professor,in Dept of E&C,SJCIT, He did master degree in biomedical signal processing form VTU, Belgaum, Karnataka,INDIA Bachelor of engineering in E&E from Mysore University. He has a work experience of 15 year in the field of teaching in different colleges. His area of interest is in biomedical signal processing.